西門子數位工業軟體旗下西門子EDA(Siemens EDA)近日舉辦年度IC設計技術論壇Siemens EDA Forum 2024,活動中,西門子EDA Silicon Systems執行長Mike Ellow揭示軟體定義、硬體賦能(Software defined, Silicon enabled)的關鍵趨勢,並說明該公司如何協助半導體業者應對此項產業趨勢。

Ellow表示,進入由軟體扮演差異化關鍵的時代,硬體晶片成為支援上層軟體實現此任務的關鍵。以汽車應用為例,軟體部分的改動可能會影響整個汽車系統的功率需求,導致硬體平台需要改變電池設計,進而影響引擎、煞車系統的設計,甚至是整個車身設計都可能需要隨之調整。因此,硬體和軟體平行開發,是軟體定義趨勢下的設計重點。為此,西門子聚焦「加速系統設計、先進3D IC整合、製造導向的先進製程節點設計」三大方向,協助業者應對「軟體定義、硬體賦能」關鍵趨勢。

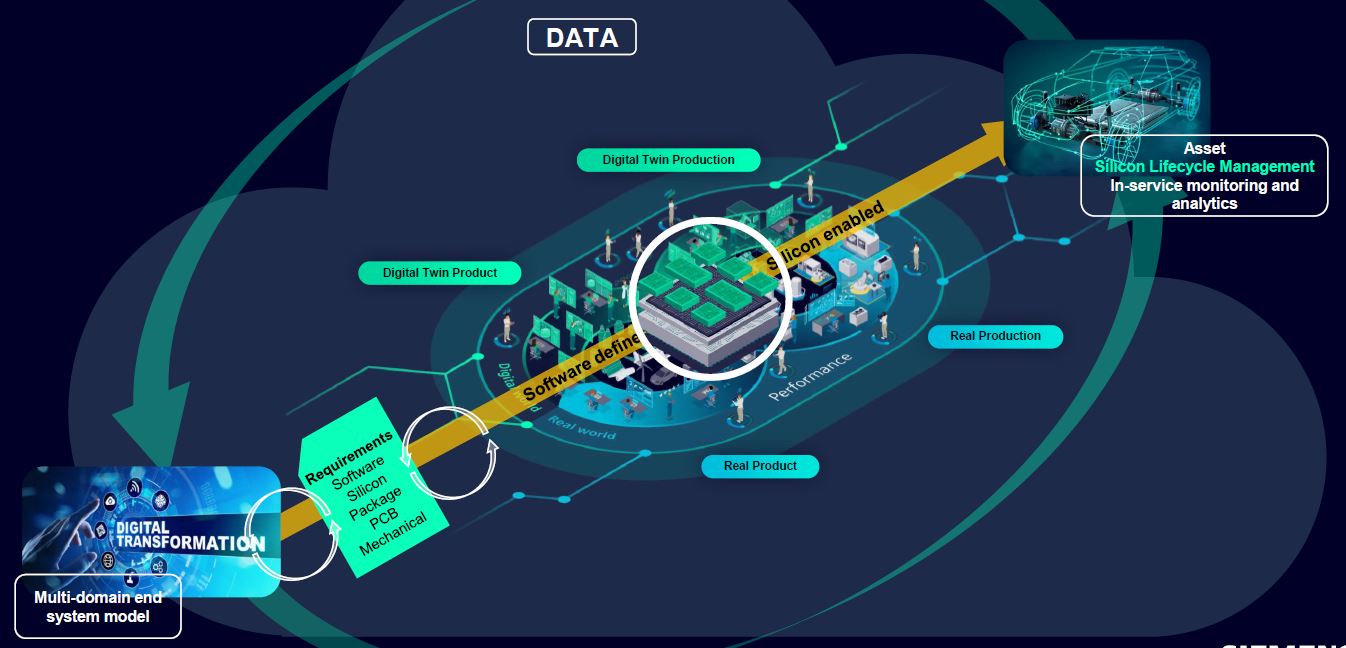

圖1 「軟體定義、硬體賦能」示意圖 (圖片來源:西門子)

圖1 「軟體定義、硬體賦能」示意圖 (圖片來源:西門子)

首先,針對系統設計,西門子Veloce CS解決方案包括協助硬體設計的模擬平台Veloce Strato CS、驗證韌體(FW)/軟體(SW)設計的企業原型驗證平台Veloce Primo CS,以及確保軟體及系統設計的軟體原型驗證平台Veloce proFPGA CS,從硬體到軟體提供驗證方案,以加快系統設計速度。此外,西門子也和業者合作,例如此次活動便展出西門子和AWS及Arm共同推出的汽車系統開發方案,開發者可以透過AWS雲端服務,取得運行於西門子PAVE360數位分身解決方案的Arm技術。

其次,為了滿足創新應用,電晶體將持續縮小,讓設計人員能夠有充足空間完成複雜設計。Ellow指出,先進的異質整合、3D IC、小晶片(Chiplet)是讓硬體平台接近軟體工作負載(Workload)的關鍵技術。有鑑於3D IC除了半導體設計,也將面對多物理挑戰,西門子於6月發表了Calibre 3DThermal產品,旨在應對3D IC的熱相關問題,同時預計於2025年初推出新的產品,幫助解決複雜封裝內部由熱所引起的壓力問題(Thermal-induced Stress)。最後,隨著製程節點演進,EDA工具將繼續扮演重要角色。Ellow表示,西門子EDA工具早已將雲端運算和AI技術融入其中,並致力於持續推動產品的優化。

Ellow也說明,實現「軟體定義、硬體賦能」的過程中,需要最全面的數位分身解決方案。傳統的數位分身主要用於模擬真實產品和製造過程,但隨著數位轉型的推進,業者在開發階段需要優先考慮產品的軟體性能和硬體需求,數位分身的應用角色也因此產生轉變。此外,也能藉由導入矽晶生命週期管理(SLM)的概念,根據資產在運行時的性能表現,進一步改進資產所運行的軟體堆疊。

半導體產業是推動全球變遷的核心,各領域對於以半導體驅動的產品需求正急遽上升,卻同時面臨半導體與系統持續提升的複雜性、成本飛漲和時間壓力,以及人才短缺等多重挑戰。在此趨勢下,Ellow表示,掌握半導體設計的前瞻技術及革新工具,將是企業創新並保持競爭優勢的致勝關鍵。