高速傳輸大量資料的需求,帶動著USB4、HDMI、Thunderbolt及DisplayPort等高頻連接器相繼問世。舉例來說,HDMI 2.1在4個通道上傳送速率可達12Gbps;最新USB4規格讓傳送速率最快可支援40Gbps,Thunderbolt 4埠具有與 Thunderbolt 3同樣的40Gbps頻寬。當訊號速度持續加快時,如何降低雜訊干擾成了重要課題。

現階段線纜連接器必須克服許多高頻訊號問題,包含:衰減(Attenuation)、反射損失(Return Loss)、耦合問題(Crosstalk)、阻抗(Impedance)、走線(Trace)以及走線長度。然而,多少頻率以上稱之為高頻呢?400MHz、1GHz、5GHz還是10GHz呢?

避免反射波長方針

其實高頻的定義可以看成是否會有反射發生:當電磁波在介質(空氣或PCB)上傳遞的時候,如果是連續介質,則不會反射;撞到不連續介質時,若沒有反射發生,則該頻率在這個介質上視為低頻;反之,若產生了反射,則視為高頻。因此,人們常常會聽到一種說法,是「反射與波長有關」。

電磁波的傳遞速率又該如何跟波的運動結合呢?電磁波在空氣或真空中的傳遞速率為光速

............公式1

而電磁波在介質中傳遞的速率(C:光速,

:相對介電係數)為

............公式2

因此可以用此公式簡單的算出電磁波在介質(例如:電路板)上的傳遞速率:頻率(Hz),:波長(m)。

............公式3

此時將波的速率與電磁波的速率公式合併,則可以獲得電磁波在介質上傳遞時的波長:

............公式4

波的反射概念:傳遞路徑的長度小於傳遞波長的,

在此條件下不會發生反射。

簡單來說,為了避免反射的發生,可以讓在PCB上走的電磁波的波長越長越好(λ大於走線長度的4倍)。由以上公式可知,降低頻率與降低PCB的相對介電係數,即可讓波長變長。但實際上因為傳輸需求,資料的傳輸速率無法隨心所欲地將頻率降低,PCB的介質也不可能為1。

另一個方式:縮短走線的長度,讓其長度小於傳遞波長的

。或許這個是個可行的方法,但是當傳輸速率越快又或者高頻元件之間的位置限制,高頻走線可能會有需要5~10cm的長度,縮短走線長度又似乎未必可行。

高頻走線與阻抗設計概念

提到電路板的高頻走線,就會想到走線的阻抗設計(Single-End 50Ω或者Differential 100Ω),而上面的說明卻都沒有提到任何的阻抗問題?上面所提的重點是:在無反射的條件下,不管頻率多高,走線就沒有阻抗問題,亦即不需要做任何阻抗設計。

上一段提到,隨傳輸速率越來越高,縮短走線長度幾乎不可行。因此,拉長走線必然會有反射產生,根據電磁波理論,不產生反射的另一個方法就是:走線阻抗=負載阻抗=內阻抗。

既然是淺談,就避開深奧的理論。以這個概念來看:走線阻抗=負載阻抗=內阻抗,其實也是符合一開始所說的:只要是連續介質就不會有反射發生。也就是說,三者阻抗相同,就等於阻抗從頭到尾是連續的介質。

反射與訊號誤判原理

為什麼不希望反射出現?反射意謂著部分能量沒有被傳遞出去而返回到原處(發射端)。這好像沒什麼,只要把發射端的能量再加大滿足接收端所需即可。但實際上,返回的能量會從原處再反射一次,因為波有疊加的性質,二次反射到接收端的波會與另一個波疊加,因而產生訊號不完整。以數位訊號來看,在接收端原本是1的訊號因此可能變成0,而原本是0的訊號而變成了1,造成了訊號的誤判。

一覽PCB板材挑選攻略

瞭解了反射所產生的訊號問題後,還得挑對PCB,才能著手設計高頻PCB板。較常看到的有兩種PCB板材是FR4與Rogers。

PCB中的其中一項參數,相對介電係數左右了訊號品質的優劣

............公式5

相對介電係數與頻率有關,頻率的高低變化伴隨著相對介電係數也跟著不同。這代表了甚麼呢?由公式可以知道

...............即公式2

以及

............公式4

當相對介電係數隨頻率高低而改變的時候,走在PCB板上的電磁波傳遞速率跟著變化、波長也跟著變化,此即是電磁波理論所提出的色散(Dispersion)現象,這種介質稱為色散介質或色散材料。色散對傳輸有甚麼影響呢?

全面剖析色散問題

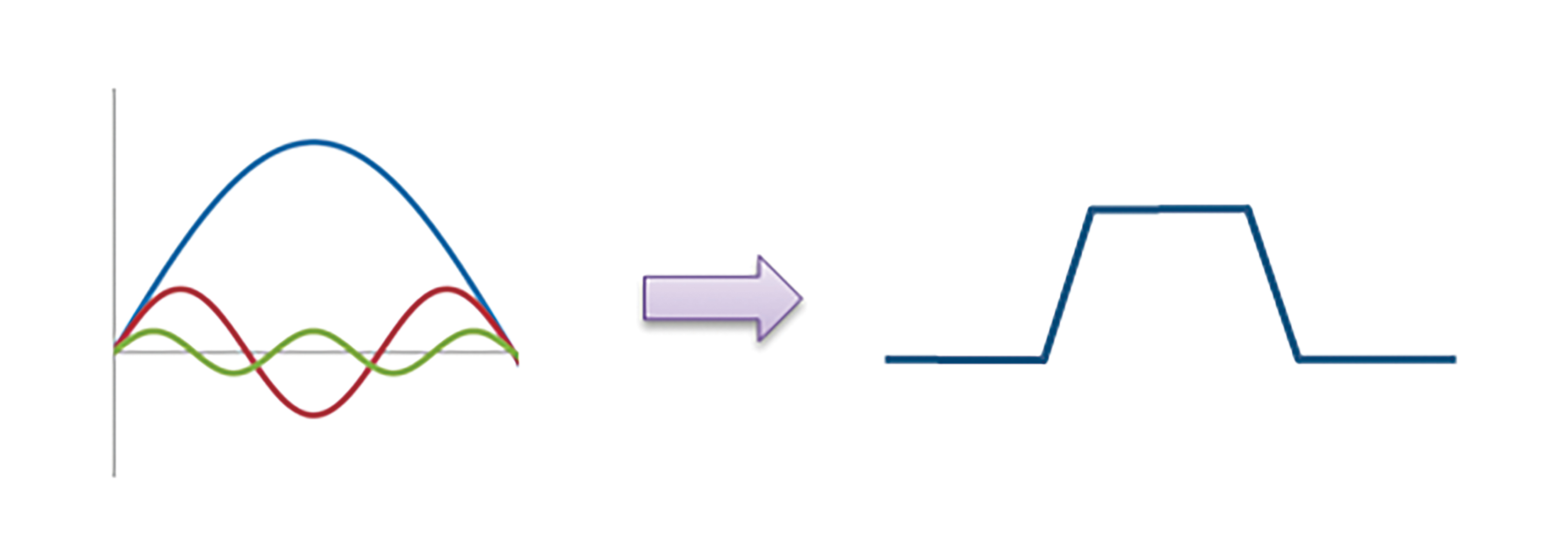

首先,數位訊號是以方波的方式傳遞,也就是0跟1;從單一個的方波來看,是由無數個不同頻率的sin波形成。簡化來看,由一個基本波與兩個奇次諧波疊加而成(圖1)。

圖1 1個基本波與2個奇次諧波加乘數字方波

圖1 1個基本波與2個奇次諧波加乘數字方波

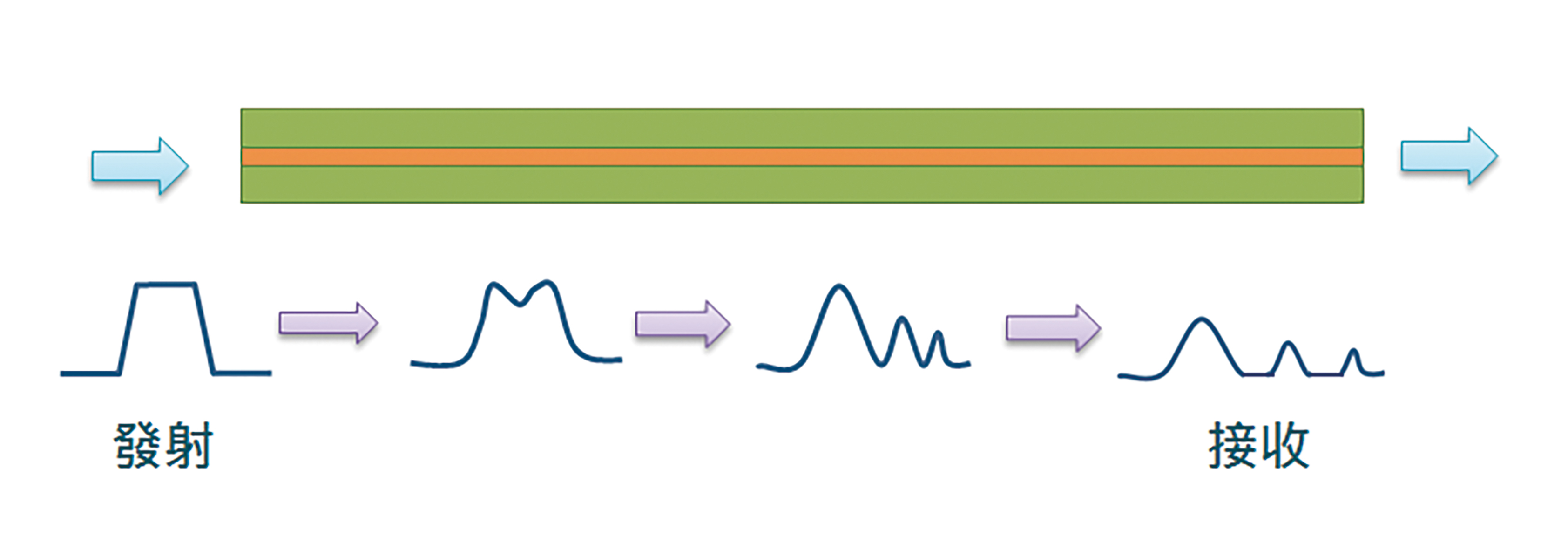

當三種不同頻率波在PCB 走線上傳遞的時候,此時由於相對介電係數跟著不同,因此傳遞速率也跟著不同。也就是理想上,三種頻率速度相同,因此傳出到接收端還是一個完整的方波訊號,但實際上,則不然:三種頻率有各有不同的速率,有的跑得快,有的跑得慢。如果走線拉得夠長,反而會讓方波分解成三種頻率的電磁波,並以不同的時間到達接收端(圖2)。

圖2 Trace與三種頻率

圖2 Trace與三種頻率

相同的High的訊號,卻不同時間到達,振幅也下降,這會造成接收端判斷錯誤造成誤碼。再者,這只是一個High的訊號,如果後面又接連好幾個High跟Low訊號,當後面速度快的超越了前面速度慢的波,此時接收端就更無法判斷資料的正確性。

雖然所設計的走線阻抗(Single-End 50Ω或Differential 100Ω),可以讓走線走很長也不會有反射的發生,但是當遇到色散介質,也就限制了走線長度。因此,即便做了阻抗設計,仍還是希望走線能夠設計多短就多短。

FR4與Rogers材料比較

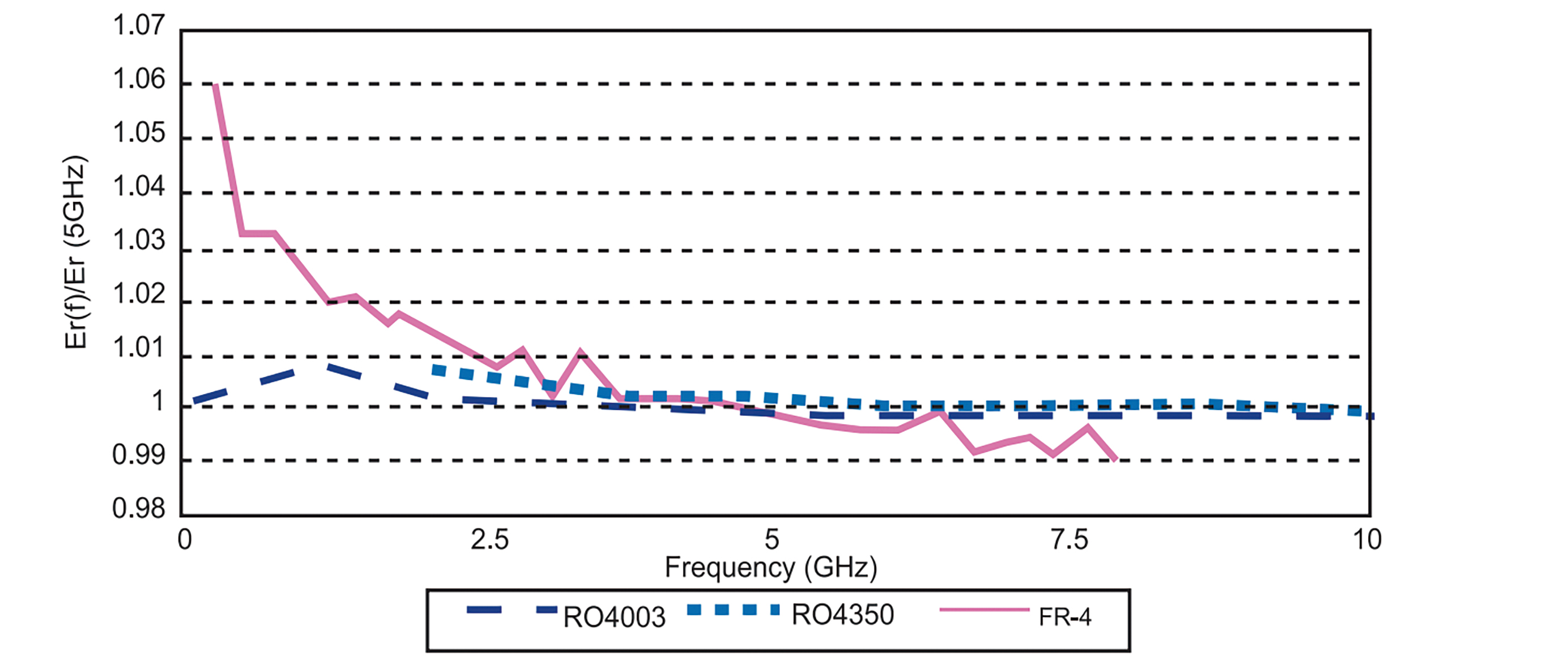

有了相對介電係數與色散現象的概念後,現在來看FR4與Rogers的材料。表1是FR4與Rogers的相對介電係數對頻率的變化。

由圖3可知,FR4的對頻率變化相當劇烈,而Rogers(RO開頭系列)則穩定許多。假設今天使用的傳輸速率的頻率範圍很寬,例如:PRBS31,那麼選擇FR4就必須相當注意色散問題,若要降低色散問題,走線就要盡可能的短。

圖3 FR4與Rogers的相對介電係數對頻率的變化

圖3 FR4與Rogers的相對介電係數對頻率的變化

資料來源:RO4000 Series High Frequency Circuit Materials DATA SHEET

大家或許會說:為了一勞永逸,乾脆直接選擇Rogers板材,問題就解決了!這個答案是正確的,但是因為Rogers板材成本很高,所以必須三思。該怎麼降低成本、訊號品質又該如何維持而能達到通訊的需求?一直是專業的Layout工程師思考要如何取得平衡的點。

最後,為什麼本篇一直沒有提到對走線阻抗的影響呢?實質上是會影響的,但是為了避免分析與說明太過於紊亂,因此把阻抗設計的問題理想化。

PCB板上Layout設計

上文說明了高頻與電路板之間的關係,例如如何挑選合適材料又兼顧成本考慮。接著要來和大家分享高頻PCB板設計的最後一哩路,也就是PCB上面的Layout設計。

PCB上的Layout該怎麼設計呢?大家第一個反應就是「跑模擬」。類比軟體相當便利,可節省不必要的成本與時間,但是模擬參數該如何制訂?預期的模擬結果該如何計算?首先須具備核心概念才能著手進行Layout設計,因此接下來會針對波導結構進行介紹。

大波導結構優/缺點分析

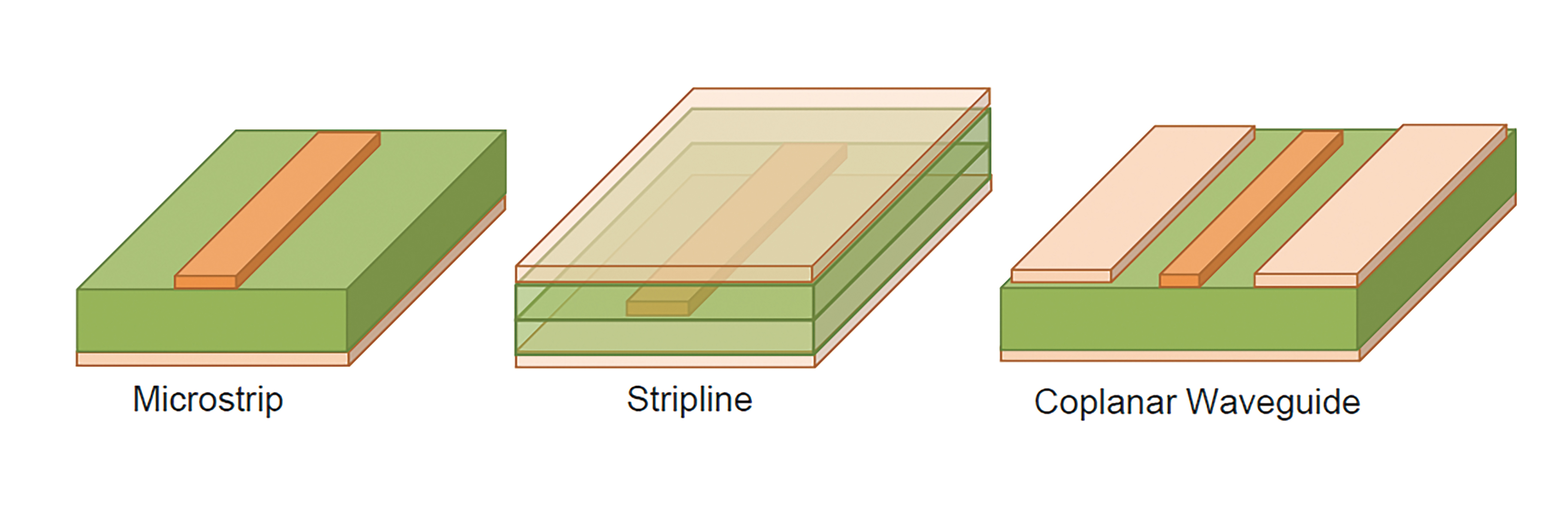

在製作高頻電路板的時候,第一個問題就是波導結構的選擇。本篇介紹三種基本的傳輸結構:Microstrip、Stripline以及共面波導(Coplanar Waveguide)(圖4)。

圖4 三大波導結構

圖4 三大波導結構

.Microstrip

架構最為簡單,設計也簡單。但由於架構簡單,在相同的PCB基板條件下,能夠變化的物理參數不多,例如線寬、線厚與基板厚度。

當頻率越來越高,Microstrip還會有一個問題:走線上方是空氣=1,而下方的基材≠1,此上下場型會有不對稱的情況發生,而使得電磁波場型不對稱,在傳輸上對訊號品質會有影響。

.Stripline

結構較為複雜,上方與下方基材的可以使用接近基板,使得電磁波的場型完整。另外,Stripline高頻走線相互之間不會有遠端串音(FEXT)的影響。

由於走內層,需要依靠灌孔與外部零件連接,因此多餘via段(稱為Stub)會造成訊號衰減與反射問題。減少此問題的方法就是使用背鑽或是盲孔,但這又會導致成本上升(圖5)。

圖5 改善Stub方法

圖5 改善Stub方法

.Coplanar Waveguide

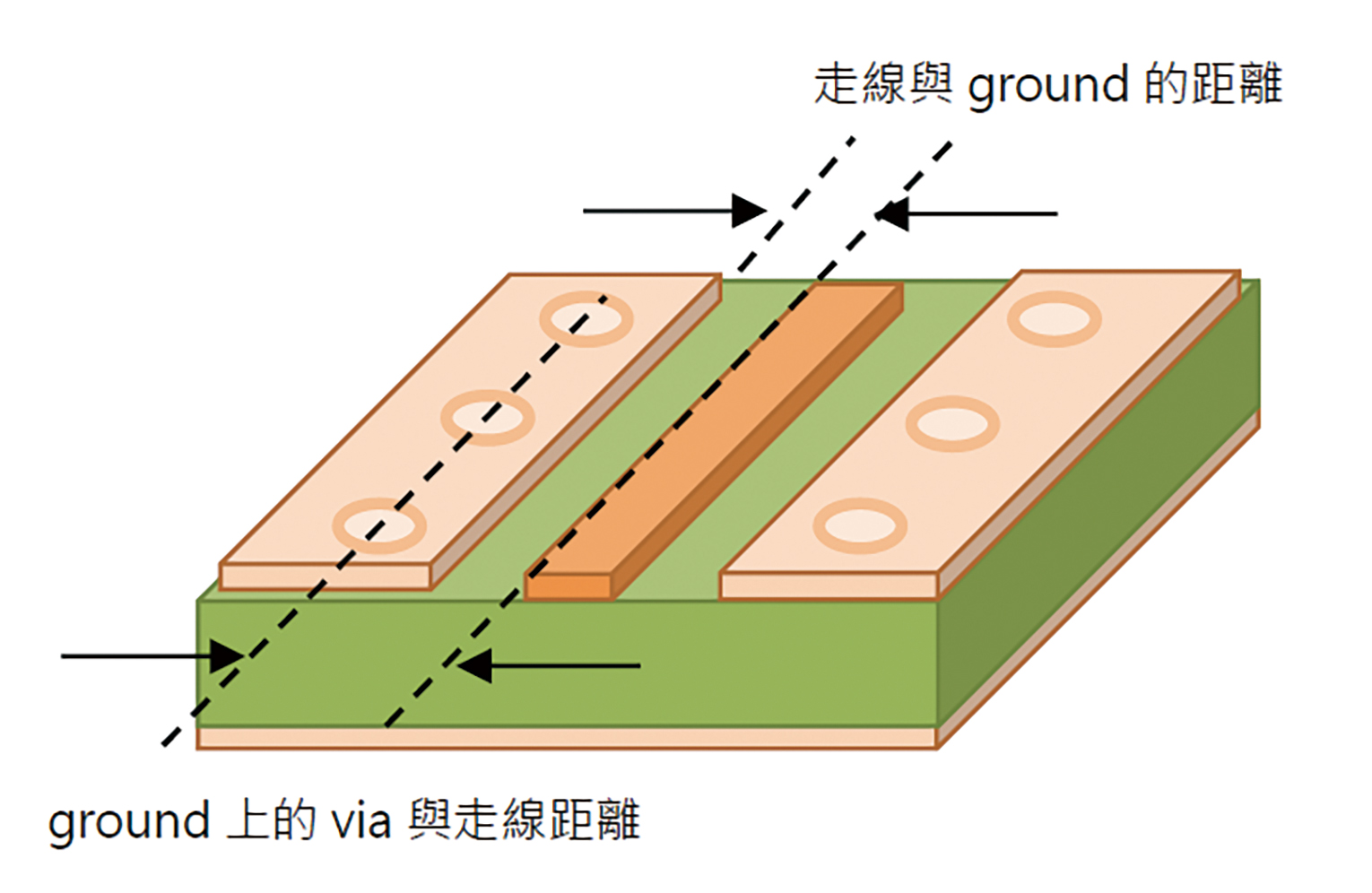

類似Microstrip,走線的兩旁用ground包覆(鋪銅導地),形成Waveguide的形狀。而相較於Microstrip,Coplanar Waveguide能夠變化的物理參數就比較多,例如走線與ground的距離、ground上的via與走線距離(圖6)。

圖6 走線與ground的距離、ground上的via與走線距離

圖6 走線與ground的距離、ground上的via與走線距離

由於Coplanar Waveguide兩旁是GND,因此可以降低Crosstalk的影響。但在設計上有個瓶頸:當應用上有密度較高的高頻走線的時候,例如PCIe,則此結構未必有足夠的空間可以在走線的兩側鋪銅接地。

本篇PCB技術淺談,著重在波反射、訊號誤判、板材挑選、波導結構等,事實上高頻PCB的設計與製造還須考慮眾多量測參數,包含S參數、串音耦合、PRBS、DC Balance(8B10B)等等。

(本文由百佳泰提供)