5G毫米波手機與基地台是發揮5G效能的必要設備,其設計也相較於先前4G時代挑戰更大,特別是射頻前端模組的開發,更是走向高整合的AiP與AiM的趨勢發展,協助高頻訊號接收的最佳化,成為5G步入毫米波時代的敲門磚。

根據GSMA預測,2025年5G技術占全體無線通訊網路約20%比例。從區域別來看,北美、中國與歐洲等區域,5G技術滲透有機會超過30%。在COVID-19疫情的催化下,物聯網裝置數量暴增,將5G的重要性推升到下一個層級。工研院產科國際所產業分析師劉美君指出,2020年5G相關半導體市場規模最大者為基頻與射頻晶片(特別是收發器(Transceiver))的發展,這也是年複合成長率較高的兩項產品。

高頻元件勢須低成本化

隨著基礎設施建設逐漸完備以及技術的日益成熟,5G將影響許多其他應用產品與服務提供。初步來看5G網路大多採用6GHz以下頻譜,除了美國一開始即專注於毫米波,然而毫米波不僅需要有多個天線模組,還要密集的基礎架構部署,故在應用毫米波相關零組件與模組相關成本較高。

在5G應用上可看到,手機、XR(AR/VR/MR)、CPE與各種基地台都會有RF前端的需求。隨著裝置數量增加,5G使用600MHz以上的頻寬將擴展到毫米波頻段,以解決對更大量裝置部署的需求。在這之中,支援高頻毫米波的基頻處理器和RF射頻相關零組件的低成本化將無可避免。

5G本身對於濾波器、交換器、功率放大器、低雜訊放大器(LNA)的元件數量與技術要求變高,加上裝置需支援頻段數量增加,使得RF前端模組的需求量節節攀升,導致RF前端模組的營收已逐漸趕上基頻營收,甚至有望超越基頻元件的成本。

円通科技總經理陳文江分析,現階段毫米波不管是高頻材料、製程與基頻SoC和升降頻器、波束成形器等晶片仍相當昂貴,期待年底iPhone 13全面支援毫米波的推出,帶動出貨量的成長,能夠在2021年底或2022年上半年帶動成本的大幅下降。

針對5G行動終端模組輕量化、小型化的需求,雖然SoC具有將多個不同功能的晶片整合在一起達到縮小化、降低成本的優點,但是過於複雜的晶片設計會大大增加晶片在分析、驗證甚至測試上的困難,使得開發時程變得冗長。

高度異質整合趨勢成形手機設計朝SiP+AiP發展

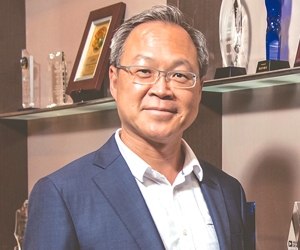

Ansys技術總監魏培森(圖1)認為,SiP(System in Package)是更適合實現5G RF模組的整合技術。因為RF模組不同於純數位晶片的整合,其特殊之處在於RF模組需要將RF元件、類比元件甚至是數位晶片結合在一起,這樣的要求正符合SiP能提供整合不同製程工藝、不同基板材料、同時構裝主被動元件甚至整合天線的AiP(Antenna in Package)技術。

圖1 Ansys技術總監魏培森表示相較於SoC的設計,SiP更適合作為RF模組的整合技術。

圖1 Ansys技術總監魏培森表示相較於SoC的設計,SiP更適合作為RF模組的整合技術。

以往軍事用途才用得上的高頻設計技術,因為5G毫米波短波長的特性,這些技術得以在5G商用的產品上實現,例如超小型化的天線;傳輸線架構的開/短路短截線(Open/Short Stub)取代外接電感/容集總元件做為RF的匹配電路;分布式(Distributed)的功率分配器、濾波器等,對於模組的縮小化與零組件的成本都有顯著的幫助。

在手機、筆電等系統級產品的設計上,比起以往單頻或多頻獨立天線的設計,陣列天線的控制尤其複雜。天線工程師們需要計算多組陣列天線模組的訊號涵蓋率,以找出最佳的陣列天線模組擺放位置。同時還需要針對各個設計的波束方向,準確地計算出所有天線單元輸出強度與相位來得到最佳的天線增益,藉以達到陣列天線的波束控制。

值得注意的是,魏培森強調,終端產品設計更需要考慮到電磁輻射對人體的影響。透過分析不同頻段、不同模組、不同距離的近天線平面的功率密度分布,來產生符合FCC(Federal Communications Commission)要求的功率密度報告。

此資料量可達到上萬筆,其資料處理所需耗費的人力與時間成本,讓全程採用量測來完成報告的方式變得極其困難。取而代之的是使用高準確度的三維電磁場模擬軟體,像是HFSS來協助找出最高功率密度的發生條件並搭配量測來簡化生成功率密度報告。

未來5G手機設計朝向高度的異質整合化已是不可逆的趨勢,特別是往結合SiP與AiP的方向發展。從封測設計的角度來看,日月光集團研發副總經理洪志斌(圖2)表示,此種設計模式會明顯墊高封裝設計難度,例如需要更密集的表面黏著技術(SMT),達成更高的隔離度需求,最佳的基板堆疊層數需求、更嚴苛的散熱需求等。因此除了由現有量產平台,釘架、球型陣列、覆晶封裝外,也會有新的平台,如扇出型晶圓級封裝技術(FOWLP),提供更先進整合技術。

圖2 日月光集團研發副總經理洪志斌認為SiP與AiP的整合型方案讓封裝設計更加困難,需仰賴SMT技術滿足隔離和散熱需求。

圖2 日月光集團研發副總經理洪志斌認為SiP與AiP的整合型方案讓封裝設計更加困難,需仰賴SMT技術滿足隔離和散熱需求。

FOWLP是從半導體裸晶的端點上,拉出需要的電路至重分布層(Redistribution Layer),進而形成封裝。因此不需封裝載板,不用打線(Wire)、凸塊(Bump),能夠降低30%的生產成本,也讓晶片更薄。整體來說,FOWLP技術讓晶片面積減少許多,也可取代成本較高的直通矽晶穿孔(TSV)達到透過封裝技術整合不同元件功能的目標。以往這種技術大多用於手機處理器,或是高效能運算(HPC)的應用,不過隨著高密度整合的需求升溫,預期下一步將導入製手機前端模組的設計。

雖說晶圓廠早已有FOWLP的方案量產,但因實際的製造成本仍偏高,故大多用於高階製程的應用上,預期未來封測廠的加入投入下,成本將有望進一步降低。

小基站主攻AiM設計

目前手機端因為面積的限制,主要以AiP為主,基地台因覆蓋範圍的不同,陣列大小不同,多以AiM(Antenna in Module)為主。Cadence技術經理連俊憲談到,基地台所需要的晶片非常多元,大多數的晶片都是封裝後嵌入在板子上,而這種設計精密度近似於載板製造,其設計可算是一種SiP或AiM概念,是介於傳統的PCB製造技術與載板之間的設計,目的是要縮短天線與晶片之間的路徑。換言之,現在基地台端可能採用分離式設計方式,或者是用AiP/AiM技術。

相較於手機市場RF模組採用IC載板的設計模式,主要由封測廠進行封裝整合,AiM則比較偏向於PCB技術的延伸,是PCB廠可著力的重點領域。連俊憲分析,PCB廠加入小基站AiM設計戰局可從兩方面著手,一是提高材料特性,PCB板可能需要找類似Rogers的板材,滿足高頻損耗低、金屬表面粗糙度低的材料;其次是PCB廠商需要升級其儀器設備、檢測、製造流程與曝光技術、曝光蝕刻材料等,以因應AiM對更高階的製造流程與驗證的需求。

另一方面,在基地台端除了傳統IC與天線分離設計和AiM設計外,洪志斌透露,歐、美、台、中、韓等各國也已有也有採用AiP設計方式,期能藉此提高系統設計上的彈性。他表示,即便基地台端的AiP需求不像手持應用端強烈,但受到新設計與高密度多向性設計的驅動下,刺激基地台廠商加速基地台引入AiP技術。此外,目前路上看到的基地台外型較大,裝置彈性較低,AiP技術的導入將提升基地台布建與設計彈性,尤其是未來5G的基地台建置手法與4G時期大相逕庭,需要的基地台數量增加許多,同時又必須易於安裝,並隱身於現有的公共設施上,就大大體現出AiP設計的優勢了。

綜合上述所言,陳文江補充,有些基地台廠商考慮以AiP方式解決大陣列彈性擴充整合的問題,但現階段多仍在嘗試的階段,目前主要小基站陣列需求以4×4、8×8為主,無AiP迫切需求。毫米波方案廠商多在開發布局階段,目前円通科已完成28GHz 4×4毫米波端模組的設計、測試及與基頻SoC平台的整合。

目前基地台廠商在選擇RF模組時,在Sub-6GHz頻段上的選擇,會先以3.5GHz n78頻段為主,後續則希望進一步支援4.8GHz頻段;毫米波部分則主要以28GHz頻段為主,主要除了希望產品能盡快投入市場外,前端模組以4×4、8×8的設計為主,並要求無風扇與更小的尺寸設計。

另一方面,在基頻設計上,可看到已有廠商,如恩智浦(NXP)提供Layerscape Access LA1200可編程基頻系列產品,同時支援Sub-6GHz和毫米波技術,為多個5G NR解決方案提供了單一架構。此外,該公司同時也提供廣泛的射頻功率多晶片模組(Multi-Chip Module, MCM)產品組合,可支援針對5G基站的大規模MIMO主動天線系統的開發,協助基地台和行動網路營運商縮短產品上市時間。