FPGA具備的彈性與降低成本的優勢,相當受到工程師的青睞。而為更進一步提升效能、降低成本與功耗,整合FPGA、硬體核心處理器與類比電路的高整合FPGA元件則更受到矚目。此外,整合FPGA元件還具備安全與靈活性等特色,在協助工程師加快產品設計的同時,並保有FPGA的效能。

現場可編程閘陣列(FPGA)的主要優勢在於靈活性,但是隨著高整合度成為另一個趨勢,FPGA的主要優勢便實現在靈活性和整合化上,而在這之後就是節省成本。因此FPGA的主要特色便包括靈活性、整合化加上節省成本。除此之外,FPGA在降低功耗,以及安全性方面都具有許多優勢,可謂數之不盡。

上述優勢正是使FPGA在這些年來變得受歡迎的原因。工程師對FPGA提供的靈活性、節省空間、省能及整合化等諸多優點青睞有加,因此,若能進一步提高靈活性和整合化水準,並且降低成本和占用空間,將更受工程師歡迎。為更符合市場需求,市面上新推出的SmartFusion晶片系列擁有FPGA傳統優點,且整合靈活的類比電路和嵌入式處理器,並具備節省占用空間、設計時間、功耗和成本等優勢。

提升FPGA整合度

|

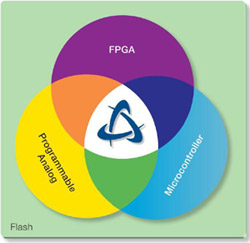

| 圖1 高整合FPGA三個基本組成架構 |

SmartFusion有三個基本部分,包括處理器、FPGA和類比電路模組(圖1)。這三個模組都整合在同一塊晶片中,並且都是可程式的,亦即處理器為軟體可程式、FPGA可經由標準FPGA設計流程進行程式,以及類比電路也可經由配置軟體進行程式,且所有模組都在工程師的掌控下,因此,雖然FPGA晶片出廠時是標準元件,但其所實現的產品卻具有非常高的靈活性。

可以把SmartFusion看作是一個包括處理器、FPGA可程式邏輯和可程式類比電路的「三腳椅」。通常一個工程團隊都會有專業技術人員分別負責軟體、邏輯設計和類比方面的工作。一般來說,這三部分的工程師使用高整合度FPGA時都會感到得心應手,但即便是只有一個工程師獨立工作,也能把FPGA用作可實現幾乎任何設計的通用萬能元件。此外,三個部分的設計工具和設計區域(Domain)已整合,且可互相通訊,此為嵌入式開發三大部分第一次真正的綜合,也可能是系統需要的唯一一顆FPGA晶片。

有些設計人員把高整合的FPGA看作是一顆處理器,有的視之為一顆FPGA,還有的認為是一種附有處理器和FPGA的通用類比晶片,這些說法都沒錯,因為這三個部分都是同樣重要。真正有趣的是,高整合FPGA不僅節省空間和成本,還能使設計更安全、靈活。由於產品的電子元件和互連基本上都位於晶片內部而非外部,因此毋須擔心印刷電路板(PCB)互連、意外的元件改變、介面出錯、供應鏈問題、逆向工程破解(Reverse-engineering)、通電湧入電流與射頻(RF)干擾等,高整合度FPGA元件可解決其中大多數問題。

透過快閃記憶體解決安全性問題

安全性意味著從安全措施到可靠性,以至反駭客等許多不同的範疇。「你的產品是安全的」這句話聽起來很不錯,但還不夠詳細明確。高整合FPGA可為產品帶來各類必需的安全性,FPGA使用快閃記憶體(Flash Memory)而不是靜態隨機存取記憶體(SRAM)儲存整個內部配置資料,這一點對於FPGA的安全性非常重要。

SRAM FPGA在啟動時處於完全空白的狀態,因此每次通電時必須從外部唯讀存儲記憶體(ROM)讀取資料重新載入。這意味著,在配置載入前,FPGA有若干毫秒的時間無法運行,直到重新載入完成,且整個載入過程都是對外公開的。換言之,工程師耗費數月甚至數年開發完成的FPGA配置資料,讓任何一個有示波器的人都可以看到,就如讀取ROM一樣簡單,而且完全沒有辦法阻止,只要複製ROM,就可以複製設計。

相反的,廠商推出的整合FPGA晶片採用內部快閃記憶體,永遠不會暴露在外,沒有ROM供那些擅長盜竊設計的逆向設計工程師讀取FPGA配置資料,亦即設計可全部安全穩地存放在晶片內部,即使用電子顯微鏡對矽片進行逐層剖析,也根本沒有辦法將設計提取出來,達到真正的萬無一失。這種方案帶來的一大好處是,晶片通電即用,換句話說,其運行模式跟大多數晶片差不多,也是大部分工程師所期望的晶片運行方式,這雖為小細節意義卻很大。試想,若主要(也許是唯一的)元件不是通電即用,其懸浮輸入輸出接腳會發生什麼事呢?會對通電初始化造成什麼樣的破壞呢?當與之連接的其他晶片輸入與沒有程式FPGA連接時,這些晶片又會做什麼呢?還有,在極不穩定的配置前狀態期間,若有人干擾各個配置接腳,該如何避免因此帶來的損害?下一步怎麼辦?要讓FPGA從始至終、每一次都按照工程師的設計方式運行,並非信口開河就能做到。

整合FPGA還有其他安全性方面的改進。由於FPGA、處理器和類比電路都同在一個元件中,所有功能模組都在晶片上,也就是說,從處理器到FPGA、從類比電路到處理器、或FPGA與類比電路間的所有資料傳送都安全,這一切都在晶片內進行,永遠不會經過任何人都能窺視的外部匯流排,因此當工程師須在系統內部傳送大量敏感資料時,無疑是極為有益的。此外,除了上述性能優勢外,FPGA還更快速、更省能。

工程師可能從不對資料進行再次加密,即使對資料交易進行加密,也只是防止資料被人窺視,一旦匯流排資料傳輸被限制在晶片上,整個問題都迎刃而解,若晶片不再存在安全隱患,工程師就能高枕無憂,全力以赴進行FPGA主要的運行設計。

重複設計縮短FPGA開發時間

工程技術的一大金科玉律是同一個東西決不設計第二次,管理術語稱之為設計重複使用。但這方面以往似乎做得不夠,從一個企劃到下一個企劃常常出現重複設計的現象。整合FPGA晶片上有這麼大量的可程式邏輯,可能帶來一個不容忽視的問題,即工程師如何實現所有邏輯,同時又不用在這項工作上花費數月時間?關於手中正在進行的設計,是否有人已經開發出了類似的東西?像脈衝寬度調變(PWM)和Reed-Solomon編碼器這類常用技術,應毋須從頭開始設計。

在這種情況下,廠商的DirectCore IP資料庫即有用武之地。DirectCore IP庫裡包括五十多個不同的IP模組,而且皆為免費,若這些都不符合要求,還有獨立的第三方IP模組供應商隨時願意為整合FPGA設計提供幫助,只須插入這些IP即可。

軟體同樣如此,而且常比硬體開發更費時間。對此,FPGA廠商提供大型的常用中間件庫,如傳輸控制通訊協定(TCP)/IP堆疊、文件系統、超文本傳輸協定(HTTP)、簡易郵件傳輸協定(SMTP),以及其他各種程式碼,都可免費取得。

從統計學來說,採用多個元件會增加設計風險,減少元件數目就會降低風險。就理想的狀況而言,就應該只有一個元件,且只有一家供應商。更理想的是,這一個元件還是可程式、可客製化的,這樣就不必擔心使用和競爭對手相同、既不能實現差異化,也不會讓設計加值的普通元件,而如果採用單一可程式客製化元件,就能取得低元件數目和低物料清單(BOM)成本所帶來的全部優勢,加上隨心所欲進行設計的自由度和靈活性,堪稱兩全其美。

大元件並不是指實體意義上的龐大。整合FPGA晶片的尺寸並不大,價格也不貴,因而適合於電池充電器、小型馬達控制器、個人電腦(PC)卡小型設備、顯示器驅動器等諸如此類的產品,可謂能力強大,而性能高、適用性廣泛則不一定意味著價格高昂。

處理器子系統等同微控制器

對於許多工程師而言,整合FPGA元件上的處理器是最熟悉的部分,這是因為元件是以安謀國際(ARM)Cortex-M3處理器為基礎。Cortex-M3是全球受歡迎的32位元處理器之一,也是適合於中階嵌入式系統的基本元件。

有些工程師聽到處理器和FPGA這兩個詞連在一起,就會叫苦連天,但高整合FPGA卻不是這樣,其無需用戶定義的指令集,而且沒有軟體支援的自建結構,是現成的Cortex-M3處理器核心。和目前全球正在使用的其他數百萬個以Cortex M3為基礎的晶片一樣,事實上,英特爾(Intel)只占全球處理器市場約2%,而不是一般人認為的90%;另一方面,立基於安謀國際的晶片每週都以比英特爾晶片多五倍的數量出貨,理由是英特爾的x86晶片主要占據的是個人電腦市場,而以安謀國際的處理器為基礎的產品幾乎遍布其餘所有範圍。

這種廣泛使用的好處也正顯示其流行程度,若使用的處理器越流行,就越容易找到配合的軟體、工具和人才研究顯示,大多數工程師都是先選擇作業系統和程式碼開發工具,然後選擇處理器。Cortex-M3處理器以100MHz的頻率運行,不同於許多精簡指令集運算(RISC)處理器,Cortex-M3包含一個硬體乘法器和除法器,因此不必採用軟體實現基本數學功能。該處理器還帶有一個記憶體保護單元(Memory Protection Unit, MPU),類似於一個精簡的記憶體管理單元(Memory Management unit, MMU),能根據要求分割和重新安排記憶體映射圖,並防止欺詐程式碼損害記憶體,然而又沒有複雜到讓工程師不得不處理頁錯誤和轉譯後 備緩衝器(Translation Lookaside Buffers, TLB)。當然,該處理器也有自己的記憶體和其他資源,在本文範例中,處理器帶有16K~64KB的高速SRAM,可用於儲存程式碼的執行和局部變數。此外,還附帶64K~512KB的非揮發性快閃記憶體。

根據處理器的速度,對快閃記憶體的初始存取占用五至七個週期不等。顯然,由於時脈頻率越高,時脈週期時間越短,故即使週期數目增加,時間總量卻保持不變,但無論處理器的速度如何,SRAM存取總是只占用一個週期。這種無等待狀態(No-wait-state)的記憶體速度很快,並劃分為兩個儲存區塊,以便兩大主控元件(處理器和DMA)能同時存取。另一個靈活特性是SRAM的位元段(Bit Banding)區,其允許C編譯器把單位元的布氏旗標(Boolean Flag)儲存在隨機存取記憶體(RAM)的一個位元中,毋須占用整個字元(或字)。若工程師須向晶片邊界外擴展,有一個外部儲存控制器可供使用。

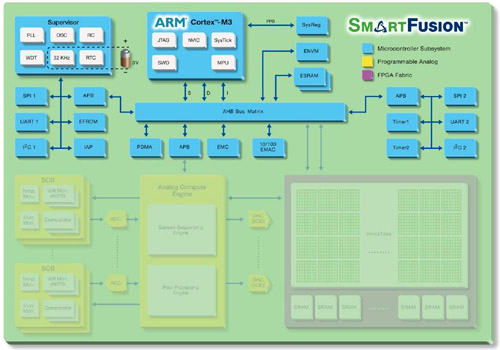

處理器周圍有大量的周邊控制器。其中包括10/100乙太網媒體存取(MAC)、兩個I2C埠、兩個通用異步收發傳輸器(UART)、兩個串列周邊介面(SPI)、一對定時器和一個八通道直接記憶體存取(DMA)控制器,簡言之,處理器子系統本身就是一個價值5美元的微控制器(圖2)。

|

| 圖2 整合FPGA微控制器子系統 |

硬核心處理器效能較佳

建立於FPGA的處理器發展過程充滿波折,有的非常驚人,有的略顯平凡。首先,基於FPGA的處理器分為軟核心和硬核心兩類,軟核心處理器利用FPGA本身的可程式邏輯建構處理器核心,會占用FPGA的部分(也許是大部分)邏輯單元,只留很少給其他電路,這已違背使用FPGA的初衷。更重要的是,早期的這些軟核心處理器的運行效能很差,導致微處理器不能充分映射到FPGA所提供的邏輯和互連類型上,缺乏合適的寄存器(Successive-approximation Register, SAR)、MUX、儲存和布線組合。結果導致在FPGA邏輯中實現的軟核心PowerPC、美普思(MIPS)或ARM處理器的速度很慢,大大浪費寶貴的FPGA資源。

根據初期實驗,大型FPGA公司往往都是從FPGA相容處理器起步,這類元件的性能要好得多。愛特(Actel)開發CoreABC;Altera設計Nios;而賽靈思(Xilinx)則開發MicroBlaze,在上述每一種設計中,處理器都被設計來匹配FPGA的可用資源,而不是把現有處理器勉強塞入不適合的FPGA中。不過廠商的第二代軟核心處理器均能更有效利用FPGA資源,以最小的額外成本提供較佳的性能。

另一類基於FPGA的處理器是硬核心處理器。毋須使用FPGA的可程式邏輯,而是永久整合在FPGA上的真正標準處理器,處理器得以全速運行,留下FPGA結構獨自執行其專長任務,無論是處理器還是FPGA結構都不必妥協犧牲,代之以共同協作。而高整合FPGA正是採用硬核心處理器方案,晶片上的FPGA架構完全免費,同時,Cortex-M3處理器配備完善,帶有滿足自身需求的各種快取記憶體、匯流排和介面,能全速運行。

類比子系統減少CPU工作負擔

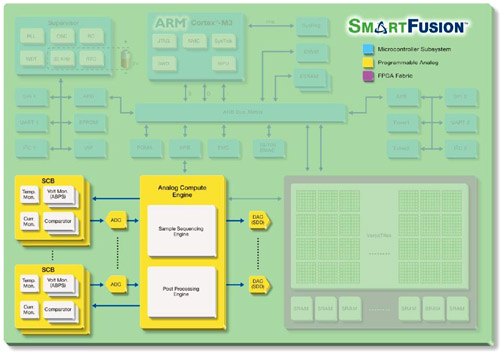

「可程式類比」(圖3)聽起來很矛盾,但這個概念簡潔優雅,讓硬體類比工程師和對類比唯恐避之不及的數位工程師都皆大歡喜。把整合FPGA的可程式類比視為一個找查表(Lookup Table, LUT)的FPGA,整合熟悉的可程式互連和一系列類比元件與模組,經由連接和整合不同的類比元件,可開發任何想要的類比前端、功能或特性,包括預分壓器、轉換器、感測器、模數轉換器、比較器、電流監測器與溫度監測器等。

|

| 圖3 高整合FPGA的可程式類比架構 |

每一款整合FPGA元件都帶有至少一個逐次逼近寄存器數位類比轉換器(ADC)。這個轉換器把電壓轉換為8、10或12位元數位,而且運行頻率達500k~600kHz(視解析度而定),這意味著可達到每秒五十萬次的採樣速率,對於大多數設計而言,應已足夠。ADC可採用十六對一多工器饋入,旨在同時對十六個不同的類比輸入進行採樣,但一次只讀取一個輸入的數位值。

若要使用另外的通道,即數模轉換,FPGA有12位元解析度的高效第一階Σ-Δ類比數位轉換器(DAC),標明高效是因為其內部架構建基於1位元DAC,不過其雜訊和解析度性能卻可與傳統12位元DAC媲美。類比部分與晶片的其他兩個主要部分直接相連︰FPGA架構和處理器的周邊匯流排(圖3中的APB #2)。類比電路和FPGA結構之間的路徑頻寬是32位元,故類比和數位邏輯間有很大的管線,從而使兩大部分成為真正的合作夥伴,而不僅是有距離的普通關係,可程式邏輯能與可程式類比電路緊密整合,反之亦然。這可比只有一個8位「針眼」通到類比區域,因而要把訊號和資料擠進一個微型介面好多了。

類比部分與處理器之間的第二個介面也很有用。處理器把類比模組視為一個周邊(如果需要,也可以是幾個周邊),因此處理器到類比模組的讀寫暢通無阻,從類比的角度來看,其又把處理器視為一個數位來源或接收器,非常類似於DAC或ADC的數位端。不過,晶片類比部分真正有趣的是其類比運算引擎(Analog Computing Engine, ACE),能為程式人員和類比工程師等節省大量時間,簡單來說,類比運算引擎就像可程式的第二個處理器,讓類比電路能循序且自行管理,無需處理器過多干預。

ACE能每次採樣後或在一個預設的時間後自動調節ADC採樣的解析度,如工程師可讓ADC自動調高或調低解析度,或是把採樣資料從一個ADC通道延遲到另一個通道。ACE還能根據來自晶片FPGA部分的訊號進行類比轉換(ADC或DAC任何一個方向),另一方面,當有事件發生時,如偵測到或達到特定採樣水平時,ACE可中斷Cortex-M3處理器。

不僅如此,ACE還能以yy=mx+b形式,包括校準,自行完成線性變換,或自行低通濾波、閾值比較或狀態濾波,所有這些都無需處理器干預,中央處理器(CPU)大可進入睡眠或執行其他工作,類比電路能自己「照顧」自己。

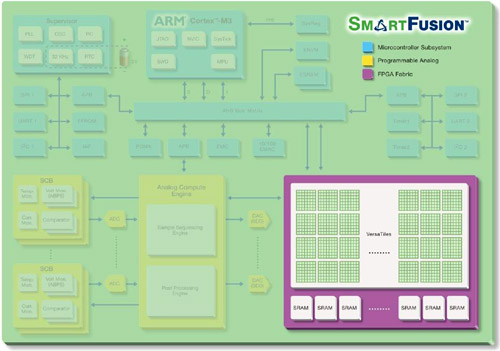

另外,廠商推出的高整合FPGA晶片都包含大量的FPGA架構,例如最小的元件上就附有一千五百三十六個邏輯單元;最大的元件包含一萬一千五百二十個單元,每一個單元大約相當於一個D型觸發器,或三輸入LUT(圖4)。

|

| 圖4 整合FPGA元件的FPGA子系統架構 |

工程就是針對某一個問題找到最有效的解決方案。有時軟體方案效果最好,有時其屬於硬體範疇,還有的時候解決方案在類比領域,實際上,最常見的往往是上述所有類型的混合。由於有如此多針對不同產品要求的不同工程方案,因此不存在一個「典型的」嵌入式系統。

美國有句諺語,當你手上只有一把錘子的時候,任何問題在你眼裡都是一枚釘子。缺乏經驗的工程師,不管這個問題屬於硬體、軟體還是類比電路範疇,都試圖利用熟知的某一種工具解決所有問題,而整合硬體、軟體和類比電路通常不失為最佳也是最有效的解決方案,但實際上卻很難這麼做。

協調一致的整合有助於實現最佳的工程解決方案,而且在商業上也頗有意義。管理層削減工程預算和人員數目,意味著更少的工程師要做更多的工作,但時間和預算壓力毫不見鬆懈,產品壽命週期卻往往越來越短,更高的靈活性漸漸變成一種企業要求,而工程靈活性可能成為事業的救星。

(本文作者為Silicon Insider創辦人)