消費性電子產品對低功耗與快速上市的要求,讓擁有靈活設計彈性的可編程邏輯元件(PLD)日益受到市場青睞。不同於特定應用積體電路(ASIC)和特定應用標準產品(ASSP)曠日費時的研發週期及高昂的非重複性工程費用(NRE),PLD可編程特性,不僅能協助開發人員在有限時間內以最具成本效益的方式完成產品開發,亦是創新差異化功能的絕佳利器,特別是基於非揮發性(Non-Volatile)技術的PLD,由於兼具高整合度與低功耗特性,更已廣泛用於消費性電子產品。

為在有限的產品上市時間內,應對不斷變化的市場標準,可編程邏輯元件(PLD)已廣泛地應用於消費電子產品中。不同於特定應用積體電路(ASIC)和特定應用標準產品(ASSP)的開發需要昂貴的非重複性工程費用,PLD是標準的現成元件,可針對各種應用使用靈活的軟體工具進行設計。

低功耗成產品市場區隔關鍵

|

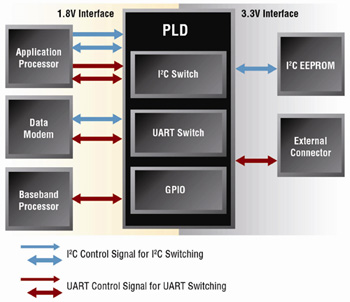

| 圖1 在手機中使用PLD |

降低靜態功耗一直是消費電子產品設計人員面臨的挑戰。許多電池供電的產品,如智慧型手機、全球衛星定位系統(GPS)設備、行動運算和數位相機,提高電池續航力是最重要的差異化特徵之一。由於設計人員力求符合最新的能源之星和歐盟管理守則的規定,對於許多透過牆上插座供電的電子設備而言,低功耗也越來越重要。

在許多消費電子系統中,透過提供先進的匯流排介面和橋接功能,PLD可擴展當前一代的應用處理器或中央處理器(CPU)的使用率。這些匯流排介面和橋接功能通常不會有非常高的性能要求,圖1展示這樣一個應用實例。此外,PLD還經常用來實現人機介面控制器、顯示控制器、外部記憶體介面控制器和脈衝寬度調變(PWM)控制器。表1顯示在消費性電子市場中常見的PLD應用。

一如高階FPGA,現在低密度PLD也有先進的輸入/輸出(I/O)功能,包括支援不同的I/O標準、多個I/O Bank,以及多種電壓。這些特性允許使用PLD實現ASIC/ASSP、記憶體、處理器,以及通常有不匹配的電壓和I/O標準的其他元件之間的互連邏輯。

|

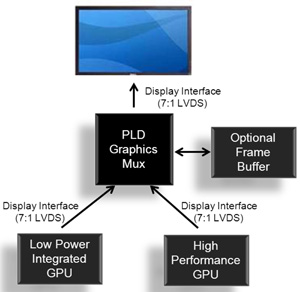

| 圖2 基於PLD的圖形多工器 |

如圖2所示,對於將低成本、低密度PLD用於先進的互連邏輯,圖形多工器是一個理想的例子。筆記型電腦和可攜式電源管理的最新趨勢是,英特爾(Intel)可切換顯示卡的倡議,圖形多工器選擇基於應用需求的圖形控制器。低功耗整合型繪圖處理器(GPU)用於諸如文字處理,電子郵件和網際網路瀏覽的常規應用;高性能的獨立GPU用於高性能的應用,諸如遊戲、視頻編輯和播放高畫質視頻。PLD支援低壓差動訊號(LVDS)I/O標準和內置的GEAR BOX和鎖相迴路(PLL),能與圖形處理器介面實現智慧多路演算法,以減少或消除切換時的視覺效果,並直接驅動液晶顯示幕。

以萊迪思(Lattice)MachXO2 PLD系列為例,其採用優化的查閱資料表(LUT)結構與65奈米(nm)嵌入式快閃記憶體製程技術相結合,可為消費電子設計提供靈活、全功能的解決方案。

封裝/整合度攸關成本高低

廠商推出的PLD元件有各種低成本、無鹵素的封裝。可用的封裝選擇包括低成本的球型陣列封裝(BGA)和薄四方扁平封裝(TQFP),以及先進的晶圓級晶片級封裝和微型晶片級封裝。其中,BGA盡可能減少的訊號布線層,以降低整個封裝的成本。這些封裝的設計使所有的I/O和電源連接能從印刷電路板(PCB)布線的二至四層引出,這樣的做法能避免使用較高成本的製造技術,如埋孔或盲孔,以及鐳射鑽孔。廠商推出的PLD,其封裝的I/O分配能使同一封裝實現密度遷移,當設計有變,需一個容量更大或更小的PLD元件時,將有助於利用同樣的電路板。

|

| 圖3 PLD可達高整合度 |

圖3所示為PLD整合分立邏輯元件,如I/O擴展器、電平和匯流排橋接轉換器、電壓調節器、時鐘源和配置器件,所有這些都整合在單個元件中。以MachXO2元件為例,其內含256Kb的嵌入式快閃記憶體,這些片上用戶快閃記憶體(UFM)使元件能整合外部非揮發性記憶體,可用於各種應用,包括儲存設定檔、儲存可編程式唯讀記憶體(PROM)資料,或作為使用者的快閃記憶體。元件還具有標稱精度為±5%的內部振盪器,可用來作為設計的時鐘源,因此無需外部振盪器。

序列介面匯流排(SPI)、I2C控制器和計時器/計數器是消費電子設計中最常用的功能。設計人員經常用PLD實現SPI或I2C匯流排擴展。計時器/計數器也經常被用來生成狀態訊號。廠商的PLD元件擁有這些常用功能的硬體實作電路,而此類的I2C、SPI和計時器/計數器功能可用於在設計中實現附加的邏輯。

PLD非揮發性特性降低功耗

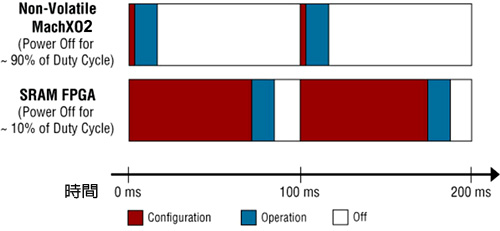

除靜態和動態功耗外,功耗的額外部分與上電和配置有關。這是PLD/現場可編程閘陣列(FPGA)進入使用者模式前,上電和配置期間的功耗,功耗與進入使用者模式所需的時間成正比。電路板設計人員須考慮這一部分額外的功耗,同時確定電源的要求。許多消費性電子系統設計成使FPGA或PLD頻繁開/關迴圈。由於開/關週期頻繁的行為加劇這一額外的功耗,因此帶有片上配置記憶體的PLD元件,可用微秒的時間自我配置,儘量減少上電和配置過程中的功耗。圖4顯示MachXO2 PLD與基於靜態隨機存取記憶體(SRAM)的FPGA進入使用者模式所需時間的比較。

|

| 圖4 非揮發性PLD與SRAM FPGA進入使用者模式的時間比 |

設計工具加速創新

利用PLD進行產品設計時能否順利,各式參考設計與套件將扮演關鍵角色。現在設計人員可使用Lattice Diamond v1.3版本軟體進行MachXO2元件設計,該軟體可從網站免費下載。

為消費電子應用而優化的全套參考設計包括LatticeMico8微控制器(MCU),外加如通用異步收發器(UART)、I2C主/從,SPI主/從,I2S控制器和各種快閃記憶體控制器的。該參考設計原始程式碼包括HDL和固化元件,可根據實際應用要求進行修改。

(本文作者任職於萊迪思)