功耗管理一向是業界重視的議題之一,而隨著製程演進,儘管運作電壓下降,漏電問題卻未改善。所幸,若能採用彈性設計的FPGA產品,並善用互相搭配的軟體工具與設計技巧,不論是動態或是靜態功耗的漏電都可獲得長足改進。

IC製程在過去6年間,從130奈米演進至90奈米,一直到現在的65奈米,功耗管理的重要性在每個製程階段持續攀升。在130奈米環境中,製造商開始注意到電晶體的漏電狀況,甚至在待機模式也會漏電。在90奈米階段,IC的運作電壓下降,但漏電卻持續攀升,浪費掉極高比例的元件功耗。不幸地是,這些趨勢在65奈米也將持續。的確,65奈米節點的漏電還是相當明顯,這也使得許多研發業者將管理功耗看得和達成效能目標一樣重要。

由於現場可編程閘陣列(FPGA)廠商向來都是針對眾多規格來設計其產品,在其元件中加入眾多高速電晶體,FPGA一向不是最耗電的元件。如同最先進製程中的其他矽元件一樣,採用的也是會漏電的電晶體。但研發業者可利用FPGA的可編程彈性,搭配相關的工具,精準地估算功耗,之後再讓其FPGA設計及印刷電路板(PCB)更加省電。

FPGA的功耗大概可分成兩類︰靜態與動態。靜態功耗是由漏電的電晶體所造成,即使在設計中沒有執行任何工作的電晶體也會漏電。動態功耗則是在執行作業時,元件所消耗的電力,和電壓、頻率及電容呈函數關係的切換節點。所以了解功耗的種類,以及在不同運作狀態下的變化,藉以妥善地最佳化,對於是否能達成設計案的功耗預算,是非常重要的。

動/靜態功耗同受重視

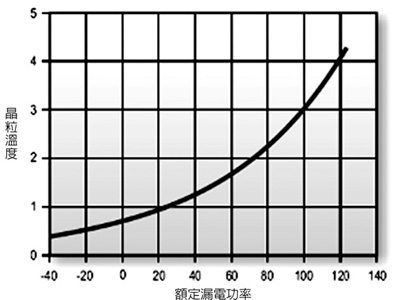

特定應用積體電路(ASIC)與FPGA在90奈米甚至更具挑戰性的65奈米製程中,都會出現相當明顯的漏電流。為了讓電晶體達到更高效能,故須調低臨界電壓,但這卻會助長漏電。雖然目前業界已採取許多方法來降低漏電,但在最糟情況與一般程序中,漏電的靜態功耗變化比還是約為2:1。核心電壓(VCCINT)也會對漏電產生可觀的影響,和VCCINT的立方呈一定比例的變化。VCCINT提高5%,靜態功耗大約會增加15%。最後,接點或晶粒的溫度也會對漏電有顯著影響。圖1與圖2顯示靜態功耗的變化,以及漏電及電壓與溫度之間的關係。

|

| 圖1 漏電與接點溫度關聯圖 |

|

| 圖2 漏電與核心電壓關聯圖 |

FPGA中靜態功耗的另一個來源,是運作電路的直流電(DC),但一般而言它們不會隨著製程與溫度而改變。例如像輸入/輸出(I/O)直流電如HSTL、SSTL、LVDS這些有終端電阻的標準,其I/O終端元件的電壓,以及像LVDS這類電流驅動器I/O的直流電。有些FPGA類比模塊也是靜態功耗的來源,也會隨製程與溫度而產生變化。其中包括數位時脈管理器(DCM)、FPGA中的時脈控制元件、鎖相迴路(PLL),以及FPGA中用來在輸入與輸出端選擇可編程延遲設定的元件。

動態功耗是指當FPGA的核心或I/O進行切換作業時所消耗的電力。想要計算動態功耗,就必須知道切換電晶體與電路的數量、電容及切換頻率。電晶體用作為邏輯元件,以及FPGA內部金屬線路的可編程互連元件。電容又可包括電晶體的寄生電容,以及金屬內連線的電容兩種。一般動態功耗的計算公式為PDYNAMIC=nCV2f,其中n為切換節點的數量,C代表電容,V是電壓擺幅,而f則是切換頻率。

若藉由內部FPGA架構的變更,形成為更緊密的邏輯封裝,將能減少切換電晶體的數量。運用較小的電晶體,能縮小電晶體之間的線路長度,進而降低動態功耗。目前65奈米的FPGA電晶體,就具有較低的閘極電容與較短的內連線,兩者結合可讓節點電容降低約15~20%,進而降低動態功耗。

電壓也是影響動態功耗的因素之一。從90奈米轉移至65奈米製程節點,光是VCCINT從1.2伏特降至1伏特,就可讓FPGA的動態功耗降低約30%。因此架構方面的改進,讓動態功耗比90奈米技術降低40~50%。值得一提的是,雖然動態功耗與VCCINT的平方成正比,但FPGA核心的溫度與製程變數影響的程度也很可觀。

FPGA分析工具精準拿捏功耗

目前已問世的功耗分析工具有幾種,此次擇二介紹。第一種屬於試算表工具,是在研發業者開始運用建置工具之前來使用;而當開發人員已建置設計,並檢查變更對功耗會產生什麼樣的影響後,再使用第二種工具。

第一種試算表工具允許設計人員在一個試算表環境中,根據FPGA中各項資源的使用狀況、切換速度、負載等方面的描述,快速估算出功耗。這個工具用來初步估算功耗、選擇電源供應器與穩壓器以及為系統選擇適合的冷卻方案如散熱片、散熱風扇及其他類似的配備。

利用這款以微軟(Microsoft)為Excel試算表環境的工具,系統工程師可做出元件設計與系統導向的功耗決策。設計人員只須輸入各項預估的設計參數如資源使用率、運作環境以及時脈和切換速度。之後工具即會針對設計案計算出預估功耗,並求出總功耗、最高接點溫度以及各電路和模塊的功耗。

在設定估算方面,工具的Process功能是一項重要的技術。它讓設計者看到各模塊在一般或最糟狀況的功耗。首先,VCCINT電源漏電的靜態功耗,和製程有直接關係。此外,在Voltage Source Summary中可以立即看到電壓變化時對功耗產生的效應。對於了解與VCCINT的關連,這項功能相當重要,VCCINT是代表所有核心邏輯的電源之一。在試算工具中選取的製程變異及電壓變異,確保設計人員能為最糟狀況選取適當電源規格。

這類試算表的另一項重要功能是Thermal Information/Summary,能讓設計人員指定散熱片、印刷電路板屬性及溫度等資訊。這項功能確保設計案能符合商業級或工業級元件的熱溫規格。Block Summary還會顯示每個模塊的功耗,Power Summary則會顯示靜態與動態功耗的總和。

每個標籤頁則方便輸入每種資源的使用資訊以及切換速度,例如像時脈、邏輯、I/O、區塊RAM(BRAM)、鎖相迴路、數位訊號處理器等。

另一項值得一提的工具特色,是Graphs標籤頁/分頁可透過圖形化的資訊,觀看功能、製程、電壓及溫度變異所對應的功耗。尤其是Power by Function圖形,不僅列出每項特徵,還會顯示其功耗,方便找出哪些特徵能透過最佳化得到最高的效益。

第二種電源分析工具,則會根據在建置過程中擷取到的實際資源資訊,提供更精準的電源分類項目圖形。例如可在工具中輸入測試與模擬向量或執行無向量的電源估算。這項工具使用有特徵的電容資料,以對應FPGA設計的各項物理資源。

由於該分析工具連結至供應商的軟體環境Integrated Software Environment(ISE),因此能接受配置與繞線後的資訊,包括多種內部檔案格式。

它還能接受業界標準的Value Change Dump(VCD)與Switching Activity Interchange Format(SAIF)格式的檔案。

倘若使用VCD或SAIF格式,就須要建立代表性的模擬向量,如此才能讓工具紀錄系統中各節點的切換速度,以便日後能存取資料。若沒有這些模擬檔案,使用者可透過這項分析工具來執行無向量的模擬。這種模擬採用數學與統計的模型方法,將啟始的切換速度散布到實際設計邏輯。之後會產生一個結果,包含設計中每個節點的切換速度。

在向量型(從VCD與SAIF格式)檔案與無向量型變異方面,這項分析工具會考量配置與繞線設計的物理連結能力,並擷取出資源的使用狀況。此工具會交叉參照每個節點的活動或切換速度,並參照有特徵的電容資料,對照每個模塊在每種切換速度下的物理資源與動態功耗。結果如圖3所示,代表總功耗及最高的接點溫度,並含有電路、模塊及各階層的功耗報告。

|

| 圖3 分析工具圖例 |

這項分析工具讓使用者看到設計案的詳細功耗狀況,並進行「如果...則會...」的條件式分析,在掌握充分的資訊後,再選擇哪些模塊能透過最佳化得到最多的利益,包括從簡單的方法一直到重新規畫整個架構。此外,尚可運用此工具來記錄一個設計案的實際電力規格,並將資訊傳遞到機板層級。

設計技巧壓低FPGA功耗

隨著製程縮小至65奈米,業界對功耗的要求也跟著提升,為了達到更嚴苛的設計目標,勢必須要運用新的工具、手段及技術來進一步降低功耗。

慎選FPGA產品

其中一種降低功耗的方法,是針對設計選擇適合的FPGA,然後運用其可編程能力,更進一步最佳化設計案的功耗。當然,根據不同設計所進行的選擇,會直接影響靜態與動態的功耗。

漏電引起的靜態功耗,會和邏輯元件的數量成正比,也和FPGA內的電晶體數量成正比。因此,如果減少使用的FPGA資源,就能把設計內容建置在較小的元件,進而降低漏電量。轉移至下個規格更小的元件,產生的效應如表1。

| 表1 降低元件尺寸所減少的靜態功耗 |

| 邏輯閘數量(k) |

轉移至較小的元件所減少的靜態功耗 |

| 300~220 |

33% |

220k~110k

|

-51% |

110k~85k

|

-24% |

85k~50k

|

-46% |

| 50k~30k |

-33% |

想要降低設計的尺寸,尚可運用許多技術,包括從邏輯功能的時槽技術著手。倘若有兩組線路執行FPGA中的一組線性功能,並相互複製,設計人員就可使用其中一組線路,以兩倍速度運行,之後再把資料重複用到該線路的單一事件。這種方式僅用到一半邏輯資源。

重新設計有助更換電路

另一種減少邏輯資源的方法,是採用產品提供的部分重新設定功能,把部分的電路換成新的區塊,當僅需要一部分電路時,就適合採用這種方法。

當然,也可以把功能轉移至無設限的可用資源,例如把BRAM轉移至狀態機器,把計數器轉移至乘法、加法與數位訊號處理器(DSP)模塊,暫存器轉移至移位暫存器邏輯,以及把BRAM轉移至查表RAM(LUTRAM)。藉此確認沒有讓自己的設計過度限制時序,避免重複配置邏輯/暫存器等資源。

此外,也可以充分利用已建置在FPGA架構中的硬式IP模塊如BRAM、DSP、FIFO、乙太網路MAC、PCI Express等。

仔細審查設計

另一種降低靜態功耗的方法,是仔細審查原始設計,並除去會消耗DC直流電的冗餘元件。一般設計中通常有許多模塊會有無關或隱藏的DCM或PLL。倘若在重新設計模塊時,忘了移除這些元件,或是在建構新一代產品時用到一些舊的程式碼,都會遇到這種情況。將DCM或PLL擷取到設計的最上層,讓模塊能共用各項資源,將能進一步降低設計規模及DC直流電功耗。

明智地運用記憶體模塊,亦有助於降低FPGA設計的動態功耗,進而降低整體功耗。由於動態功耗是電容(面積或長度)與頻率的函數,因此應檢討設計案在存取區塊記憶體的方法,並找出能對電容與頻率進行最佳化的區域。

目前已問世的FPGA包含兩種記憶體陣列,提供18k或36k位元容量的BRAM,針對大型記憶體區塊進行最佳化。LUTRAM則是針對小量微調的功能進行最佳化,採用FPGA中的查表作為基礎。LUTRAM以64位元單元的形態,嵌入於FPGA中。

在這兩種類型中,BRAM的功耗通常較高。它的啟用速率(Enable Rate)通常占BRAM功耗中最大的比例,比重排第二的則是切換作業。研發業者可利用幾種步驟來降低BRAM功耗。例如可讓BRAM僅在讀取或寫入時才啟動:也可以針對小型記憶體模塊,運用LUTRAM來取代BRAM,將BRAM用來支援較大的記憶體。此外,亦可嘗試用BRAM支援多個大型模塊。

而FPGA在時脈控制閘方面也有許多令人感興趣的功能,例如可使用BUFGMUX時脈緩衝區,讓FPGA關閉全域時脈,或機動地選擇較低的時脈。

另一個技術是運用記憶體陣列來減少空間、提高效能、或降低功耗。圖4顯示一個2k×36位元的儲存陣列,此陣列針對速度與空間進行最佳化。若以平行模式使用四個2k×9位元來構成這個元件,當增加一個新的數值時,永遠啟動所有模塊。

|

| 圖4 左為速度與空間與功耗最佳化的記憶體陣列示意圖,右為具備功耗與空間選擇的方塊記憶體啟動工具。 |

也可以藉由建構四個512×36位元模塊,來運用另一種2k×36位元的模式,但須把較低位的兩個位址位元進行解碼,選擇被存取的512×36位元模塊。在後面這種情況中,一次存取不超過一個記憶體模塊,所消耗的電力會比第一種模式減少75%。

圖4的右半部顯示方塊記憶體啟動工具,這個工具可建立指定容量的記憶體陣列,並針對速度與功耗進行最佳化。圖5則是前文述及的電源分析工具,用來比較在一個特定啟動速度下N模塊的功耗,以及在該啟動速度下N/4模塊的功耗。

結果顯示動態功耗減少75%。

|

| 圖5 功耗最佳化陣列的功耗試算表結果 |

目前多數公司都可協助設計人員針對所須執行任務挑選適合的記憶體陣列。若在一個設計中打造兩組記憶體儲存陣列,在其中一個案例中,將需要十六組64×32位元的記憶體結構(總位元為32k),運作時脈為300MHz;在另一個案例中,則將需要十六組512×36位元的記憶體結構(總位元為294k)。

若進一步分析十六組64×32位元記憶體結構功耗,電源分析試算工具則將告知小型記憶體陣列最適合建置在LUTRAM(圖6)。相較於建置在BRAM,若是建置在LUTRAM可省下85%的功耗。這是因為在BRAM浪費許多空間,而且使用十六組18位元模塊才得到十六個極小(64×32位元)的記憶體。

|

| 圖6 運用模塊RAM或LUTRAM所估算的小型記憶體功耗 |

但在第二個案例中,十六組18k位元陣列的功耗比較,電源分析試算工具顯示大型記憶體陣列(圖7)有相反的情況。將它們建置在BRAM而非LUTRAM,能節省28%功耗,這是因為許多小型元件須要啟動與互連所致。

|

| 圖7 運用LUTRAM與區塊RAM所估算的大型記憶體功耗 |

如前所述,FPGA在時脈控制閘方面也有一些有趣功能。例如,設計者可使用BUFGMUX時脈緩衝區,讓FPGA關閉全域時脈,或是機動選擇較慢的時脈。

也可以使用BUFGCE時脈緩衝區,以類似ASIC設計中採用的週期閘控(Cycle-gating)方法,來執行週期時脈閘控。而這兩種功能是可以同時使用的。

當某些模塊沒有使用,但本身卻會消耗電力時,上述技術的成效尤其顯著。一般來說,在這些情況,可關閉大部分的時脈領域,其中涵蓋數千個時脈作業,可關閉特定的時脈週期,或一次關閉多個時脈週期。

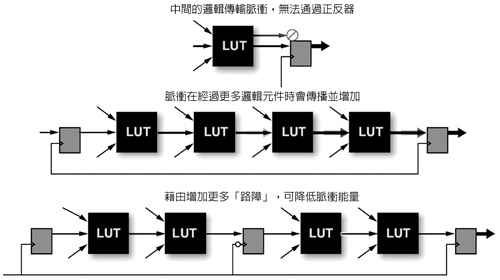

也可以藉由減少脈衝功耗來降低動態功耗。在含有邏輯與暫存器的設計中,有時連結至一個整合邏輯元件的多個輸入端,會在稍微不同的時間點抵達,所產生的短時間脈衝,會傳播到其他結構,而且會浪費功耗(圖8)。在各邏輯層之間運用更多管線,即可阻止脈衝擴散到其他結構,進而降低動態功耗。

|

| 圖8 脈衝的傳播,以及運用插入的正反器來加以阻擋 |

從機板層級降低功耗

在降低FPGA功耗方面,考量機板層級的設計時,印刷電路板設計師、機械工程師及系統工程師各自會考量幾項因素。FPGA的核心電壓與接點溫度會強烈影響各元件的功耗。

從機板層級降低功耗方面,其中一種方法是控制VCCINT核心電壓。漏電與動態功耗所產生的靜態功耗,和FPGA的核心電壓有密切關係。

因此,降低漏電的一種方法,就是將核心電壓調至接近額定數值,而不是FPGA產品運作範圍的頂端。利用現今的切換穩壓器,可達到±1.5%的電壓容許度,相對於±5%的規格容許率。若將核心電壓維持在1伏特的額定值,而不是1.05伏特的最高設定範圍,能降低漏電產生的靜態功耗15%,並降低動態功耗10%。

另外,亦可藉由控制接點溫度來降低功耗。設計中的FPGA、印刷電路板、散熱片、周圍溫度、氣流及FPGA功耗都會影響FPGA的接點溫度。

降低FPGA接點溫度的一項簡單且明顯的方法,就是使用散熱效率較好的印刷電路板或散熱片。如此一來,FPGA研發業者進行的任何變更,也能同時降低功耗。若當接點的溫度上升達到100℃時,溫度若降低15℃,則漏電產生的靜態功耗就會降低20%。

另一種降低功耗的方法,是監控FPGA中的溫度與電壓。部分FPGA產品內含一個監視用的類比模塊,它能監視外部或內部的類比元件電壓及晶粒溫度。此監視用類比模塊旁有一個10位元的類比數位轉換器,此轉換器能在-40~125℃的範圍之間,提供精準且可靠的結果。類比數位轉換器能將晶片內部感測器的輸出結果進行數位化,並用它監視最多十七個外部類比輸入端,以檢查在環境方面的系統效能。

模塊中包含可設定的臨界值與警示界限,並把它所量測到的結果儲存在可設定的暫存器,這些暫存器能輕易連結至使用者的邏輯或微處理器,或可透過JTAG埠,甚至在開機啟動後、FPGA設定之前來讀取這些數值。

當透過電晶體改良、減少電容及降低電壓等手段來調低核心電壓後,I/O功耗成為另一個在平衡功耗與效能方面必須注意的重要考量因素。想掌握充分的資訊來做明智的選擇,必須考量每個FPGA設計的I/O介面需求。

連結記憶體如DDR2、QDR、RLDRAM等時,可能須要在FPGA中配置終端元件,以維持訊號完整性,但也通常會消耗更多電力,而且會提高接點的溫度。

同時,若把FPGA連結至ASIC/特定應用標準產品(ASSP),就必須根據ASIC/ASSP的目標規格如LVDS、HSTL等選擇適合的介面。若把一個FPGA連結至另一個FPGA,則可能根據設計的效能需求,選擇適合的介面,並可能更快找到機會進行功耗最佳化。

在輸入與輸出功耗方面,如LVDS、HSTL及SSTL等參考標準會消耗最多電力。在輸出方面,高驅動強度的標準,消耗大多數電力,輸出的啟動速度與切換速度會和功耗成線性比例。但LVDS是個例外,因為它採用一個固定電流,且不受切換速度所影響。

在輸入方面,參考標準會消耗大多數電力,因為它的接收結構含有不同的接收器,加上因為它們含有一個可選用的內部終端元件。兩者都會消耗直流電力。

若在FPGA中加入可機動調整三態數位控制阻抗的功能,將讓使用者機動地移除終端機制,在當某個I/O銲墊用作為輸出端時就能啟用。這對資料匯流排或記憶體介面相當有用,依據讀取與寫入比率,它能控制可觀的電力(圖9)。

|

| 圖9 FPGA接腳顯示運用T_DCI進行記憶體讀取與記憶體寫入的狀況 |

在選擇I/O介面時,重點在於能明智地選擇兼顧效能與功耗的介面。當設計需要最高效能與最低雜訊,或是目標元件需要I/O標準時,則應採用如LVDS等介面。 由於終端元件通常會耗用大量的電力,故須明智地運用,並考量在功耗與效能之間取得理想平衡點。採用外部終端或沒有終端元件的機制,能大幅降低功耗。

整體解決方案降低功耗

自從電源管理成為一項重要議題後,業者們一直努力開發功耗最佳化技術,並融入至套件中。除了整合套件外,亦可設定功耗最佳化合成引擎,可自動找到來源程式碼中的小型陣列,並將它們合成至LUTRAM。引擎會根據指定的大小找到大型陣列,並將它們合成至區塊RAM。若它找到一個大型計數器,就會建置到一個DSP48模塊。當複製邏輯,以確保僅建置最佳數量時,它也可以做出明智的選擇。

近期尚出現一款新的最佳化定位器,能結合多種功能,藉以降低路由與電容的距離。此款相關工具可讓設計者挑選一組邏輯,並實際將其置於FPGA的一般區域。這將有助於降低電容,並加快路由時間。

一般認為,動態與靜態功耗將會繼續衍生許多挑戰。但在此同時,若業者們不僅努力最佳化自身的電源管理工具與方法,亦集中心力解決矽元件的各種將發生的電源問題,各種挑戰仍有望迎刃而解。

(本文作者為賽靈思技術行銷部首席工程師)