每當大量的資料處理或傳送,串列資料系統即扮演著非常重要的角色。工程師開發高速元件如發射器、接收器及資料訊號通道,其中抖動(Jitter)會是一個關鍵問題。串列高速通訊系統須要操作在很狹窄之邊界內,資料提供的速度極其快,且極低的異常錯誤機率。對於開發者來說,所面臨的挑戰是建立極低成本的高速系統,使產品具有市場競爭。

抖動測量 檢視眼圖/誤碼率

討論抖動的主題將完全超出此本文範圍。相反地,這裡提供一個通用的抖動介紹、原因和方法之抖動測量,特別是誤碼率(BER)和眼圖(Eye Diagram)。本文也將談論串列高速元件關於標準抖動容忍限制測量,並且將詳細觀察快捷外設互聯標準(PCI Express, PCIe)接收器進行抖動測試的情形。

抖動關乎訊號品質

抖動是數位領域中使用的術語,從它的起因和導致的影響是與類比的本質很像的。二進位制的資料是由隨機的1和0位元(bits)所組成的資料流(Data Stream)去做傳輸。在一個理想的世界中,這些位元將可嚴格地在某個時間和存在於一個精準確預定的時間內。此外,它們將有均一的高和低的位準。

不幸的是,真實世界的情形與理想世界是有一段距離的,設計者須要克服很多種類的影響因素如抖動源,以確保傳輸資料的訊號品質。一般認為,抖動可以用一種高頻的量來表示。頻率低於10Hz的抖動行為被稱為「偏移」,更低頻率的抖動稱為「漂移」。

儘管它們在大型同步系統中是值得關注,偏移和漂移在非同步系統中扮演著的作用卻是微乎其微,因為它們很容易由時脈資料恢復裝置進行追蹤。非同步系統採用的是發射機和接收機獨立的參考時脈(Reference Clock)。在一個串列的接收器所需要的時脈頻率是從資料串流而來,其中位元轉換是被用於在一個時脈資料恢復裝置中的同步鎖相迴路 (Phase Locked Looped, PLL)壓控振盪器(VCO)所使用。

認識相位與振幅抖動

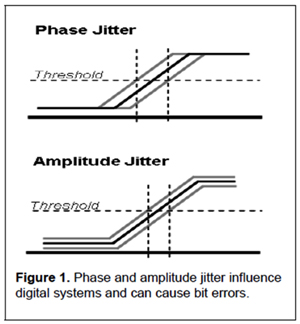

|

| 圖1 相位抖動(上)與抖動幅度(下)會影響數位系統,並可能導致位元錯誤。 |

相對於理想轉換時間的時序變化被稱為相位抖動(Phase Jitter)(圖1上)。訊號位準的變化也發生在數位系統,稱為抖動幅度(Amplitude Jitter)(圖1下)。

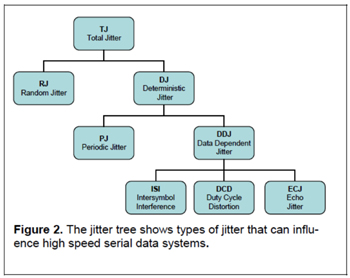

因為有限的訊號轉換時間,狀態的變化對系統的二進位制狀態判斷產生影響。在轉換之前取決於它的原始位準,該訊號的斜率到達門檻確定有些延遲或超前的實際位元狀態。再者,1或0的決定週期對於系統的影響是存在的,因為它總是取決於技術標準。抖動目前並沒有統一的定義,國際電信聯盟(ITU-I)抖動定義為:數位訊號從理想時間位置在極短時間內顯著的瞬間變化量(圖2)。

抖動可分為有界(Bounded)或無界(Unbounded)。前者是在系統事件內與頻率和振幅有關,因此有界的抖動是可決定性的(Deterministic),這也意味著切斷訊號源會將有關的有界抖動停掉。有界抖動總是有大小的限制。

|

| 圖2 抖動樹狀圖顯示某些類型抖動會影響高速串列資料系統 |

有個例子是符際干擾(Inter Symbol Interference, ISI),訊號的轉換造成相鄰通道的干擾,但是原始資料流如果沒有活動,就不會有干擾發生,如圖2中所示。

因為起始事件是有限的能量,因而導致抖動也是有限的,並且總是被衰減。無界抖動並不與事件相依,而是由系統元件或外部的影響所造成的。最為顯著的是隨機抖動(Random Jitter, RJ),一般是存在於主動與被動元件的白雜訊(White Noise)所造成。放大器和線路驅動器等裝置是用來做雜訊能量的倍增用途。由特性來看,白雜訊的能量是用高斯分布(Gaussian Distribution)來表示,所以隨機抖動可以由機率密度函數來做描述,如公式1所示:

.......公式1

其中,x是獨立的數值,而σ(Sigma)是均方根(RMS)數值,μ(Mu)指的是平均分布。抖動的定義是理想狀態的偏移量,這也就是說,它有相對理想狀態的正和負之偏移量,基於這個原因在抖動分析μ總是為0,並且可以省略。從公式1可以發現,不管多大獨立的x,都可能會造成某些事件的抖動機率變得非常小,但它永遠不會小到接近x軸。白雜訊的頻譜很寬,所以很難在不影響實際訊號的狀況下將其壓縮或衰減。

系統抖動是由多種訊號源造成的,或是隨機,或是可決定性。可決定性抖動的意思,很明顯地是與系統事件有關的原因所造成的。如上面所述,當在位準轉換或者從一個交換式電源供應器轉到Vcc網路上不完整過濾之切換脈衝的期間,這些原因作為例子可能會與相鄰的通道產生干擾。表1提供了抖動的起因之完整說明。

抖動測量 檢視眼圖/誤碼率

如何測量傳送或接收器之高速和分析資料的完整性串流?常用的方式是確定使用誤碼率來進行這個測量。已知的(虛擬)隨機位元串流注入到該待測物(DUT)。資料形式在待測物的輸出進行比較,並且可以做錯誤位元的計數。

BER=NErr/NBits .........................................公式2

在公式2中,BER為所測量的誤碼率,NErr錯誤位元和NBits比較位元的整個數目。這需要非常複雜的測量設備,允許每個位元的幅度和轉換時序的比較,並提供調整需要與待測物的訊號傳播延遲能力。在這理想條件下,可做為抖動相關測量的參考,被稱為單位間隔(UI),如公式3所示:

1UI=time period of 1 symbol

.............................................公式3

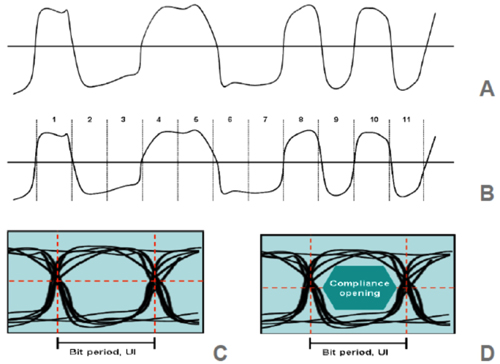

|

| 圖3 產生眼圖 |

特定位元的二進位制值,轉換時間和(差動)的振幅確定影響測量結果。專門用誤碼率測試(BERT)儀或示波器透過眼圖表示整個資料串流,所有已測量位元被顯示在同一時間。

同時,測量技術有可能是由於非常高的資料傳輸速度和相對低的訊號位準是相當複雜,產生眼圖的原理是很簡單的(圖3),在一個2UI窗口顯示一個很長地資料串流的眼圖行為。全部資料串流被折疊到該窗口。該眼圖允許可決定的訊號與該技術標準規定所要求的訊號的標準。眼圖C和D被延展在x軸的2.5倍是為更好的解析度。

在該範例中,一個資料流(A)在等額增加時被分解,I1到I11(B),每一個位元週期的大小,這代表的意義是每一個定義為1UI大小。至於允許最重要的訊號部分做詳細分析及轉換2UI為增量,5UI為預先轉換,1UI位元取樣和0.5的UI轉換後被記錄,並將重疊在2UI寬的窗口,其量測結果是如圖3C的眼圖。

一個資料位元位的理想的形狀將匹配在兩個恰好一個UI時間和幅度,而且在理想條件下的容忍邊際將幾乎是趨近1UI(-0.5UI的+0.5UI相對於位元中心),來識別訊號狀態正常。抖動來源的累計影響改變了訊號的幅度和轉換時間,這也顯著減少容忍邊界。

由表2可以知道,按照開放的敘述到底有多少訊號轉換和位準之前,允許從理想狀態發生變化時,它們會導致位元錯誤。為了有意義的決定通過/失效,技術標準提供精確的測試設定和必要的測量邊界描述。

表2顯示摘錄是為了這些需求的PCIe2.0、10Gb乙太網路和SATA II比較。有些格式允許超過50%的邊界,而其他嚴格得多。為了更多全面的資訊,可參考實際的技術標準。

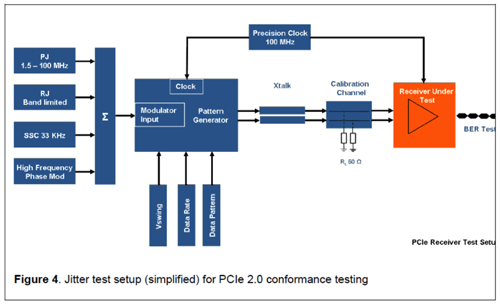

|

| 圖4 PCIe 2.0抖動相容性測試 |

圖4則顯示PCIe 2.0的抖動相容性測試串列接收器並簡化了測試設置。這個測試裝置其目的是揭露待測物的訊號條件,即由標準來定義的。一旦待測物的通過相容性測試,其確保硬體將工作正常,則其他組件也表示通過測試。

一個樣式資料產生器提供了一個已知的資料串流給待測物,對於同步系統而言,兩者待測物和樣式資料發生器具有相同精密時脈且被鎖住。若拿待測物的資料輸出與樣式資料產生器的誤碼率分析來比較。待測物強調的是透過改變訊號的幅度,透過不同的數據模式,並產生不同的數據傳輸速度。

值得注意的是,原始的資料串流加上調變方式不同,範圍從1.5M~100MHz可變訊號產生器產生週期性抖動的條件,另一個產生器固定在33kHz,可做為展頻時序的模擬。其中,訊號的轉換時間是透過相位和高斯白雜訊產生器,以及注入隨機抖動與頻譜分布的改變而得知。

最後在樣式產生器的輸出方案,符際干擾則是透過特殊的串音線路而產生出來。

(本文作者為Wireless Telecom Group公司Noisecom產品管理總監,譯者許國俊為筑波資深專案技術經理)