雙倍資料速率(DDR)記憶體測試包含由美國電子工程設計發展聯合協會(JEDEC)所制定的電氣和時序測試參數兩大類。然而,JEDEC標準並沒有規定該如何進行量測,僅提供了記憶體元件、動態隨機存取記憶體(DRAM)都須遵循的測試規範,以確保包括電腦、伺服器和行動裝置記憶體系統的相容性(Compliance)與互通性(Interoperability)。

若以手動方式測試這些參數極為耗時,因此現在很多設計工程師都利用示波器供應商所提供的自動化DDR相容性測試軟體來完成這類工作。隨著DDR記憶體的速度從DDR3到DDR4與更高的速度,深入進行除錯與特性分析的需求大幅攀升,自動化相容性測試所提供的合格/不合格資訊已經無法滿足這些需求了。

幸好,目前市面上已經有專為除錯與特性分析而設計的軟體工具,不但可以滿足這種需求,同時還提供能以更有效率的方式更迅速做好工作的除錯環境。接著,就來探討DDR除錯工具(DDR Debug Tool)須要具備哪些功能?

讀取和寫入資料的區隔

JEDEC規範定義的測試參數分為輸出和輸入週期,這代表使用者必須能區分讀取和寫入週期,以便針對正確的訊號進行量測。由於這個規範是為DRAM制定的,因此大部分的測試都是針對輸入(寫入)週期。DDR除錯工具首先須要進行的就是讓讀寫區隔能夠非常可靠。

大多數的測試演算法是利用Strobe觸發訊號(DQS)和資料(DQ)之間的相位差來判定這是讀取或寫入週期。讀取資料的訊號緣會與Strobe訊號對齊,而寫入資料則是中間位置與Strobe訊號對齊。當速度提升時,若要用相位差法準確偵測叢發訊號(Burst)可能不夠穩健,尤其是當系統原本就有嚴重的訊號完整性問題時。讀取可能被誤判為寫入週期(反之亦然),造成測試工具根據錯誤的量測而顯示測試結果為合格。

DDR除錯工具會進行標準的讀寫區隔,然後顯示讀取和寫入叢發訊號的開頭和結尾,以幫助使用者確認讀取和寫入週期的區隔結果如同預期一般。

統計分析多個叢發訊號

|

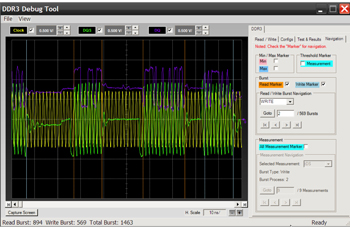

| 圖1 DDR除錯工具列出軌跡中所出現的讀取和寫入叢發訊號數量,同時標記還標示出叢發訊號的開頭和結尾。瀏覽功能可讓使用者針對儲存下來的時脈、Strobe訊號(DQS)和資料(DQ)波形軌跡,去瀏覽其中的每個叢發訊號。 |

為了以快速而有效的方式進行讀寫區隔,此工具必須要能瀏覽軌跡中的每個讀寫叢發訊號。DDR除錯工具也會顯示有效叢發訊號總數以及軌跡中出現的讀取和寫入叢發訊號數量。如此就能讓設計工程師決定是否要增加系統的運作,以便為除錯或特性分析工作取得更多資料(圖1)。

JEDEC規範並沒有規定必須量測的叢發訊號數量。以往大多數的設計工程師只測試一組叢發訊號來判斷系統能否通過相容性測試,而能不能通過測試,取決於系統承受多大的壓力。設計工程師可以增加資料傳輸量進行測試,在某些情況下,他們發現系統的餘裕較小。

現在幾乎每個記憶體設計者都會進行邊限測試(Margin Testing),他們不再只是關注DDR自動相容性應用軟體所提供的Pass/Fail資訊而已,也想要對訊號執行統計分析,進一步了解其設計是否有足夠的餘裕可以超越規範中所規定的性能範圍。

|

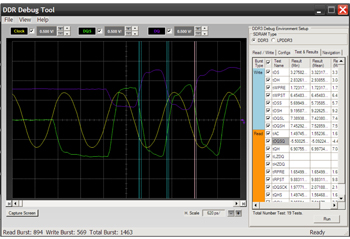

| 圖2 JEDEC量測的測試結果會附上最小值、平均值和最大值的統計報告,方便使用者在進行邊限測試時更有信心。統計報告可以匯出到一個.csv檔作進一步分析,也可以用來作成報告。 |

為了達到這個目的,設計工程師必須盡可能蒐集更多的統計資訊。若能對叢發訊號進行更詳細的分析,那麼對邊限測試的結果將更有信心。DDR除錯工具必須以最快的方式針對發現到的所有叢發訊號量測其全部的測試參數,這樣才能夠加快測試時間。

由於DDR除錯工具是針對示波器所儲存的波形檔或是存下來的相容性應用軟體專案檔來執行,因此示波器毋須為了量測而進行資料擷取或是將波形縮放至最適大小,這種方式可大幅縮減測試時間。測試結果可以匯出到一個.csv格式的檔案做進一步分析或者用來製作報告(圖2)。

另外,在邊限測試中,設計工程師還需要一種方法,可以在改變工作電壓時,仍可按照JEDEC規範以對應的參考電壓以及交流電(AC)和直流電(DC)輸入與輸出量測位準進行量測。

|

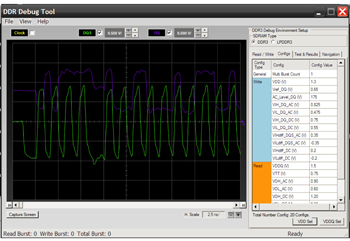

| 圖3 當使用者將1.5伏特的DDR3工作電壓(JEDEC規範中的定義)改為1.3伏特以測試系統在低功耗模式的效能時,就會產生新的量測臨界值。DDR除錯工具依據JEDEC規範中的公式自動計算1.3伏特工作電壓下的交流電和直流電量測電壓位準。

|

舉例來說,DDR3標準的工作電壓為1.5伏特(V),在邊限測試時,使用者可將電壓降低到1.3伏特,看看系統能否降低功耗;此工具會自動計算新的量測電壓位準,然後所有的量測(圖3),會依照新的量測臨界值來進行。DDR除錯工具的自動計算功能可以幫使用者平順地轉換新的交流電和直流電電壓量測臨界值,不但縮減測試的設定時間,也不再須要另外查閱JEDEC規範中的公式。

進行JEDEC量測

DDR除錯工具所執行的量測是依照JEDEC規範來進行,其中的測試可分為電氣、時序和眼圖測試三大類別。在這些測試類別中,個別測試會按照輸出(寫入)和輸入(讀取)週期來區隔。此工具將所有測試以讀取或寫入週期來分類,讓使用者在選擇測試項目之前不必再查閱JEDEC規範。

為了讓除錯工作更有效率,DDR除錯工具使用標記來標註軌跡中出現的所有有效量測,並標示電壓和時間的量測臨界值。為了幫助使用者把心力集中在問題區塊,此工具並標示測試結果中出現的最小和最大量測值。使用者也可以瀏覽每一個量測以確保所有的有效叢發訊號都已經量測過。DDR除錯工具也會列出有效量測的數量。有些系統的資料傳輸量很小,因此即使出現很多讀寫叢發訊號,但假如叢發訊號中並沒有傳送夠多的資料,就會欠缺用於進行統計分析的有效量測。

舉例來說,假如對叢發長度(Burst Length)為8的兩組叢發訊號量測設定時間tDS,可能會發現只有九個有效量測,因為在這兩組叢發訊號中資料只傳輸九次。如果叢發訊號的每個位元都有傳輸資料,可獲得十六個有效的tDS量測。儘管所有這些功能在傳統的DDR相容性測試軟體中可能已經是標準配備,但是DDR除錯工具加入了視覺化功能,可以幫忙教育使用者,同時也讓他們更有信心量測結果確實是正確的。

|

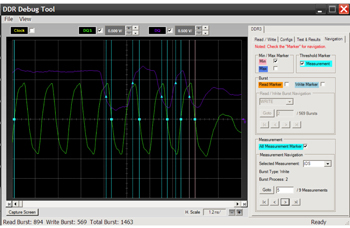

| 圖4 量測標記可在寫入週期標註設定時間tDS的量測,標示出依據JEDEC規範的AC DC電壓量測臨界點。還能將具有波形、標記和量測臨界點的螢幕截圖存下來用來做成報告。 |

顯示標記和量測臨界值的螢幕畫面還可以擷取下來用於製作報告。由於波形檔的載入是來自於之前儲存的波形檔,無論是預先設定好示波器的訊號擷取,還是相容性測試應用軟體儲存的軌跡,因此時間和電壓的刻度就毋須做任何調整,可以完全依照使用者的喜好,以製作報告的觀點進行最佳化(圖4)。

提升記憶體設計品質 除錯工具不可或缺

總結來說,由於現今的記憶體技術(如DDR4)在速度和能源效率上有顯著的提升,相容性測試工作須要更深入進行除錯與特性分析工作,這種不斷增加的需求已經改變了記憶體設計工程師的測試架構與環境。僅提供Pass/Fail資訊的傳統DDR相容性測試軟體已經無法用快速而有效的方式支援這些新增的工作。

目前市面上已經有專業的全新DDR除錯工具出爐,可針對JEDEC量測提供統計分析結果,同時具備瀏覽功能以及可標示問題區塊的標記功能,讓記憶體設計工程師能以更快速的方式專注在問題區塊,並且對測試結果具有更充分的信心,尤其是邊限測試。

除此之外,DDR除錯工具還必須具備方便除錯的環境或架構,利用直覺式操作介面來省下設定時間進而加快測試速度,如此一來即可有效幫助記憶體設計工程師縮短測試時間,最終亦可節省整體產品設計與測試成本,並達到率先在市場上推出產品的目標。

(本文作者任職於安捷倫)