將定點及浮點功能整合於同一個數位訊號處理器(DSP)核心能夠徹底改變嵌入式系統演算法的開發及部署方式。在定點數位系統中執行演算法的程序相當繁複,無法因應目前快速的浮點DSP對於速度的需求。然而,運用全新的DSP浮點運算功能,便不再須要進行如此繁複的程序。

位元數/格式影響數字準確

包括德州儀器(TI)的DSP在內的所有數位處理器都是以一系列位元(0與1)的二進位表示數字。數字的準確度會因為使用的位元數及呈現的格式而有所不同。定點系統使用位元來表示整數或含整數及分數位元定點數等值的固定範圍,值的動態範圍受到局限,而且設定範圍以外的值必須以端點為限。

定點處理器通常可達到每秒16位元的效能。為了完全達到此效能,針對這類處理器開發的演算法必須運用預先定義範圍內的資料集。無法預期或變化過大的資料集無法在定點執行中達到良好的效果。

浮點表示法使用假數(或有效數字)及指數等科學記數法表示數字,因此能夠提供動態範圍。C66x核心可進行單精度浮點運算,其中的數字以32位元表示為(-1)5×M×2(N-127),其中S是正負號位元,M是假數或有效數字,N是指數。S為1位元,N以8位元表示,M以23位元表示。因此,在2-127-2128範圍內的數字能夠以24位元精度的有效數字表示。

不同於浮點表示法,16位元的定點演算法只能夠表示216值的範圍如數字0~65535,數字的動態範圍較小。因此,資料集或處理資料集的演算法無法預期或動態範圍變化過大時,較適合使用浮點表示。另一項重點是,有效數字的第一位數固定為1,因此數值可固定維持24位元的精度。

將定點及浮點整合於單核心

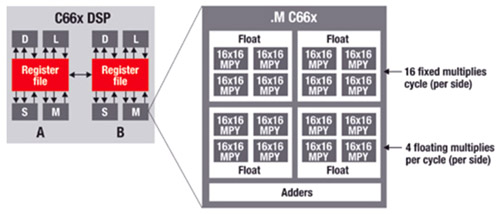

圖1顯示德州儀器全新的C66x核心,其中的基本A及B結構與C64x+核心相同。必須注意的是,.M單元已擴充為各個功能單元十六個16位元乘數,因此可達到核心原先運算能力的四倍效用。C66x DSP的突破性創新使得四個乘數的各個叢集能夠共同實作單精度浮點乘算。

|

| 圖1 德州儀器C66x DSP核心 |

C66x DSP核心最多可以有八個浮點乘算同時進行,各個核心的時脈頻率可達到1.25GHz,因而成為市場上效能最高的浮點DSP。結合多個C66x DSP核心可製作出絕佳效能的多核心系統單晶片(SoC)裝置。

為達到定點及浮點的絕佳效能,德州儀器已針對此款全新C66x核心開發全新的浮點及定點指令,能有效發揮無線訊號處理的效能。使用浮點表示法時,由於運算複雜度相當高,因此採用個別的定點及浮點處理器。對於定點而言,加法及乘法之類的基本運算相當直接而容易實作。對浮點而言,如此基本的運算需要較多的處理作業。以下列兩個浮點數相乘為例:

(M1×2N1)×(M2×2N2)=(M1×M2)×2N1+N2

必須注意的是,指數須要相加,假數須要相乘。得出的(M1×M2)值須調整為23位元,這須要一併變更指數值。對於使用浮點進行的所有基本運算而言,需要一些額外的作業,因此浮點運算變得更加複雜,這正是為何許多演算法僅使用定點表示和定點運算的原因。嵌入式處理器能夠以更快的速度執行定點運算,並且通常只需要定點演算法即可進行運算。例如,C66x DSP核心能夠執行十六個定點乘算,也就是一回四個浮點乘算的週期。

將浮點演算轉換為定點

雖然DSP執行定點處理的速度比浮點處理快,不過部分演算法的開發時間較長。通訊系統的一般設計流程是先根據電腦機型開發演算法,然後用於初始系統部署。隨著部署的範圍和運用不斷擴大,工程人員須要收集實際資料進行實驗,才能調整演算法以提升系統效能。這些全新的演算法通常是以MATLAB或其他浮點運算工具進行開發。

其中的難題在於將這些浮點演算法轉換為定點,同時維持演算法和系統兩者的效能。因為不靈活或複雜的演算法會用盡系統資源,而降低系統的整體效能。如果涉及複雜的處理,將程式碼從MATLAB導入實際系統通常需要幾週或幾星期的時間。透過德州儀器全新架構的原生浮點支援,便毋須進行從浮點轉換為定點的整個程序。使用C66x DSP的浮點指令並直接編譯於DSP,即可從Matlab之類的工具導入程式碼。

原生浮點提升4G效能

無線電話逐漸演化為複雜的媒體平台,需要大容量的資料傳輸空間才能支援串流視訊及其他大頻寬應用。基地台中全球微波存取互通介面(WiMAX)及長程演進計畫(LTE)等新4G技術能夠為使用者處理更多的資料,而且使用多天線訊號處理提升多重輸入多重輸出(MIMO)及波束形成等運算的效能。這些演算法一般需要逆矩陣技術(Matrix Inversion Techniques),不過這種技術一般會有定點處理方面的量化及縮放問題。針對浮點執行,這些演算法可提升系統的速度和準確度,使效能得以改善,為手機使用者帶來更佳的體驗。

由於各個基本運算的時間較長,使得浮點處理的時間較長,不過這對於演算法需要大動態範圍進行運算的情況不適用。在4G處理的逆矩陣運算中,無法直接使用定點運算,所以在無任何原生浮點支援的定點處理器上執行的演算法基本上會強制模擬浮點。由於處理器未運用定點功能,因此,相較於使用支援浮點運算的處理器執行的情況,這些演算法的速度相當慢。

C66x DSP上的原生浮點能夠解決如此效能不彰的問題。例如,C66x DSP核心執行MIMO及其他主要多天線訊號處理演算法的速度,比C64x+ DSP的定點功能執行時快四倍。浮點能夠直接從MATLAB使用程式碼,這不僅能縮短開發時程,而且相較於定點程式碼如大型快速傅立葉轉換(FFT),許多演算法的浮點執行均使用較少的週期。

C66x核心能夠讓DSP型嵌入式處理器及系統單晶片發揮創新效用,完全毋須在定點處理器或浮點處理器間抉擇。如此革命性的進展將徹底改變即時性系統的演算法開發方式,讓系統開發人員能更快速且輕鬆地製作出與眾不同的全新解決方案。

(本文作者為德州儀器通訊基礎設備事業部策略行銷協理)