1831年,法拉第(Faraday)發現在一定的時間內穿過線圈的磁通量變化越大或磁通量變化速率越快,感應電動勢就越大,否則就越小。也就是說,每單位時間線圈內磁通量的變化越大,感應電動勢就越大。

上述的現象即為Faraday定律,再經過10、20年左右,Maxwell把這三個現象整理出四個方程式(Equations)(公式1),這就是有名的Maxwell's方程式,最後就變成整套的電磁理論。

................公式1

這四個方程式,兩個是關於電場的散度(Divergence)和曲度(Curl),另外兩個是關於磁場的Divergence和Curl。所有的電磁現象如日光燈的發亮、收音機等等,全部可以用這四個方程式來解釋。這四個方程式是由先前的三個現象導出來的,導的過程主要是利用Stokes'和Gauss定理,還有一些向量的計算。

導出這四個偏微分方程式後,剩下的問題差不多就是數學家的問題。其中第一個方程式與庫侖定律有關,第三個是和Faraday定律有關,剩下的兩個則與Biot-Savart定律有關。前面兩個式子很容易可以用Stokes'或Gauss定理導出,比較麻煩的是由Biot-Savart定律導出另外兩個公式,這裡要稍微提一下,Biot-Savart定律並不完全等於這兩個公式,這中間還有一些需要討論,所以在這三個實驗現象和Maxwell's方程式之間還有一些東西需要補充,補充這個部分的人當然就是Maxwell,所以這些方程式一般就叫做Maxwell's方程式。

為何在此提出Maxwell's方程式,因為其解釋了磁生電、電生磁的效應。今天不會利用上述公式來導引印刷電路板(PCB)產生的電磁干擾問題,但希望從幾何圖形方式來講述電磁相容(EMC)如何引導及隔離。就像工程蓋水霸時,需精密計算結構強度及現場土質以利其分析。

認識電磁相容

EMC全名為Electro Magnetic Compatibility,通常又翻譯成「電磁相容」。在國際電氣標準協會(IEC)的定義中為對任何的東西而言,不給其無法容許的電磁干擾波,且在電磁環境中還需能具有滿足其功能的機器、裝置或系統的能力。

電磁相容又等於電磁干擾(Electro-Magnatic Interference, EMI)加上電磁耐受(EMS)電磁相容定義的電磁干擾源,以及後半段的電磁干擾環境,都可以稱之為電磁雜訊(Noise),成因主要分為以下兩種:

| ‧ |

(Conducted Emissions) |

| |

干擾波的電磁能量主要是經由電力線和訊號線等的導體而被傳達,侵入其他裝置給予的干擾者。 |

| ‧ |

|

| |

干擾波的電磁能量以電磁的形態傳播至被放射的空間,對其他的裝置給予干擾者。 |

另外,電磁干擾波又可依時間波形而分為連續的干擾波(長時間的連續干擾)和過渡的干擾波(波形急速的變化,在短時間干擾者)。

當想到發射(Emission)時,第一條守則是頻率(Frequency)愈高,則可能是幅射耦合之路徑;頻率愈低,則可能是傳導耦合之路徑。

何謂電磁干擾

|

| 圖1 電容器的示意圖 |

電磁干擾產生的過程中,有許多的變數,這是因為電磁干擾是被動元件正常狀態行為以外的結果。首先,從印刷電路板的布局(Layout)的各項組件來說明。

例如電容等效特性由兩導體中間有絕緣物構成,如圖1所示的電容器示意圖及公式2的等效電容值公式,兩導體因接通交流電時,由於電容充放電所致,除非另外導體為無窮大的地,可以忽略其高頻響應,不然其與路徑上的電感形成如圖2所示的電感器示意圖及公式3的等效電感值公式。

|

| 圖2 電感器的示意圖 |

..................................公式2

......................................................公式3

下列有幾種記憶方法可協助在印刷電路板走線時快速地分辦其等效特性:

|

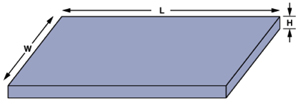

| 圖3 印刷電路板貫孔的電容及電感效應值公式 |

對於印刷電路板貫孔的電容及電感效應,傳輸線在換層時也能參考到同一接地層,且板子薄一點較好,而線寬大於等於貫孔直徑時,貫孔所形成的阻抗不連續性幾乎消失。圖3為其等效特性、電容及電感值公式。

貫穿孔的影響可分為兩方面,它的電容效應會延遲訊號0與1之間的變化,也因此增加訊號的傳導時間,而其電感效應則會削弱,如旁路電容(Bypass Capacitor)的效用。對多數的應用而言,這樣的電感還不至於造成太大的影響,但旁路電容若是接到電源層與接地層各需一個貫穿孔,其影響又會加倍。無論如何,盡量將旁路電容靠近需穩壓的元件,並盡可能地多打幾個貫穿孔以減少阻抗是正確的做法。

這些特性稱之隱藏電路。數位工程工師一般假設這些元件有單一的頻率響應結果,其根據時域的功能特性來選擇元件而不管在頻域裡的實際表現,則電磁干擾的情形就表現出來。

必須注意的是,上述等效電路適用於走線(Trace)的路徑遠少於訊號波長(l <<λ),如果頻率超過微波須按照微波的微帶傳輸線(Microstrip Transmission Line)來設計並須考慮阻抗匹配。

疊構分層考量

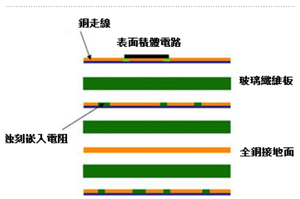

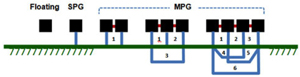

|

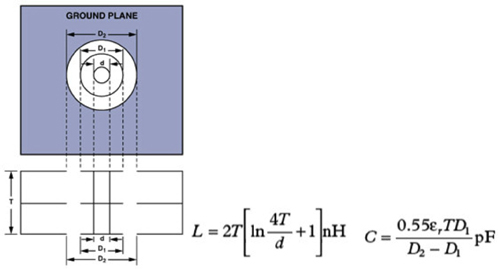

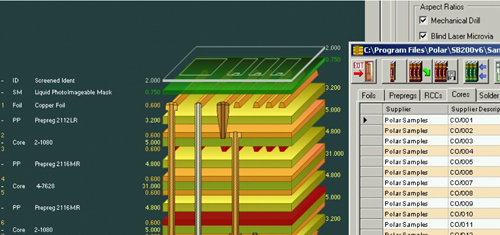

| 圖4 一般印刷電路板堆疊(Stack Up)示意圖 |

印刷電路板的疊構分層,須視整體線路功能分布及成本做考量,一般電源器採用二層板,其板厚因考量磁性元件而採用較厚的印刷電路板(圖4)。

| ‧ |

|

| |

二層板有兩種的布局技術,一種是較老的技術,適用於較低速之元件,一般包含雙列直插式(DIP)包裝的元件成排或成矩陣狀排列,現在已經很少使用。

第一種方式是將電源(Power)和接地(Ground)以格狀布局,使形成之每一格總面積小於1.5平方英寸。Power和Ground之走線以90℃角分布。Power在一層,Ground在另外一層。Ground走線置於頂層,垂直走向。Power走線置於底層,水平走向在每一個Ground和走線交接處,放置解除耦合(Decoupling)電容。

第二種方式通常用於低於10kHz低頻類比設計。將Power走線在同一層布線層幅射狀拉線,由電源處接至每一元件,減少走線的總長度。將所有Power和Ground走線相鄰布線,使得由來自高頻切換雜訊的環路電流最小,因而不會衝擊其他電路和控制訊號。這些走線會分開的唯一情況是,當連接到解除耦合電容時。訊號流向應和Ground路徑並行。避免不同樹枝互相交錯,以免造成接地迴路。

低頻寄生電感及電容通常不會產生問題。在此情況下,建議可採用單點接地的方式。換句話說,在低頻的應用上,藉布局達成之高頻表現。但注意以下兩點,高頻時,控制訊號路徑和其回返電流路徑之表面阻抗,也就是回歸路徑(Return Path)要越少越好。而在低頻時,可以依據走線特性及路徑來控制布局的形狀而非阻抗。 |

| ‧ |

|

| |

|

由此可得知,當有多於三個完整平面提供時(即一個Power Ground)將最高速時鐘(Clock)布線於相鄰接地層(Ground Plane)且不相鄰於電源層(Power Plane),可得最佳電磁干擾效果,此為在印刷電路板上電磁干擾抑制的基礎觀念。

多層板可提供優良電磁相容之訊號品質,因為經由微帶線(Microstrip)及帶狀線(Stripline)可有效佳之訊號阻抗控制。電源及接地層之分布阻抗(Distribution Inpedance)應盡可能地降低。這些平面含有來自於邏輯交錯(Logic Crossover)之極短暫的突波電流、訊號及匯流排的電容負載。

微帶線及帶狀線應用之主要意義在於磁通量之互相抵銷。使得傳輸線之電感降低。多數的邏輯族在其上拉(Pull Up)/下拉(Pull Down)電流可能極不平均,此使得磁通抵銷(Flux Cancellation)的效果在訊號與接地層之間比訊號及電源層之間要好。因此,使用電源層做磁通量抵銷不能達到最佳的效果,結果會導致訊號通量相位偏移增大電感、不良的阻抗控制以及雜訊不穩定,所以應使用接地層為佳。

| ‧ |

|

| |

六層板有三種方式,第一種方式有最佳的電磁干擾特性,對所以布線層有較好的磁通抵銷,其分布如下:第一層為元件面(Component Side)、微帶線訊號布線層,第二層是接地層,第三層為帶狀線、布線層(下跟著填充物質)。第四層是電源層,第五層為接地層,以及第六層的焊接面(Solder Side)、微帶線訊號布線層。

第二種為對時鐘和高頻元件,是較常用的方式,其分布為第一層為元件面、微帶線訊號布線層,第二層是接地層,第三層為帶狀線,第四層為帶狀線,第五層是電源層,至於第六層則是焊接面、微帶線訊號布線層。

第三種方式則有較佳的電磁干擾特性,因為在Ground及Power平面間有較好之層間(解除耦合)。其第一層為元件面、微帶線訊號布線層,第二層為埋入微帶線布線層,第三層是接地層,第四層為電源層,第五層則為埋入微帶線布線層,以及第六層的焊接面、微帶線布線層。 |

| ‧ |

|

| |

|

| 圖5 八層板的疊構示意圖 |

八層板的疊構示意圖如圖5所示,有兩種方式,第一種組態提供較少的磁通量抵銷,第二種組態因為有較多的完整平面,提供最大的磁通量抵銷。考量因素包括布線之NET數量、元件密度、匯流排結構大小、類比和數位電路,以及可用的面積。

第一種方式因為在電源及接地平面有較差的磁通量抵銷,因此是較差的堆疊方式,其有六層布線層。第一層為元件面、微帶線訊號布線層,第二層是埋入微帶線布線層,第三層為接地層,第四層為電源層,第五層是帶狀線布線層,第六層是帶狀線布線層,第七層為埋入微帶線布線層,而第八層是焊接面、微帶線布線層。

第二種方式則對射頻電流有較緊密的磁通量抵銷,是較佳的堆疊方式,其有四層布線層和四層平面,分布方式如下:第一層為元件面、微帶線訊號布線層,第二層是接地層,第三層是帶狀線布線層,第四層是接地層,第五層為電源層,第六層是帶狀線布線層,第七層為接地層,第八層則為焊接面、微帶線訊號布線層。 |

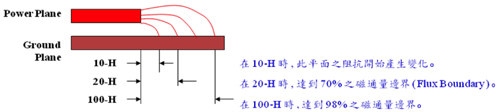

了解20-H Rule法則

|

| 圖6 電源與地層布銅20H示意圖 |

20-H Rule法則是由W. Michael King於1980年所提出來,透過大地層面大於電源端吸收電源端的幅射能量,射頻電流存在於電源層之邊。此種層間耦合稱之邊際(Fringing),通常僅見於高速的印刷電路板,當使用高速邏輯及Clock時,電源平面間會互相耦合射頻電流且幅射至空中,若要減低效應,所有電源平面要比相鄰的地平面小(圖6)。

考量元件放置

印刷電路板布局之前應先注意將元件放置(Placement)至適當的位置,一方面須考慮電路板外部接線端子的位置,另一方面也須考慮不同性質的電路應予以適當的區隔。類比、高速數位及雜訊電路(繼電器、高電流開關等等)應加以分隔以降低子系統間的耦合。在規畫線路時就應該依功能區隔大地及適當的隔離。

當放置元件時,應同時考慮子系統電路之間的內部電路繞線,特別是時序及振盪電路。為了去除電磁干擾的潛在問題,應系統化地檢查元件放置與線路布局,反覆檢視及修正布線,一直到確定所有的電磁干擾風險降低到最低為止。簡而言之,事先的防範是將低電磁干擾問題的首要原則。

留意數位電路的雜訊與布線

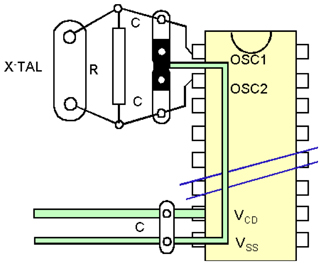

|

| 圖7 石英或陶瓷共振電路的線路布局 |

如何降低內部雜訊是數位電路板布線的首要考量因素。在微控制器(MCU)為主的系統中最敏感的訊號是時序、重置和中斷線路,振盪器在開機時尤為敏感。千萬不要將這些線路與高電流開關線路平行,如此容易被電磁交互耦合訊號破壞。此效應容易破壞微控制器經由中斷碼的執行,引起非預期的重置或中斷。時序訊號受到干擾,將造成失相(Lose Phase)使整個系統失去同步,由於微控制器的執行是依據適當的時鐘脈波,因此不要期望它們能在電磁干擾的干擾下恢復正常操作。

振盪器或陶瓷共振時鐘是一種射頻電路,必須繞線以減少它的發射位準及敏感性。圖7以一個振盪器或陶瓷共振器與DIP包裝為例來說明,盡量將振盪電路的配置靠近微控制器,若是振盪器或陶瓷共振器的本體很長,就放在印刷電路板之下並將包裝接地。如果振盪器在印刷電路板之外,就將微控制器放在離印刷電路板連接器的附近。不然,就將微控制器盡量擺近振盪器以縮短繞線距離。振盪線路的地線應該連接元件可能使用最短繞線的接地腳位,電源和接地腳應該直接繞線到印刷電路板的電源部分。

注意類比電路的雜訊與布線

線性訊號容易受到數位訊號的干擾,所以類比和數位訊號必須隔離以確保線性訊號品質,如果因為空間或者晶片限制須混雜,要確保彼此的路徑採相交,降低交互耦合(Cross Coupling)的效應。

如果類比電路的參考訊號未與數位線路隔離,類比數位轉換器的訊號會受到嚴重的干擾,因此不可將數位電源和接地直接輸入類比數位轉換器的參考訊號線路。這些腳位應直接從電源端之參考電壓來著手。

接著,說明接地的方式。電子設備的設計關鍵在於具有強韌與可靠的電源系統,而接地布局尤為關鍵。一般訊號接地種類有單點接地和多點接地,以下分別說明。

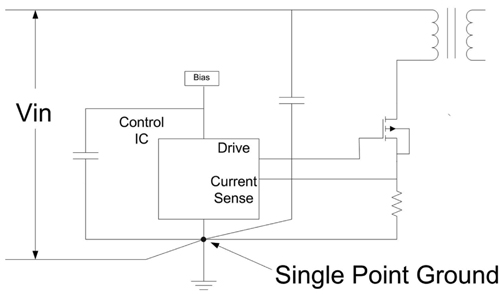

| ‧ |

|

| |

|

| 圖8 單點接地示意方式 |

單點接地在高頻的時候會有一些危險,因為走線在高頻時會表現電感的特性,使得高頻的阻抗升高,而且接地線會產生電感性干擾的問題,如果頻率很高,這些接地導線可能形成天線將雜訊幅射至外面。所以,如果採用單點接地,接地線必須盡可能地縮短,使其高頻的阻抗變低,才不易形成天線。

當元件電路和訊號在1MHz以下的時候,單點接地是最好的選擇,圖8說明了單點接地示意方式。

而較高之頻率,Power平面和走線的阻抗變得不可忽略。如果走線的長度等於或接近訊號的四分之一波長,此阻抗會非常地高。須注意,只要是走線或Ground導體具高阻抗,它就會像天線幅射射頻的能量,所以在1MHz以上的頻率,建議直接對地。

應用單點接地的訊號通常以幅射狀傳遞,相關產品包括音訊電路、類比儀器、60Hz和直流電源(DC Power)系統。 |

| ‧ |

|

| |

|

| 圖9 多點接地 |

高頻產品(10MHz)設計通常使用多點接地,將射頻的電流並聯由接地層機殼接地,可減低由印刷電路板電源平面所看出來的地阻抗來降低回歸路徑電感效應。亦即電路盡量找最接近的低阻值面接地,因為大的接地面有較低的電感值,所以其高頻阻抗也較高。所以,完整平面之低電感特性造成低的平面阻抗。在高頻電路上,走線的長度使電路上電感增加,約每吋15~20奈亨(nH),因此愈短愈好。

除了平面中之電感外,長的走線同時也像是天線一般,特別是對時鐘訊號和其他同期性脈波而言。將走線電感降低及減少走線造成的射頻電流,可以達到良好的訊號品質和射頻壓制。圖9所示為多點接地示意方式。

不過,從系統面來看多點、單點或是混合使用,端視其功能及頻率而定,因頻率高時,其路徑的等效影響越大,需要最適當的路徑來接地。 |

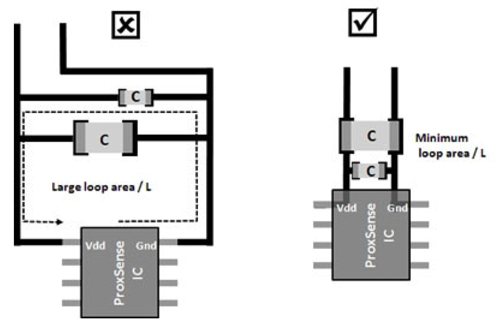

電源線布局與解耦

|

| 圖10 數位IC解耦電容的安置與布線 |

印刷電路板的地線布局完成後,接下來是電源線的布局。若空間許可,電源線應與地線平行,但從實際觀點而言,此點未必可行。電源線的雜訊通常可藉由適當的電源濾波電容與解耦電容將之濾除。

網狀的地線(或接地平面)較網狀的電源線更為重要,因此布局時,應優先考慮地線的布局,其次再考慮電源線的布局。以下說明一些電源線雜訊抑制的方法。

印刷電路板上的邏輯閘開關時,在電源線上會產生暫態的脈衝電流,由於電源線多少具有微小的電感性,如圖10(a)所示,因此在電源端產生雜訊干擾。電源線的電感可藉由多層印刷電路板(電源平面)來降低,或使用較慢的邏輯降低開關的速度,但前者將增加成本,後者則會降低系統的性能。在使用雙層印刷電路板的前提下,電源線的雜訊干擾可藉由解耦電容來降低。

印刷電路板的解耦電容可分為兩類,一類是置於IC旁的削尖電容(Despiking Capacitor),另一類則是置於電源端的大型解耦電容(Bulk Decoupling Capacitor)。IC旁的削尖電容其特質為容量小、頻寬高,目的在於提供IC開關時的瞬間脈衝電流。但這些電容也須補充瞬間所損失的電荷,這就必須藉由印刷電路板電源輸入端的大型解耦電容來補充電荷,其等效電路如圖10(b)所示。

電源端的大型解耦電容其數值雖然不是非常關鍵,但至少應十倍於所有IC削尖電容的總和,也應放置於印刷電路板的電源輸入端。IC電源端須考量其最大的頻率響應再加註適當的值以降低電源的回響。

排除電磁干擾

在印刷電路板布局處理電磁干擾有兩種方式,一種是隔離,另外一種則是導引,上述討論的原則是引導,但因目前空間有限,再加上混雜訊號,還是有很強的能源幅射出來。首先必須善用工具,尤其善用手中的示波器、近場天線及頻譜儀找出雜訊源,在無法確認源頭時善用磁珠(Bead)或電感來隔離可能的雜訊源。找到源頭時大概有兩種方式,一則阻抗匹配,二則使用RC線路抑止能量。後者須考量其波形是否符合功能訊號規格。

另須注意,一般傳輸線末端若不加一個匹配阻抗,將產生訊號回響,造成訊號不準。特性阻抗就是在傳輸線末端加上的匹配阻抗值。加上後,此有限長的傳輸線對訊號而言是延伸至無限長,就不會回響。

簡述電磁干擾耦合路徑

了解雜訊如何傳輸,有助於辨識電路內部的電磁干擾問題。雜訊的發生必須要有來源、耦合路徑或放大器,以及易感染的接收器(Susceptible Receptor)。

雜訊耦合到電路內的方式之一是透過電導體。假如訊號線經過一個充滿雜訊的環境,訊號線將受感應拾取雜訊訊號並傳至電路的其他部分,例如電源供應器的雜訊就會經由電源線而耦合至電路。

雜訊的耦合也可經由電磁輻射的方式發生,此種狀況會發生在所有具有共同輻射電磁場的電子電路。電流改變就產生電磁波,這些電磁波會耦合到附近的導體並影響電路中的其他訊號。

系統設計初始 解決電磁相容

電子設備的電磁相容性,應被視為系統規格來預先考慮而非事後補救。一個電子設備如果與環境不會相互影響,即具備電氣相容性。如果設計工程師未能在設計初期慎重考慮此一問題,那麼雖然因忽略電磁干擾設計而縮短設計時間,並且完成功能測試而量產,然而在產品上市後,不明的電磁干擾現象就非預期地出現了。這種產品危機的解決方法通常會受到相當的挫折,增加不必要的虛耗及產品後續改善時間的延長,其結果常導致產品的失敗。

電磁干擾的防治雖然有很多方法,但主要可歸納為降低電磁干擾的散布與提高增電磁干擾的免疫能力兩種不同型式。經由適當的系統設計,可以抑制電磁干擾的散布,如果問題仍然持續,就得研究不同方式的遮蔽去包住發射體。電路對雜訊的敏感性可藉由電路設計的加強,以及使用遮蔽物來降低電路對電磁干擾敏感性。

數位電路的設計,若能從布局階段就謹慎地規畫,測試時又能對重要訊號詳細測量,相信做出一塊執行穩定的電路板不會是問題。記住一些基本觀念,例如減少電源路徑的阻抗、讓訊號線阻抗匹配、盡量讓訊號線之間的間距加大、盡量讓訊號線走直走短等等,就不會犯下太大的失誤。

(本文作者任職於四零四科技)