隨著資料轉換器和FPGA持續使用更先進且更小的幾何製程尺寸,新的資料介面挑戰便主動向系統設計人員來報到。更小的製程尺寸可得到頻寬更高的轉換器,可提高解析度和速度,二者均驅動更高的資料傳輸量。

然而,他們也可以做成更高的串列/解串列(SerDes)速率以因應頻寬的消耗,這是在大的製程尺寸下不曾做過的。此外,較小的占位面積也讓更多資料轉換器得以整合到單一元件中。這些資料轉換器的介面解決方案要具有高資料率,能夠與更加複雜的FPGA元件相容,還要維持合理的輸入/輸出(I/O)數量。

JESD204B介面是一種轉換器的SerDes鏈接規格,允許資料以每秒最高12.5Gb(10億位元)速率傳輸。藉由使用先進的製程節點,如採用65奈米(nm)甚至更精細製程加上提升省電效率,讓轉換器得以達成最大資料速率。12.5Gbit/s的通道速率可幫助系統設計人員完全利用此一SerDes新的技術優勢,更勝於另一種LVDS雙倍資料率同步動態隨機存取記憶體(DDR)介面。

有一些開放市場上的FPGA型號提供資料速率達到甚至超過12.5Gbit/s的串列收發器。其實FPGA具備這樣能力已有一段時間,如今,轉換器能夠有相同的SerDes性能,都是由於在設計中使用更小的製程節點,使得多重轉換器的同步處理,或加上多個內部通道,都可以全部裝進單顆FPGA元件內。

允許交流耦合 JESD204B比LVDS更具吸引力

當資料轉換器的高速串列傳輸時代來臨,在選擇差動訊號技術用於不同應用上,有不同的選擇。資料轉換器廠商選擇LVDS做為主要的差動訊號傳輸技術已有10年以上。雖然在一些LVDS的應用可以提高資料速率,但是目前市場上轉換器廠商可提供的最大LVDS資料速率為0.8G~1.0Gbit/s。

LVDS技術尚未跟上轉換器的頻寬需求,該技術是由TIA/EIA644A規格所控制,這是一種工業標準,引導LVDS晶片製造商遵循指導方針,扮演設計人員的最佳實踐指南,促進不同廠商間LVDS傳送器和接收器的相容性。如果設計人員不完全遵守LVDS的規格去生產不相容的產品,那麼產品在市場上的相容性將面臨更大的挑戰。

LVDS和JESD204B都有標準組織,在電氣和物理要求下提供指導方針給各個不同的廠商,以達到互通性。JESD204B最大資料速率被定義在12.5Gbit/s,相較於現行的LVDS,它達到的傳輸量超過十倍以上,且該轉換器使資料轉換器系統降低了對I/O的要求並縮小封裝尺寸,同時以較低的靜態功率顯著節省系統成本。

此外,JESD204B規格允許交流耦合,能相容不同的技術節點與使用不同的供應電壓,通常在製造技術最前端的28奈米及更小的FPGA製程節點。

JESD204B對於高解析度和高速資料轉換器製造商而言是一種非常有吸引力的差動訊號技術,因為轉換電晶體節點往往落後於FPGA的技術幾個世代,導致需要客製化類比設計,而LVDS通常使用直流耦合的策略,這使得轉換器到FPGA介面要具備較低電源變得困難,共模電壓不匹配越嚴重,靜態電流消耗就越高,但這與資料速率無關。

支援物理層變異衍生三大優勢

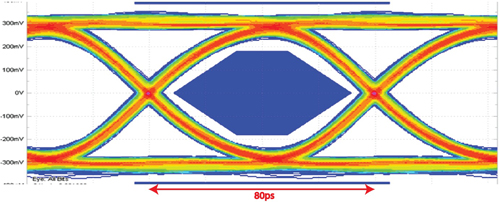

JESD204B規格對於眼圖性能除了電氣規格之外,還有三個物理層差異的要求。性能指標包括:定義資料眼圖到遮罩和總抖動預算。由LV-OIF-11G-SR允許的總抖動最大數字是一個單位間隔(UI)的30%。

如圖1顯示,在12.5Gbit/s下的JESD204B無修飾眼圖加眼圖遮罩,眼圖遮罩允許餘量可在垂直和水平軸確定性的量。值得注意的重點是,12.5Gbit/s的眼圖遮罩滿足LV-OIF-11G-SR的規格,這是根據11.1Gbit/s的速度規格,比其他可在12.5Gbit/s的應用有更嚴格的時序要求。

|

| 圖1 5Gbps下的JESD204B眼圖與LV-OIF-11G-SR傳輸遮罩的比較 |

JESD204B支援串列資料傳輸三個物理層的變異,由LV-OIF規格中定義和分類取決於最大JESD204B通道速率,定義三種物理層變種類別的速率是3.125Gbit/s、6.375Gbit/s和12.5Gbit/s,例如,LV-OIF-SxI5為基礎的操作:從312.5M~3.125Gbit/s;以LV-OIF-6G-SR為基礎的操作:從312.5M~6.375Gbit/s;

以LV-OIF-11G-SR為基礎的操作:從312.5M~12.5Gbit/s。

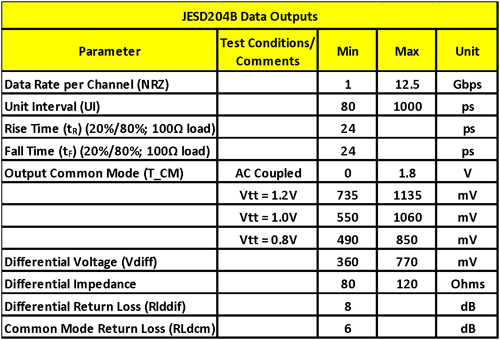

每個類別都有稍微不同的最小和最大的電氣規格,來容納資料速率所支援的寬廣範圍之不同需求。表1就顯示出電氣規格參數為LV-OIF-11G-SR的物理層的變異,用於JESD204B的最大資料速率12.5Gbit/s。

這些規格變異的優點之一是更廣泛的共模電壓範圍,比起直流耦合的情況下更能得到這個鏈接的支援。這放寬了JESD204B傳送器和接收器在被不同供應商使用時的系統設計要求,因為它提供所必需的位準位移。

對交流耦合資料線路的第二個優點是共模雜訊在傳送器和接收器之間被去耦,如此有助於改善系統設計人員所擔憂的訊號品質,因為直流耦合在共模雜訊耦合到資料線路時更容易受到影響。

交流耦合的第三個優點是它放寬從不同供應商所提供的不同傳送器(VTT)和接收器的終止電壓要求,進而讓接收器能夠在最佳的共模電壓下工作,這讓JESD204B傳送器和接收器得以在系統設計需要不同電源電壓的彈性需求下,在不同的終止電壓工作(表1)。

|

| 表1 LV-OIF-11G-SR JESD204B 12.5Gbps傳送器的電氣規格表示共模電壓終端在鏈結上的彈性 |

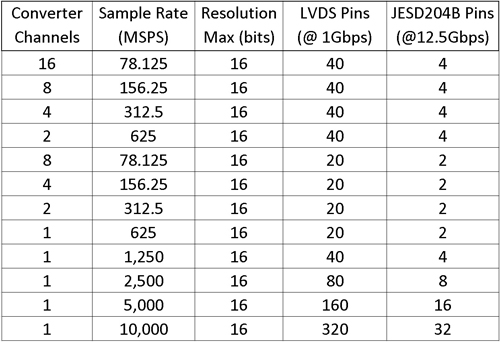

JESD204B介面還可以為許多轉換器將資料劃分到單一鏈接。由於鏈接速率提高到12.5Gbit/s,更多的轉換器可以容納到同一鏈接(所有其他變量是常數),這對具有二、四、八和十六個轉換器在單一封裝的裝置特別有用,並具有超越LVDS介面的明顯優勢。如同一種I/O結構,LVDS可支援Direct I/O在單一轉換器進行資料的輸入輸出,但並沒有明確定義出一種方法結合通過I/O的多重轉換器之間的資料(表2)。

|

| 表2 具有不同取樣率和通道數的轉換器比較表,表內顯示I/O數量的差異。相較於操作在1.0Gbps的LVDS接腳數,操作在12.5Gbps的JESD204B介面所耗用的腳位數只有前者的十分之一。 |

JESD204B有效克服高速資料傳輸挑戰

有了JESD204B,透過相同的接腳將來自多重轉換器的組合資料進行串列式發送與傳輸便有一個明確規格。每個轉換器資料的組成甚至不需要是一個實際的固定式硬體轉換器,而是來自一個「虛擬轉換器」過濾器,做為可以硬體轉換器而來的幾個經過數位處理的輸出之一。使用實部和虛部資料(I&Q)為90度相位取樣的通訊系統,還可以利用虛擬轉換器為鏈接JESD204B的多重轉換器發送資料。

對於高速轉換器頻寬無止盡的需求,市場正推動以更先進的互補式金屬氧化物半導體(CMOS)製程節點來設計低功耗和更高的性能,如此也為新的介面帶來挑戰。最高12.5Gbit/s速度的JESD204B介面,有助於解決這些挑戰,否則將需要越來越多的LVDS DDR通道,來跟上頻寬速度和高取樣率能力的腳步。

重點是,轉換器數位介面的接腳I/O,對於耦合和電源供應領域的需求將有助於為系統選擇合適的轉換器。

(本文作者皆任職於ADI)