為了解決行動資訊和視訊流量的爆炸性增長,無線基礎設備市場正迅速朝新型異質網路(HetNet)架構方向發展;而新的低功耗節點(LPN)如小型蜂巢、低功耗無線射頻遠端網路架構(RRH)和中繼設備的出現,彌補了傳統巨型蜂巢式(Macrocell)基地台的不足。

|

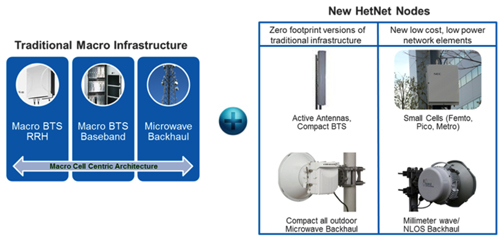

| 圖1 當今不斷演變的無線異質網路結合新型零空間占用的傳統巨型蜂巢式,以及各種新的低功耗、低成本的網路元件。

|

同時,行動營運商不斷追求更低的資本設備支出(CAPEX)及營運支出(OPEX)成本,推動傳統的巨型蜂巢式基地台往「零空間占用」架構方向發展(圖1),如緊湊型基地台、主動式天線和全室外微波/毫米波無線。

在異質網路的世界裡,營運商擁有高度彈性的網路部署方式,能夠充分利用有限的頻譜資源,而消費者則可以在各種環境中享有無處不在的寬頻覆蓋。但現在面臨的問題是,開發人員是否可以建構和部署可擴展的綠色異質網路,來解決日益增加的流量需求,包括可預期來自物聯網(IoT)的需求,並仍然滿足嚴格的成本和功耗目標,以維持營運商的投資報酬率。

低功耗節點建置如火如荼

從硬體的角度來看,大多數這種新的網路元件必須滿足一些共同的要求。擁有結構緊湊、重量輕、大批量特質的低功耗節點具有嚴格的功耗、電路板空間和成本的限制。此外,這些低功耗節點必須具有高度可配置特性,支援多種空中介面標準和射頻(RF)頻率,另外還必須擁有足夠的彈性以支援實際升級,這已經成為新的先進長程演進計畫(LTE-Advanced)異質網路功能,在第三代合作夥伴計畫(3GPP)版本11和更新版本中做出規範。其他主要的要求還包括易維護和可靠性,包括支援自組織網路(SON)功能,在電壓不足的情況下提供不間斷的服務,並提供多個網路定時和同步的選項,如IEEE1588v2和同步乙太網路(SyncE)。

近期,半導體廠商已經開始著手克服這些系統的挑戰,並提供一些創新的基頻和射頻產品來滿足異質網路市場的需求。一般情況下,硬體設計師使用現成的特定應用標準產品(ASSP)解決方案和/或客製化特定應用積體電路(ASIC)實現資料通道密集的功能,因為它們提供這些系統所需的最佳成本和功耗組合。同樣地,設計團隊選擇高度整合的多頻帶無線射頻積體電路(RFIC)和寬頻功率放大器(PA),以降低電路板上射頻元件的數量,並有助於最小化整個電路板面積和重量。

此外,工程師們採用一些整合的可編程設計電源管理元件整合可編程設計類比和邏輯電路,以簡化電路板管理的設計,支援通用的功能,包括電源管理、數位電路管理和介面邏輯。

接著描述典型的異質網路小型蜂巢的硬體架構,並解釋如何使用來自半導體廠商的最新產品,讓設計師們可以將資料路徑、控制路徑和電源管理功能分區設計,進而優化效能並滿足嚴格的異質網路要求。

異質網路包含多種小型蜂巢

異質網路中有從部署在住宅和企業單位的毫微微型蜂巢式基地台(Femtocell),到新型用於更高容量和覆蓋範圍(室內和室外)的微微型蜂巢式基地台(Picocell)和都會型基地台(Metrocell)。

|

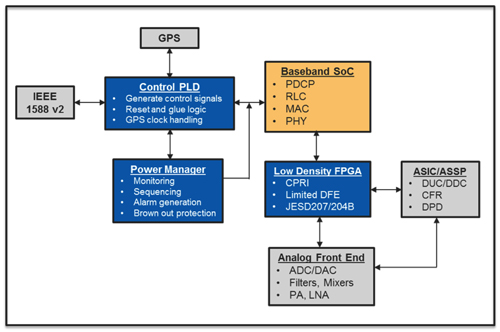

| 圖2 Picocell/Metrocell中典型的功能方塊圖 |

這些小型蜂巢在其覆蓋範圍和平均輸出發射功率上皆不同於巨型蜂巢式。例如,一個小型蜂巢的典型輸出發射功率範圍從只有幾百毫瓦(mW)到小於10瓦(W)。由於小型蜂巢往往須要在公共場所支援隨插即用的安裝,如燈柱上,其特性如大小、重量、功耗、散熱和SON功能成為關鍵的設計考量因素。這些小型蜂巢還必須支援不同的部署配置,包括緊湊型基地台在一個實體盒子裡整合基頻和無線發射單位,以及雲端無線存取網(RAN)型配置,其中多個獨立的無線發射裝置連接到同一個集中式基頻單位,執行LTE-Advanced功能,如多點協作或協調多點傳輸收送(CoMP)。圖2為Picocell或Metrocell中典型的上層功能方塊的概述。

如圖2所示,包含L1/L2/L3層的基頻處理通常是最適合實施基頻系統單晶片(SoC)的ASSP。該系統單晶片通常設有多個數位訊號處理(DSP)和精簡指令集運算(RISC)核心處理軟體方面的功能,以及硬體加速器,用以解決運算密集型工作,如第三代行動通訊(3G)和長程演進計畫(LTE)標準。

至於低功率Femtocell(約100~200毫瓦),從基頻系統單晶片來的資料通常是透過JESD207介面直接傳輸到射頻類比前端。

另一方面,室內Picocell(約1瓦),通常需要一些有限的數位前端(DFE)功能,如峰值因數衰減(CFR)。這些解決方案還需要額外透過通用公共射頻介面(CPRI)介面連接基頻系統單晶片,並且透過低壓差分訊號(LVDS)/JESD204B連接資料轉換器。低密度現場可編程閘陣列(FPGA)結合帶有串列/解串列器(SerDes)的高速邏輯和靈活的輸入/輸出(I/O)介面,以及在一個小尺寸封裝中的數位訊號處理功能,便是此應用最理想的選擇,如萊迪思(Lattice)的ECP3-70(ECP3系列)元件。

Metrocell(約5~10瓦)通常需要一個完整的數位前端解決方案,包括功率放大器線性化技術,如數位預失真(DPD),以及增強數位升頻(DUC)/數位降頻(DDC)/峰值因數衰減功能。

從成本和功耗的立場來看,可以將計算密集型的資料運算功能(數位升頻/數位降頻/峰值因數衰減/數位預失真)使用ASIC/ASSP實現,同時使用低密度FPGA,保留可編程設計的連接功能(CPRI、JESD204B、LVDS等)。

Femtocell和室內Picocell類比前端通常是一個高度整合的多模、多頻段、多天線的無線射頻收發器晶片組,其中包括資料轉換器、頻率合成器和通道選擇濾波器;而Metrocell類比前端提供一個更複雜的挑戰,設計者通常利用多個獨立且更高效能的元件,如基於JESD204B的資料轉換器和額外的類比電路,來實現改善功率放大器效率的技術,如封包追蹤(Envelope Tracking)。

時間和頻率同步是小型蜂巢的關鍵,鑑於潛在的接收問題與全球衛星定位系統(GPS)在室內的位置,備份同步解決方案,IEEE1588v2或SyncE通常使用現成的ASSP晶片組來實現。管理和分發時脈到電路板上的其他元件以及執行基本控制功能、I/O擴展和介面邏輯功能,設計者通常可以使用小型、低成本的可編程邏輯元件(PLD)。

此外,Metrocell須要支援多種供電方式,進而在頻繁的電壓不足條件下能夠不遺失資料。為了實現多種板級功能,包括電源排序、監控、電壓測量和用於電壓不足保護的供電過渡控制,設計人員需要一個整合的電源管理元件。可編程設計、高精度的混合訊號解決方案,可提供完整的電源管理功能,並且代替多個IC,還可以提高可靠性,加快產品上市時間。

行動寬頻連線無處不在

異質網路顯然將是無線基礎設施的發展方向。這些創新的架構能為營運商降低資本設備支出及營運支出成本,同時為消費者和物聯網提供無處不在的行動寬頻連線。

然而,要實現此一目標,設計師不得不尋找一種方法,有效地在系統架構層面上衡量取捨新的低成本、低功耗網路單元的開發,如小型蜂巢、主動式天線和毫米波無線。利用最新現成的ASSP、客製化ASIC、低密度FPGA和整合型電源管理元件,設計師可以建構一個提供全新效能水準、整合度和設計彈性的平台,並且不會超出其嚴格的成本和功耗預算。

(本文作者為萊迪思資深策略行銷經理)