無線通訊接收器的前端可能會因同步或非同步訊號傳輸而形成過載;在分時雙工(TDD)系統內,交換器(Switch)或循環電路連接埠間的不完美隔離,以及由兩個無相關系統天線間所造成的非故意耦合,都會造成此一結果。

在核磁共振(NMR)接收器內,另一個造成過載的原因為刺激脈衝後探針線圈儲存能量所帶來的振鈴(Ringing)訊號;縮小低雜訊放大器(LNA)元件尺寸的做法雖可改善射頻效能,卻會犧牲過載的承受能力。例如採用0.25微米(μm)pHEMT技術的400微米與800微米低雜訊放大器,最高輸入功率PiMAX分別為7dBm與10dBm,過載會影響到硬體與承載的資訊,太大的過度驅動會因跨接導線/金屬化保險絲或電晶體接面熔化而造成元件故障,而由於過度驅動所造成的閘極電流快速增加,也會因金屬變化而縮短元件的壽命。

此外,長時間暴露在微小過載的情況,也會造成元件輸出功率或第三階輸出截點的劣化,核磁共振接收器則會因前端接收器逐漸由飽和恢復的停滯時間(Dead-time),而漏失關鍵資訊。

利用限幅器避免過載

|

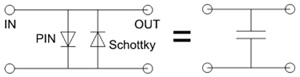

| 圖1 蕭特基強化PIN限幅器的電路安排及其小訊號等效電路 |

限幅器(Limiter)透過允許低於特定位準的射頻訊號通過,並大幅衰減超過臨界點的較大訊號來避免過載。最簡單的限幅器電路包含一個PIN二極體(Diode)及作為直流返回路徑的並聯電感,也就是所謂的自偏壓限幅器,但這樣的做法會使其臨界點比許多低雜訊放大器的過載限制來得高。在基本PIN限幅二極體上並聯蕭特基二極體(Schottky Barrier Diode),亦即蕭特基強化PIN限幅器(圖1)可以將限制臨界值降低約10dB,主要原因為蕭特基二極體較低的導通電壓。

由於限幅器必須安排在接收器增益電路的前端才有效,因此其小訊號插入耗損會對整體雜訊指數造成相等dB單位的增加。插入耗損主要由傳輸線上二極體寄生電容造成的負載產生。在過去,微波限幅器使用裸二極體晶片製造,但現代大量生產的限幅器二極體則使用會大幅增加電容的塑膠材料封裝。此外,蕭特基強化PIN限幅器中的額外二極體,也會帶來比僅PIN二極體限幅器更大的耗損。

去除限幅器二極體電容問題的急迫性,可以由許多被提出的解決方案中看出,二極體堆疊可以降低電容但卻帶來較高的導通臨界值,使用平頂結構來移除部分PIN接面區,雖然可以降低寄生電容,但卻大幅增加二極體的轉換熱阻。

另一方面,蕭特基二極體可透過高阻抗四分之一波長傳輸線或指向性耦合器由射頻路徑隔離,不過,這些被動式組件會增加成本與體積。電容性負載可透過連接二極體到較低阻抗(12.5Ω)的節點降低,但卻需要降壓與升壓變壓器。

為降低這類限幅器的高頻耗損而不須要付出前述解決方案的代價,本文提出將二極體寄生電容結合低通梯型濾波器的創新組態。雖然使用二極體的寄生特性來降低耗損,已在自偏壓PIN限幅器中提到,但從未出現在蕭特基強化PIN限幅器上。

|

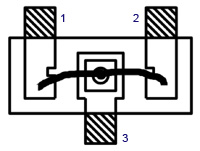

| 圖2 PIN二極體內部圖,其中晶片上的陽極接點透過跨接導線連接到兩個接腳。 |

為快速製造新的組態,使用原有二極體產品線的低成本SOT-323封裝元件,PIN二極體擁有1.5微米的I層厚度,約1皮法(pF)的零偏壓電容及適合新組態的雙陽極封裝形式(圖2)。此蕭特基二極體擁有1毫安培(mA)時250毫伏特(mV)的載子高度,以及約0.8皮法的零偏壓電容,二極體跨接導線與接腳的寄生電感分別為0.7奈亨(nH)與0.4奈亨,限幅器使用包含50歐姆(Ω)共平面波導接地(CPWG)傳輸線,中間具有間隙的30密爾(mil)厚FR4印刷電路板(PCB)實現。

PIN二極體採陽極接腳跨越間隙的方式安裝,蕭特基二極體則如常見的限幅器連接到傳輸線的輸出端,雙陽極PIN二極體、蕭特基二極體及帶間隙線的組合帶來近似低通梯型濾波器的小訊號等效電路。

為進行效能的比較,在相同電路板上安排一個組合至連續傳輸線的傳統PIN蕭特基限幅器,兩個限幅器採用完全相同的二極體元件,由於兩個二極體在傳統限幅器組態內採並聯形式,因此小訊號等效電路可由一個1.8皮法的電容代表。

改善插入耗損及頻寬

|

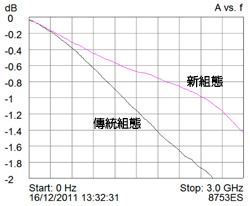

| 圖3 傳統與新限幅器組態的小訊號插入耗損相對頻率關係圖 |

新的組態可以改善插入耗損與頻寬,由於寄生電容在頻率低於300MHz時幾乎不會造成影響,因此兩個組態在此擁有相近的插入耗損,但當頻率超過300MHz時,耗損差異就會大幅擴大(圖3)。

在常見的2.1GHz 3G頻帶中,可以達到令人滿意的0.8dB耗損差異,這樣的改善也可以量化為頻寬的提升,以1dB耗損點比較,新組態可以將最高頻率限制由原本的1.3GHz提高到2.4GHz。

實際的結果會比這個測量值表現更佳,原因是測試安排可能會擴大耗損,在實際應用上,電路板的走線要短上許多,同時限幅器的輸出也會直接連接到低雜訊放大器而不經過射頻連接器,透過正規化去除測試安排的耗損後,限幅器的1dB頻寬可以大幅提高到3GHz。

除降低插入耗損外,新的組態也帶來改善回返耗損(RL)的結果,特別是在1.2G?3GHz頻帶範圍變化超過4dB時,新組態梯型濾波器等效電路明顯地比原始分流電容擁有更好的匹配,在回返耗損RL≦-10dB點,新組態可將最高頻率限制大幅提高三倍,由傳統組態的1.1GHz提升到2.9GHz。

新電路組態值得期待

相較於原有組態,蕭特基PIN限幅器的新電路組態可以同時改善插入耗損、匹配、頻寬及洩漏功率,由於採用二極體封裝寄生電容來形成低通梯型濾波器,因此組態的改變沒有增加額外的元件,也沒有擴大電路板的占用面積,相同的做法已經成功應用在降低僅PIN二極體限幅器的耗損上。

實驗結果顯示,新組態也可以在蕭特基強化PIN限幅器上得到相同的好處,能夠改善使用這類限幅器無線通訊與核磁共振/MRI接收器的靈敏度,同時這個組態也可適用於更高頻率的運作應用中。

(本文作者任職於安華高)