大容量FPGA具備高處理速度與效能,因此適用於大型通訊系統相關的應用中,如ASKAP此一龐大架構的天文望遠鏡陣列即為一例。隨著FPGA技術不斷推陳出新,實現更大型的ASKAP系統將指日可待。

由二十個國家聯合開發的「無線電望遠鏡平方公里陣列(SKA)」是目前全世界最大、最靈敏的天文望遠鏡。預計在未來10年內,70M~10GHz的大面積成像技術將會顛覆人類過去對宇宙的認識。在SKA開發過程中,澳大利亞探路者無線電望遠鏡(ASKAP)占用700M~1.8GHz的關鍵SKA頻段,ASKAP試圖透過相位陣列系統並將其建置到拋物面的反射鏡,以取得即時的大面積成像。這樣的寬廣成像使ASKAP成為史無前例的天文望遠鏡,可望在SKA研究領域中取得重大進展。

澳大利亞聯邦科學與工業研究組織(CSIRO)是澳大利亞政府資助的研究機構,其下天文學和空間科學研究所(CASS)負責開發ASKAP。擁有優越的地理位置、創新的技術和科學研究,使ASKAP成為全球領先的無線電天文學設備,同時並與SKA的科學研究與技術發展方向一致。另外CSIRO也參與SKA的開發工作,此系統預計2024年能開始運作。

ASKAP架構龐大

ASKAP目前仍處於在西澳內地Murchison無線電天文台(Radio Astronomy Observatory, MRO)的建設階段,由一套包含三十六個12公尺長的碟形天線陣列組成,每個碟形天線皆配備先進的相位陣列系統(PAF)提供30m2/。的大視野。不同於傳統光學天線,PAF採用數位電子元件製造波束形成(Beamforming)器,進而提供多個可配置的波束方向圖。地處南半球的位置對天文學研究極其有利,加上超大無線電平靜區(無線電頻率發射受控區域),ASKAP將發展成無與倫比的無線電望遠鏡。

ASKAP的大視野和寬頻雖然有助於天文學家進行研究,但面對ASKAP比現有望遠鏡高出兩個等級的訊號處理,未來的發展仍是一大挑戰。所幸,先進的現場可編程閘陣列(FPGA)能提供整合這些功能的完美組合,以滿足大約每秒兩千兆次運算以及100Tbit/s通訊的效能需求。與其他代方案相比,如高效能計算(HPC),FPGA能提供功耗和資本支出相對較低的解決方案。

超強計算能力/高頻寬通訊為挑戰

ASKAP須解決兩大難題:超大計算能力與超高頻寬資料通訊。解決其中一個難題並不難,但要同時解決這兩個難題卻相當棘手。廠商推出的Virtex-6系列FPGA能夠提供輸入/輸出(I/O)頻寬與計算能力的完美平衡,適合濾波器組和波束形成器所需要的重複並行運算。

此外,ASKAP的設計還受到諸多因素的影響。偏遠地區的電費和相關氣候條件也為儀器冷卻帶來更多挑戰。無線電天文學儀器的運行環境還要求極低的電磁干擾(EMI),因為即便是極低的輻射,望遠鏡也很敏感,FPGA在降低工作電壓與I/O擺幅方面的技術有助於進一步減少EMI。另一個優勢是,隨著功耗的降低,系統會減少冷卻需求,這對24小時全天候運行的天文學儀器來說是雙重節約。

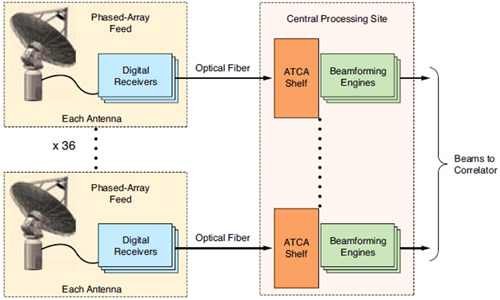

藉由分治法分析,ASKAP團隊決定採用低成本的立即解決方案。如圖1所示,其中有兩個數位訊號處理位置--天線的電子元件和中心處理站,天線的電子元件負責採樣和處理一百八十八個PAF接收器的輸出和四個校正訊號,然後透過光纖將資料傳輸到中心處理站。

|

| 圖1 長達8公里的光纖,以天線為基礎的處理,從波束形成器和相關器的公共中心處理站分離。 |

在中心處理站,各個天線的波束形成器組成射向天空的三十六個雙極化波束。所有天線波束形成器的輸出連接到相關器,形成複值可視訊號,可用於構建天空圖像。每個天線含有一系列的接收卡,負責處理少量PAF接收器輸出,若是波束形成器,則這些接收卡負責處理整個輸入頻寬中的小頻率片段,這種技術可解決資料通訊難題,同時也可以降低每個處理卡成本。

數位接收器負責採樣PAF中頻訊號

|

| 圖2 數位接收卡負責PAF接收機資料的採樣與濾波,然後把資料傳輸到中心處理站。 |

數位接收器子系統包含用於對來自PAF的中頻(IF)訊號採樣的硬體,以及把IF頻寬分割為1MHz的頻段,並把最終資料傳輸到中心處理站波束形成器。子系統分為四個3U×160毫米歐規卡子架,每個子架由十二個數位接收卡、一個電源卡和一個控制介面卡組成,數位接收系統如圖2所示。

電源卡負責把48VDC輸入轉換成數位接收卡所需電壓。控制卡包含一個用於執行UDP本地控制和監視的1GB乙太網埠們在低成本Virtex-5 FPGA中實現相對較簡單的要求/回應控制韌體,而控制和監視鏈路則透過背板從控制卡扇出(Fan Out)到數位接收卡。

每個數位接收卡負責對來自PAF的四個類比IF接收器訊號進行採樣。此卡由三大部分組成:類比數位轉換器(ADC)、FPGA和10Gbit/s光資料傳輸元件。採樣由e2v半導體提供的兩個雙輸入8位元ADC執行,採樣速率為768MSPS,所提供的總頻寬為384MHz。FPGA以四個同步訊號源384MHz 雙倍資料(DDR)資料流接收來自ADC的資料,系統採用ADC測試圖校正這些資料線中的IDELAY。

ADC資料傳送到客製化的Radix-3三百八十四通道多相濾波器組,形成1MHz寬的頻道。多相濾波器組以32/27比率對這些通道執行密集採樣,因此其時脈頻率為303.4MHz。透過對濾波器組的密集採樣,可確保在操作位於波束形成器下游的精細濾波器之前,能夠在通道邊緣遺失最少資訊。

為上述數位接收器選擇Virtex-6元件是因為其具有足夠的乘法器和記憶體,適合多相濾波器組的特定尺寸,為其監控功能,如長條圖與光譜積分器提供足夠預留容量。對於許多無線電天文學應用,隨機存取記憶體(RAM)與數位訊號處理器(DSP)的比一般都為1:1,但必須適合I/O頻寬。另外,最低速度等級元件能以最低成本達384MHz。

資訊以數位接收卡即時分配

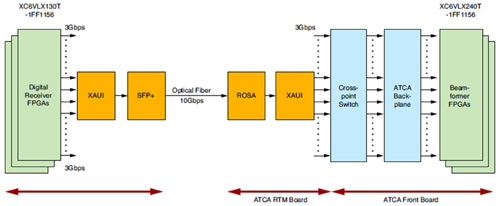

ASKAP專案團隊面臨的巨大挑戰之一,是把來自天線陣列PAF大量的即時資料傳輸分配到中心站的數位訊號處理鏈。圖3為用於三十六個PAF之一的資料傳輸與分配架構概況。

|

| 圖3 每個天線對波束形成器傳輸3Tbit/s資料,後者採用ATCA背板分配資料。 |

數位接收器中的FPGA透過十六個GTX收發器輸出資料,其中每個GTX收發器的線路速率均為3.1875Gbit/s。每個數位卡都產生一個用於串列器的159.375MHz參考時脈,因此公共參考時脈並不存在,避免造成資料錯誤。每條鏈路為數位接收卡處理的四個PAF埠承載十六分之一的總處理頻寬,即19MHz。

由於每個波束形成器卡片也處理十六分之一的頻寬,因此來自數位轉換器FPGA的每條輸出鏈路目的地是不同的波束形成器卡片。來自數位接收器FPGA的串行輸出資料先進行分組,再聚集到客製化的XAUI(10G附屬單元介面)封包結構。由於十六條鏈路是單向點對點互連,因此無需完整的封包交換型通訊協定。

來自FPGA的十六條輸出鏈路被平均分為四組,每組包含四條通道,每組都配有XAUI幀編碼。其將輸入串流傳輸到數位接收卡中的Netlogic XAUI收發器上,在此把四個輸入流重新序列化成為10.51875Gbit/s 64b/66b編碼輸出串列流(光纖通道線路速率)。由四個10G收發器驅動四個Finisar SFP+光收發器。

每個天線由一百九十二條(四十八個數位轉換器/天線×四條光纖/數位轉換器)連接到中心站的單模光纖,總數據速率達到2Tbit/s,光纖從最近的數百公尺,到最遠長達8公里不等。

波束形成器採用分組化鏈路

資料路徑和分散式架構的兩個關鍵元件是Vitesse 6.5Gbit/s 72×72交叉點開關和業界標準先進電訊計算架構(ATCA)背板。這些元件能把3.1875Gbit/s串列資料流從數位接收器直接傳輸到相應波束形成器卡進一步處理。

採用分立的光接收器次模組(ROSA)元件把來自天線的10Gbit/s光資料訊號重新轉換成電訊號,然後透過與數位接收器相同的XAUL收發器元件把訊號解串成四個3.1875Gbit/s訊號。此電路位於ATCA後端轉換模組,每個RTM可接受12×10Gbit/s資料串流。

|

| 圖4 16插槽ATCA機架核心是Virtex-6 LX240T,可容納波束形成硬體。 |

ATCA背板最多可支援十六張卡(圖4),每張卡有四條雙工3Gbit/s資料連結連接到各卡,也就是說每個卡有(16-1)×4=60條雙工鏈路。使用ATCA背板時的挑戰之一,是每個插槽的全網狀連接各不相同,因此在啟動時,必須根據卡所位於的具體插槽,分配到各訊號路徑,因此採用72×72交叉點開關設定到各張卡的連接路徑矩陣。

一旦3.1875Gbit/s資料串流到達其目標波束形成器卡,就被傳輸到四個LX240T處理FPGA中的一個GTX接收器上。3.1875Gbit/s資料串流在此解串,而資料封包進行解碼。由於每個波束形成器FPGA只處理304MHz總頻寬中的大約5MHz,因此到達3.1875Gbit/s資料串流的19MHz頻寬四分之三,須要轉發到位於同一卡上的另外三個波束形成器FPGA。波束形成器子系統的最後轉發也採用分組化鏈路,而此時物理傳輸透過各個DSP FPGA之間的低壓差分訊號(LVDS)I/O仍然相互連接。

此外,由於在各個DSP卡將產生GTX解串器的參考時脈,因此,相關資料傳輸設計採用Virtex-6 GTX收發器內部的時脈校正與彈性緩衝器功能。

波束形成器提供校正RAF支援功能

資料通訊系統使公共通路內所有的PAF接收器都能到達特定的波束形成器FPGA。輸入數位接收器的時序訊號用於同步波束形成器中的一百九十二個資料串流,波束形成系統的主要功能是形成多個波束,另外也提供一系列校正及監控的PAF支援功能。

操作波束形成能獲取串列PAF資料流,然後在雙埠RAM中緩存這些資料。從通訊鏈路輸入資料時,可在之前保存的時間片段(Time Slice)中形成波束。一組波束形成器權值包含一個須納入波束形成計算的接收器列表和一個關聯複數權值,接著DSP48元件執行對各個時間片段的乘法與加總計算。

來自各個波束形成器(最多同時可以有三十六個波束)的資料儲存到外部DDR3記憶體。每個FPGA都直接連接到一個DDR3和一個以64bits×800Mbit/s速度運行的介面。

在相關器處理波束資料之前,採用另外一個多相濾波器組設定波束的最終頻率解析度。進入此第二個濾波器組、速度較慢的資料和數量較多的波束需要更大的儲存空間。FPGA內部區塊RAM(Block RAM)運行方式與DDR3記憶體大相徑庭。BRAM擁有高頻寬,但是深度有限,而DDR3頻寬較低,但深度幾乎無限。將波束資料寫入DDR3記憶體,再按照適合濾波器組和相關器的順序讀出。

波束形成器FPGA的支援功能之一是計算陣列協方差矩陣(ACM)。ACM用於校正陣列,相關計算過程採用各個PAF接收器,並把它與各個其他接收器交叉關聯。結果每隔幾秒鐘將累積一次,以便減少輸出資料頻率。波束形成器和ACM均以 318.75MHz(159.375MHz基本通訊時脈兩倍)的頻率處理資料。在完成ACM計算後,則採用UDP封包並透過10億位元乙太網絡從各個波束形成器輸出結果。

波束形成器卡(圖5)是標準ATCA卡(8U×280毫米),包含四個訊號處理FPGA、一個控制FPGA、一個交叉點開關、四條DDR3 PC3-8500記憶體和八個SFP+埠(四個全雙工、四個僅限傳送)。

|

| 圖5 固定波束形成硬體的是ATCA網、交叉點開關、Virtex-6 FPGA、DDR3記憶體與SFP+光學元件。 |

開發軟體輔助設計流程

ASKAP專案團隊用於所有模塊,即測試訊號產生器、多相濾波器與波束形成器的設計流程是以支援MATLAB/Simulink的賽靈思系統產生器為基準。利用VHDL語言編寫資料通訊、控制和監控及介面,採用系統產生器模擬相關訊號處理模塊,並採用ModelSim模擬以HDL為基礎的模塊。

完成模擬之後,在硬體中獨立驗證各個模塊,然後把它們與其他已完成的模塊整合,以確認資料與處理路徑的運行是否符合預期。在此階段大量使用 ChipScope整合邏輯分析工具,便於追蹤錯誤,並能輕鬆掌握晶片上的資料運作。

透過VHDL程式產生器所產生的DSP網表(NGC格式),設計團隊整合整個設計及所有其他基於HDL的模塊,並採用XST和ISE Project Navigator進行整合與建置。

數位接收器和波束形成器設計採用大量BRAM與DSP48E(表1),因此很難透過簡單約束達到時序要求。一般須採用布局規畫,布局規畫的主要目的是透過減少路徑延遲進而縮短時序。PlanAhead工具可讓ASKAP專案團隊在網路中使用流水線技術,同時引導映射與布局/布線工具以符合時序要求。這意味著在一般情況下,最好方法是除部分區域約束外,還須另外裝置BRAM群組。此外,這種設計分析方法還能明顯縮短執行時間。表1概述各個FPGA元件的時脈速度以及FPGA資源利用統計,另外還列出數位接收器和波束形成系統的總數清單以供參考。

新一代FPGA處理效能更高

FPGA已證明能成功應用於ASKAP數位後端--包括資料通訊的處理效能和I/O的頻寬。Virtex-7元件系列可達更高的資料處理速率、處理密度和更低的功耗。另外,更大的Virtex-7/Kintex-7具有加強型I/O元件,將大幅改進系統架構並降低電路板設計的製造成本。

隨著軟體無線電在商用領域的快速發展與普及,速度更快、成本更低、功耗更小的ADC,以及更新FPGA的推出,都讓採用這種新技術的SKA原型建置方案有更多發展的可能性,並為PAF資料的直接採樣與處理帶來數位解決方案。這一切也預告著終極無線電望遠鏡SKA所需的大規模數位系統即將問世。

(本文作者皆任職於澳大利亞聯邦科學與工業研究組織)