WiMAX或稱為IEEE 802.16標準,是針對寬頻無線存取所設計,目前已逐漸獲得重視,被視為具有巨大市場潛力的新科技。本文將先針對現有與發展中的IEEE 802.16標準進行簡介,並探討其主要差異與應用,亦將剖析典型WiMAX基地台的實體層與媒體存取控制層。

各種全球微波存取互通介面(WiMAX)基礎架構開發者在實行上所面對的各項挑戰,包括效能/成本/在挑選矽晶片上進行抉擇的彈性,若能透過現場可編程閘陣列(FPGA)架構的系統來解決上述挑戰,以加速產品面世時間需求,將是在此市場中更早達到成功所須考量的關鍵要素。

WiMAX問世刺激寬頻無線存取成長

網際網路在10年間的爆炸性成長,帶動了高速、無處不在的網際網路存取需求的增長。寬頻無線存取已經逐漸普及,成為另外一個最後一哩(Last Mile)科技,用以替代數位用戶迴路(DSL)線路與纜線數據機。隨著IEEE 802.11無線區域網路(WLAN)標準在全球部署的大量成功,IEEE 802.16d無線都會網路(WMAN)標準的發展也正在進行中。此一技術可支援居民和中小企業的固定寬頻無線存取,對於沒有任何固網基礎設施的地區,可直接存取網際網路。針對IEEE 802.16e版本的標準也正在制定中,同時為WMAN環境中的終端用戶提供移動存取。

WiMAX論壇是由業界引導、非營利的法人組織,以促進IEEE 802.16相容設備的應用,確保寬頻無線產品之間的相容性和互用性。該組織是非營利的協會,在2003年由設備和元件供應商所共同組成,以推廣營運商採用符合IEEE 802.16規範(表1)的寬頻無線存取系統設備。

| ◎表1 802.16標準之中的差異比較概觀 |

| |

802.16 |

802.16a/Rev. D |

802.16e |

| 完成日期 |

2001年12月 |

802.16a:2003年1月

802.16Rev. D:2004年6月 |

2005年中期 |

| 頻譜 |

10G~66GHz |

2G~11GHz |

2G~6GHz |

| 應用 |

回程傳輸鏈路 |

無線DSL和回程傳輸鏈路 |

移動網際網路 |

| 通道條件 |

僅在視距範圍內 |

非視距 |

非視距 |

| 位元率 |

多通道,28MHz頻寬時為32M~134Mbit/s |

多通道,20MHz頻寬時為75Mbit/s |

多通道,5MHz頻寬時為15Mbit/s |

| 調變 |

QPSK/16QAM/64QAM |

OFDM 256副載波/QPSK/16QAM和64QAM |

可擴展OFDMA |

| 移動能力 |

固定 |

固定 |

步行移動--區域漫遊 |

| 通道頻寬 |

20M/25M/28MHz |

1.5和20MHz之間,通道頻寬可選 |

與802.16a相同,含有UL次通道,以節省功率消耗。 |

| 典型蜂巢半徑 |

1~3哩 |

4~6哩,最大範圍30哩,取決於塔的高度、天線增益以及發射功率。 |

1~3哩 |

此修訂後的版本結合了IEEE 802.16、802.16a和802.16c,保留了所有模式以及主要特性,並沒有增加新的模式。該標準規定固定點對多點(PMP)寬頻無線存取(BWA)系統的空中介面,在WMAN環境中提供多種服務,該標準還為媒體存取控制(MAC)層規定了可選的改進網狀網路拓撲。一般來說,WMAN MAC能夠支援多種實體(PHY)層設備針對應用的頻寬進行最佳化。該標準包括系統工作在11GHz以下,以及10G~66GHz之間的PHY規範。10G~66GHz空中介面採用單載波調變,稱為WMAN-SC空中介面。標準還規定了頻率低於11GHz的WMAN-SCa、WMAN-OFDM與WMAN-OFDMA空中介面。

MAC層關注空中鏈結資源

在MAC層部分,此層的主要關注焦點是專注在用有效率的方式來管理空中鏈結的資源。MAC層包含了三個次層:特定服務聚合次層(SSCS)透過提供CS服務存取點(SAP)連結到上層實體的介面。MAC通用元件次層(CPS)提供核心的MAC功能,包括上行鏈路排程、頻寬要求與准許、連線控制與自動重複要求(ARQ)。隱私次層(PS)則提供驗證與資料加密功能。

802.16 MAC通訊協定所執行的工作,可以依不同的方式被分割成兩個領域,分別是週期性每個訊框的快速路徑活動與不定期的慢速路徑活動。快速路徑活動,像是排程、打包、分裂與ARQ,必須在單一訊框的細度分割下執行,且它們受到硬式即時截止期限的支配,必須及時完成與它們相關聯訊框的傳輸。相對來說,慢速路徑活動的執行一般是依據計時器,而不是關聯到特定的訊框或訊框期間,且多無迫切的截止期限。

PHY層側重MIMO天線配置

至於PHY層,因為正交分頻多工(OFDM)訊號在多通道衰弱無線通道中具有優異的性能,802.16標準的OFDM和WMAN OFDMA PHY層,建議在低於11GHz非視距(NLOS)應用中採用這種方案。其他無線標準也建議採用OFDM技術,例如數位視訊廣播(DVB)和無線區域網路。

除了隨機處理、前向糾錯(FEC)、頻譜交錯、映射至QPSK和QAM符號等這些常用功能之外,該標準還規定了多路天線技術,包括空時編碼(STC)、使用自適應天線的波束合成方案,以及多重輸入多重輸出(MIMO)配置,以獲得更高的資料速率。一般透過對資料訊號進行快速傅利葉轉換(FFT)和逆向快速傅利葉轉換(IFFT)來實現OFDM調變/解調。儘管在標準中沒有對其他高階訊號處理技術做出規定,例如峰值因數衰減(CFR)和數位預失真(DPD)等,也可以將這些技術應用在前向通道中,以提高基地台功率放大器的效率。上行鏈路接收處理功能包括時間、頻率、功率同步(測距)和頻域等化以及殘餘解碼/解調等,來恢復發送訊號。

硬體平台有助WiMAX實現

WiMAX系統設計人員必須達到許多嚴格要求,如處理速率、靈活性及產品面世時程等,才能獲得用戶支持。而要克服這些苛刻的要求,就須要倚賴硬體平台,其中一些常見的挑戰將在下文進一步描述。

在實行上的挑戰,從處理速率來看,WiMAX等寬頻無線系統對傳輸量和資料速率的要求,遠遠高於WCDMA和CDMA2000等蜂巢系統。為了能夠支援如此高的資料速率,基礎硬體平台必須有足夠的處理能力。而且,高階訊號處理技術的計算量大,例如Turbo編碼/解碼以及FFT/IFFT、波束合成、MIMO、CFR和DPD等前端功能,每秒鐘的乘法和累加運算達到數十億次。

在靈活性方面,WiMAX是相對較新的市場領域,目前還處於最初的發展和實施階段。802.16Rev. D標準甫通過,而802.16e移動版本還在制定中。在目前這種情況下,最終WiMAX相容產品中具有硬體靈活性及重新編程能力便顯得非常重要。這一特性可以確保實現現場編程,避免了由於標準不斷變化所帶來的風險。

關於產品及時面世,由於WiMAX是一種新興的技術,原始設備製造商(OEM)在儘早贏得市場占有率上最看重的就是產品的問世時程能力。產品及時上市對開發週期和硬體平台的選用有直接影響,設計人員須要使用方便的開發工具、軟體、電路板、現成的矽智財(IP)以及參考設計來加速實現系統設計。

在降低成本的途徑上,選擇硬體平台時要注意的另一重要標準,在於是否具有往後降低成本的途徑。隨著時間的推進,WiMAX標準/市場最終會在不確定因素沉澱之後穩定下來,這將導致產品最終成本比保持靈活性更重要。硬體平台應提供明確的降低成本途徑,並能夠在需要時無縫地來快速衡量靈活性和成本。

FPGA為適切解決方案

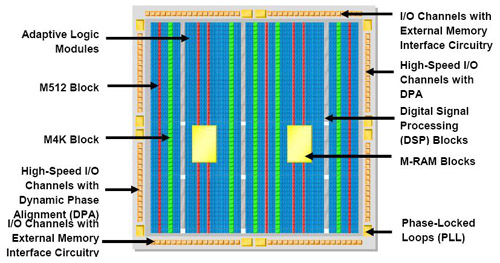

現場可編程閘陣列(FPGA)為WiMAX等寬頻無線系統開發提供了理想的實施平台。像是採用先進的高階、高性能FPGA做為寬頻系統的核心元件,將可加速性能,支援實現新功能。目前已上市的FPGA架構配置如圖1。

|

| 圖1 FPGA元件平面配置圖 |

前述元件在功能特性上的增進上,在邏輯架構端採用自適應邏輯模組(ALM),可以用較少的面積包裝更多的邏輯,並擁有更快速的效能,專業的數學運算功能可有效率地執行加法樹與其他運算密集的功能。至於在記憶體端,在三個模組尺寸中有9Mbits的記憶體,M-RAM、M4K與M512模組,包含同位位元進行錯誤檢查。效能達370MHz,混合寬度資料與混合時鐘模式。

至於在數位訊號處理器(DSP)模組上,具有專屬的乘法器、管線與累加電路,以及取整數功能,可在每個DSP模組的Q1.15格式中支援飽和功能。效能最高可達370MHz,可提供高達284GMAC的DSP傳輸率。而專屬的看門狗電路能確保在更新後功能仍可正確執行。

FPGA架構挑戰仍多

如同前文所述,高效能的平台由於包含嵌入式DSP模組、記憶體架構、邏輯架構及高速介面(圖2),能夠為WiMAX等寬頻無線系統在實行時提供強大與整合的平台。每一DSP模組可以支援各種乘法器位元寬度,如9×9、18×18、36×36以及工作模式如乘法、複數乘法、乘法累加和乘加,每個DSP模組的DSP傳輸量可達到每秒28億次乘法累加運算(GMACS)。如在WiMAX系統中實現複雜的DSP演算法就需要如此高的傳輸量,這些系統包括自適應波束合成、MIMO、FFT/IFFT、有限脈衝回應(FIR)濾波以及CFR等。容量最大的元件產品之一具有九十六個DSP模組,傳輸量達284GMACS,可支援三百八十四個18×18乘法器。

|

| 圖2 已問世之DSP模組架構 |

前文提及的元件傳輸量,比目前市場上的單晶片DSP處理器要高出數個數量層級。此外,DSP模組中還加入了新的取整數和飽和功能,能夠方便地將DSP韌體程式碼導入到FPGA中。

由於標準不斷變化,最終WiMAX相容產品的硬體靈活性和重新編程能力便非常重要。能夠根據市場需求的變化,輕鬆更新WiMAX系統的元件,將可以在任何網路上實現遠端系統更新、保持產品競爭優勢、並具有專用恢復電路,確保更新的可靠性。

如圖3所示,遠端系統升級是利用了FPGA元件和快閃記憶體,使用者可以採用幾個簡單步驟進行遠端系統更新,分別是透過網路,從開發位置向該元件發出更新命令、在記憶體中儲存更新資訊,以及以新資料更新元件。

|

| 圖3 三個步驟實現遠端系統更新 |

用FPGA開發的WiMAX系統可以在當需要其他通訊協定支援來保證今後產品的相容性時進行更新,必要時亦可進行功能增強與故障修復。

對於那些在設備實施階段還不確定的標準和應用,使用FPGA的WiMAX系統將能支援這些標準和應用的發展變化,從而避免了產品過時的風險。

對於任何有前途的新技術,OEM在開發WiMAX相容產品時,必須考慮產品及時面市的問題,以突出產品優勢。為達到這一目標,設計人員應將可採用現成的IP以及參考設計,以加速自己的開發過程。此外,使用方便的開發工具、軟體以及開發板也是其他要考慮的重要因素。

在WiMAX PHY層IP與參考設計中,有許多進階的問題須要討論。舉例來說,前向錯誤修正(FEC)就是一例。

由於802.16Rev. D修改了Reed-Solomon(RS)在上行鏈結與下行鏈結的外部程式碼連續性,以及與速率相容的迴旋內部程式碼。因此所謂的編碼是透過將模組格式中首先通過的資料用RS編碼器來執行,然後將它傳送到歸零的迴旋編碼器。

想要執行這些方案,可以透過RS編譯器與Viterbi編譯器的IP進行參數化。舉例來說,參數包括像是每個符號的位元數量、每個代號的符號數量、每個代號的檢查符號數量、欄位的多項式、產生器多項式的第一個根與產生器多項式的根之間的空白,都可以使用RS編譯器來進行指定。這讓設計師的工作變得非常容易,他們要做的只是在802.16Rev. D中提供指定的參數。此外,依據傳輸率的需求,使用者可以指定不同的實行技術,包括分離式、持續式,且串流解碼架構也可以實質地提供更多靈活性,以便在傳輸率與資源消耗之間進行衡量。自動產生的程式碼將會針對FPGA進行高度最佳化。

Turbo迴旋程式碼與Turbo模組程式碼是標準中指定做為選擇性的FEC方案,低密度的同位檢查(LDPC)程式碼是FEC程式碼的新型態,它已經越來越普遍,且可能會在802.16e版本中指定為選擇性的FEC方案。

如圖3所示,OFDM或OFDMA副載波是由在發送器執行IFFT運算所產生,當在接收器的FFT運算已經完成時,便可轉換訊號回到頻域之中。在802.16Rev. D標準中有特別指定,針對OFDM模式下執行FFT/IFFT需要256點,在OFDMA模式下運作則需要2,048點的FFT/IFFT。FFT是一種運算量相當吃緊的功能,需要大量的乘法器與具有嵌入式DSP模組的FPGA,必須用不同的數值來執行FFT,以提供理想的彈性平台。

FFT功能實行採用了Radix-2/4頻率消去法(DIF)的FFT演算法則,其轉換長度為2m,以及6‧m‧14,內部使用模組浮點架構,以便在轉換計算中最大化訊號的動態範圍。累加模組說明則是用於輸出到指示的任何資料比例之上,其過程會在轉換期間發生,以便維持精準度並最大化內部的訊號到雜訊比,轉換方向則是可透過在輸入埠的每個模組基礎上進行指定。

至於多重天線技術,在WiMAX系統中將可增加傳送與接收的範圍與穩定度。多重天線方案可提供不同的效益,包括陣列增益、差異增益與跨頻道干擾的抑制。802.16Rev. D目前支援數種多重天線選項,包括空時碼(STC)、多重輸入多重輸出天線系統與自適應天線系統(AAS)。這些方案牽涉到運算密集的演算法與操作,將非常適合在FPGA上實現。

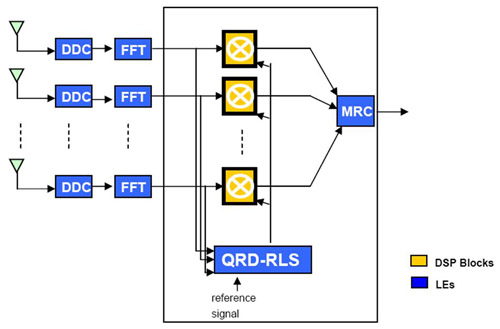

圖4描繪了實行AAS來執行接收波束合成的範例,首先會使用數位降頻轉換器(DDC)將來自不同天線的訊號向下轉換為基頻,然後使用FFT運算將其轉換為頻域。在執行最大化無線電合成(MRC)之前,複雜的加權隨後便會套用到訊號上,以最大化訊號到雜訊比。應用會從不同的天線複雜加權到訊號之上,其牽涉到複雜的乘法運算,然後會映射到在元件中可用的嵌入式DSP模組之中,加權的運算則是依據最小平方遞迴(QRD-RLS)演算法來使用QR分解。有FPGA廠商提供IP核心來執行自適應加權更新演算法,像是最小均方差法(LMS)、標準LMS(NLMS)、RLS與QRD-RLS演算法。

|

| 圖4 用AAS方案來執行波束合成 |

另外,Alamouti解碼器核心也有助在WiMAX標準中使用Alamouti空時碼來實行傳送差異選項,MIMO空間多工方案通常須要執行如QR分解、Cholesky分解與單數值分解(SVD)等矩陣分解演算法。

波峰因素抑制(CFR)或波峰到平均功率比(PAPR)的降低,是WiMAX這類OFDM架構系統的必要功能。如OFDM般的多重載波調變技術,將會產生具有波峰到平均值比高波峰因素的訊號,會進一步降低用於基地台傳送器中功率放大器的效率,功率放大器(PA)的運作點一般都會降低或是退去,以便容納輸入訊號的峰值。這個功能在PA輸出中將可維持線性化,並避免頻帶外輻射。具有高波峰因素的輸入訊號將需要被大量的退去,且將讓PA有較低的效率,因此減少輸入訊號的波峰因素相當重要,且可避免PA的效率掉到無法接受的層級。

在標準中特別指出隨機化可在資料將被傳送之時,透過收集相關聯的位元樣本,來減少所產生具有高波峰因素的訊號的技巧,另外一個技巧是透過剪輯訊號來減少PAPR,以便能夠跟隨頻域的濾波。在傳送器的IFFT輸出可以透過插入零值來進行竄改,並跟隨著非線性的剪輯運算。剪輯動作將可以增加頻帶外輻射,這將隨之帶來頻域濾波,其基本上會牽涉到額外的FFT與IFFT運算。

數位頻率轉換將可比傳統的類比技術提供更大的彈性與更高的效能,同時也將造成衰減與選擇性。它也可透過剔除掉所需的類比混合器與振盪器,來減少元件與製造上的成本。在數位升頻轉換時,透過數字化控制的振盪器(NCO)。所產生的可調整載波頻率,其所輸入的資料在求積調變之前的多重階段便已經被竄改。

想要實行可竄改基頻的有限脈衝回應(FIR)濾波器,有業者提供了可完全參數化的FIR編譯器IP,使用這種經過最佳化的FIR濾波器架構,將可以透過速度與面積的衡量方式來建立。舉例來說,具有分散式運算的完全序列化架構,將可以被使用於高頻寬的系統,另一種完全平行架構則可以使用在低頻寬的系統中。它也包括在內建的協同產生器中,將可以依據所需的濾波器特性來自動地計算FIR協同因素。

FPGA元件也提供NCO編譯器IP核心,將可以產生具有超過115dB無雜散動態範圍的振盪器,且其效能表現相當好。在實行多重載波升頻時,將會依據每個載波頻率來進行,並可以選擇最佳的FPGA資源來實行NCO,例如NCO可以使用特定的乘法器或記憶體,或是採用CORDIC IP來實行。數位降頻器(DDC)也可以使用與FIR編譯器,以及與NCO編譯器IP類似的設計方式。

除了上述的PHY層功能之外,其他功能包括數位預先校正(DPD)、排列、通道判斷等,都可以用於開發新的解決方案與創新的WiMAX產品,也可以幫助縮短產品上市時間,並開發與競爭對手解決方案有差異性的產品。

|

|

| |

如同先前所提及,加速WiMAX硬體設計的另一個重要需求是擁有易於使用的開發工具與軟體。 |

在快速原型端,由於WiMAX系統設計中牽涉到不同的DSP演算法,設計師在實行時通常會採用像是MathWork的MATLAB與Simulink環境等高階模型,在進行完功能驗證之後,便會使用硬體描述語言(HDL)再一次對演算法進行程式碼撰寫,這將造成較長的設計週期。DSP Builder工具整合了MathWorks MATLAB與Simulink具有VHDL合成、模擬的系統層級設計工具,可將演算法開發、模擬與驗證功能的這些階段合併在一起。DSP Builder可以透過幫助設計師使用對演算法相當親合的開發環境,來建立DSP的硬體描述,以縮短DSP設計週期。既有的MATLAB功能與Simulink模組可以與DSP Builder模組及矽智財(IP)結合在一起,以搭配DSP演算法所開發的系統層級進行設計與實行。

DSP Builder允許系統、演算法與硬體設計師共享通用,設計人員可以在樣品階段使用DSP Builder中的模組,以便在Simulink中建立硬體實行的系統模型。DSP Builder包含了位元與週期精確的Simulink模組,可以涵蓋計算或儲存功能等基本運作,並可以透過使用在DSP Builder模型模組中的IP功能,來將複雜的功能整合起來。

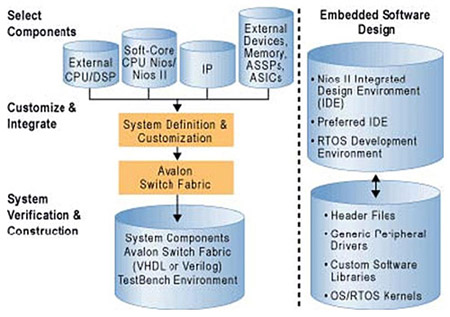

一些牽涉到WiMAX系統中的PHY與MAC層功能最好可以用軟體來實行,包括在MAC方面的排程器,以及PHY層的通道判斷等控制導向功能。這些功能可以有效率地透過FPGA內的軟式處理器來整合施行到FPGA中,並排除掉對分離式數位訊號處理器的需求。可編程單晶片系統(System on Programmable Chip, SOPC)設計,具有一般用途RISC CPU中的各種功能,在架構上特別針對廣泛的嵌入式應用進行設計。有的處理器系列由三種核心所組成,包括快速、經濟與標準核心,每個核心都針對特定的價格與效能範圍來進行最佳化。

如同圖5所描述,包含了內部的嵌入式處理器或FPGA外部的零組件與周邊,其中包括矽智財核心與客戶所建立的周邊核心,以及像是ASSP與ASIC等晶片外的元件。搭配標頭檔案與周邊驅動程式的匯出,SOPC Builder不但可以加速應用軟體的開發,更可以讓設計師專注在系統中的關鍵零組件,並且排除掉系統整合工作所需的工程時間,讓應用程式開發能夠更快地展開。

|

| 圖5 SOPC Builder設計流程 |

雖然在一個WiMAX產品初始時非常希望擁有靈活性,不過標準最終還是會確定下來,因此,須要綜合考慮WiMAX產品的靈活性,決定是否採用低成本ASIC實施方案。FPGA元件可提供結構化ASIC,能提供替代傳統ASIC的豐富功能。目前的ASIC設計產品開發成本越來越高,設計週期也越來越長,原因在於製程尺寸的縮小以及設計複雜度的提高。這些挑戰要求晶片製作必須首次成功,以避免耗時的高成本重製。

透過FPGA、設計工具、矽智財,以及從功能驗證的原型,到大量生產元件之間的無縫式整合途徑。有了HardCopy元件,相較於FPGA,使用者可以獲得平均達到50%的效能提升與接近40%的功率降低,並可確保在第一次製作矽晶片時便能獲得成功,工程師可以在他們的桌面使用類似的設計流程、架構、工具與IP,來展開FPGA或HardCopy元件的設計。

WiMAX是一種新興的科技,具有極大的市場潛力,並將對「寬頻無線網際網路存取」市場帶來重大的革命。各式各樣的硬體需求包括處理速度、整合性與產品及時問世等要素,都讓FPGA架構的實行平台成為首要之選。高密度的FPGA與HardCopy元件可讓WiMAX OEM透過開發時間與資源的最小化,儘可能第一次便成功與加速產品及時面世,進而擁有巨大的競爭優勢。

(本文作者為Altera亞太區資深行銷經理)