SEU對裝置可靠性的影響,已逐漸從太空延伸到醫療電子等高可靠性的應用。事實上,FPGA元件各邏輯間的連結技術,將影響元件對於SEU免疫的程度,分析目前快閃、反熔絲與SRAM的FPGA,基於前兩技術的FPGA可有效防範SEU問題;而SRAM FPGA則僅能抑制。

隨著積體電路(IC)線寬不斷縮小,元件更容易受高能粒子的影響而發生單一事件擾亂(Single-event Upset, SEU),特別是元件中的靜態記憶體結構最值得關注。這些風險在太空領域已早被意識到,如今這種擔憂也正在蔓延到其他領域,例如網路、航空電子、汽車及醫療裝置。醫療裝置不僅會受到自然環境存在的宇宙射線影響,而且還得在現代醫療機構中常見的輻射環境中工作。因此醫療裝置設計人員在選擇產品所採用的技術時,也須要考慮裝置是否容易受SEU影響。

粒子碰撞輻射效應造成記憶體SEU

互補式金屬氧化物半導體(CMOS)記憶體結構,如靜態記憶體單元和正反器,在受到高能粒子轟擊時容易發生擾亂(即狀態改變)。這些高能粒子可能是阿爾法(Alpha)粒子、中子、質子或各種重離子,是由宇宙射線與大氣外層中的粒子碰撞,或宇宙射線釋放的粒子與宇宙射線二次碰撞產生。

宇宙射線簇射的主要成分是中子,其次是占地球表面中子通量7~32%的質子。這些粒子的其他來源包括封裝和矽基板本身。IC的封裝材料含有微量的鈾和釷,這兩種元素都會產生高能阿爾法粒子。此外,大量硼元素被使用在多晶矽摻雜、基板摻雜,或硼磷矽玻璃(BPSG)中。當這些常見的硼同位素(10B)之一被某一低能量(熱能)中子擊中,即所謂中子捕獲,就會產生一個鋰離子和一個阿爾法粒子。如果基板中硼元素和宇宙射線中的低能量中子達到一定濃度,這種輻射效應將相當顯著,由於這些粒子的源頭都在元件內部,因此,再多的外部遮罩措施也無法阻擋這些粒子。

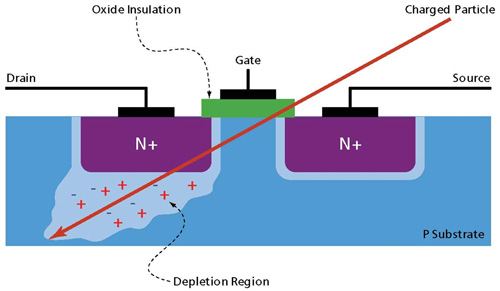

當一個高能粒子(如中子)撞到基板上,將與基板內的原子碰撞,釋放一群帶電粒子,會留下一道電離痕。這種電離作用會產生足以使閘極過壓,從而改變記憶單元的電荷(位元翻轉),這種記憶體單元的狀態變化被稱為SEU(圖1)。

|

| 圖1 帶電粒子造成SEU |

記憶體單元的這種擾亂狀態是暫時性的,在下次寫入或重置(如重新供電)時,擾亂就會被清除。目前還未見到SEU導致電路永久性損壞的情況。記憶體電路的SEU敏感性隨著元件的更新換代而增加,隨著製程尺寸的縮小,下列情況也隨之發生:

其結果是記憶體單元的SEU敏感性增加。所以原本僅在太空應用中才須關注的問題,如今甚至成為地面上,在設計如醫療設備等的高可靠性設備時所須注意的挑戰。

FPGA邏輯陣列連接影響SEU敏感性

不同現場可編程閘陣列(FPGA)有許多共同特點,包括都有一個邏輯模組陣列,即FPGA基礎架構、一組嵌入式記憶體,可能還有一些其他特殊構件,如乘法器或數位訊號處理器(DSP)、時鐘管理電路,如鎖相迴路(PLL),以上這些都由周邊可程式輸入/輸出(I/O)連結。不同FPGA產品系列間的關鍵差異之一是邏輯陣列,不同供應商FPGA產品系列的邏輯模組所採用的具體結構和模組互連方式都不同,而這種互連方式正是SEU所關注的重點。

FPGA有兩種走線方式:金屬連接和通孔連接。而FPGA中的通孔是可程式的,是構成整個可程式邏輯技術的基礎,也用於各邏輯模組和整個元件的配置設定。FPGA產業中採用三種類型的通孔連接技術,包括反熔絲(Antifuse)、快閃(Flash)和靜態隨機存取記憶體(SRAM)。

| ‧ |

|

| |

|

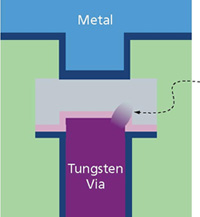

| 圖2 反熔絲技術示意圖 |

反熔絲通孔(可程式鏈路)(圖2)是一種金屬間的可程式互連元件,位於最上面的兩個金屬層之間。反熔絲一般處於開路狀態,且當燒錄後就形成一個永久性的被動低阻抗連接,由於對反熔絲燒錄需要多個高壓脈衝,因此,高能粒子無法改變其燒錄後或未燒錄狀態。反熔絲幾個主要特點,包括一旦程式燒錄後,無法再重新燒錄;燒錄反熔絲所需能量較高;燒錄是在外部進行,為原始設備製造商(OEM)製造過程的一部分;屬靜態結構(斷電後仍保持其狀態),不涉及任何電晶體,以及具備SEU免疫能力。

|

| ‧ |

|

| |

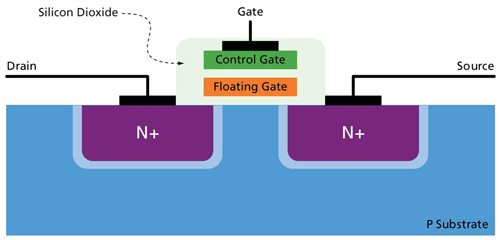

基於快閃技術(圖3)的FPGA中,採用的互連元件是快閃開關。與所有快閃記憶體相同,這些快閃開關燒錄後的狀態是非揮發性的。對一個快閃開關進行燒錄/清除需要的電壓和能量遠遠高於宇宙射線誘發的粒子所產生的電壓和能量。

快閃開關的主要特點包括可重新燒錄;燒錄互連快閃開關所需的能量較高;屬靜態結構(斷電後仍然保持結構狀態),以及擁有SEU免疫能力。 |

|

| 圖3 快閃開關技術架構圖 |

| ‧ |

|

| |

基於SRAM的FPGA中的基本可燒錄通孔是一個僅有1位元的SRAM單元。這種SRAM通孔的燒錄和擦除方式與其他SRAM記憶體一樣,雖然SRAM通孔比一般SRAM元件更可靠,但其狀態也很容易被宇宙射線引發的輻射撞擊所產生的電荷改寫。

SRAM通孔主要特點為,可重新燒錄;燒錄所需能量較小;燒錄本質上就是對通孔儲存位元的寫入操作;由多個電晶體構成的易揮發性結構(斷電後結構狀態被清除),以及易受SEU攻擊。 |

醫療設備日益關注SEU問題

1998年Bradley和Normand報導可植入心臟除顫器發生SEU的事件,該報告提出植入醫療設備上發生的宇宙射線輻射效應臨床數據資料。

加拿大的St. Jude Medical於2005年向醫生發出建言,警告可植入心臟除顫器的記憶體若發生SEU事件,可能造成設備電池過度耗電。

除Bradley和Normand曾研究的在地表上誘發的錯誤外,現代醫療設備,如可攜式輸液泵、飛機上使用的心臟除顫器、起搏器,以及植入式心臟除顫器,都必須能在民航飛行環境(中子通量較大的飛行高度)中運行。

電路的出錯率通常與運行環境中相對中子通量成正比。兩極航線附近40,000英呎飛行高度的中子通量,大約是美國紐約市地面(JESD98A定義的參考點)的六百倍,這個通量意味著在飛機上運行的設備的SEU風險大幅度增加。因此,運行在兩極附近飛行高度設備的失效率(FIT)大約是低海拔設備的六百倍。

然而,宇宙射線和元件材料並非醫療設備環境中電離輻射的唯一源頭。隨著新技術如利用電離輻射殺死癌細胞的治療方法的興起,設計人員也須考慮局部產生的粒子通量。事實上,研究人員曾研究過運行在高能模式下Varian直線加速器(LINAC)產生的通量,研究指出,一般的放射治療室中的擾亂事件率達每天38SEUs/MB。對現代電子元件的儲存內容而言,這個出錯率的確相當可觀。

SEU抑制與免疫措施重要性日增

無論是基於SRAM、快閃,還是反熔絲技術的FPGA,都含有容易發生SEU的SRAM區塊和正反器。正反器是最穩健的記憶體結構,僅在高輻射環境中如太空,才會出現擾亂。抑制正反器錯誤的措施眾所周知,如可透過三模組冗餘(Triple-module Redundancy, TMR)實現。SRAM區塊的擾亂也可借助一些用於檢測和糾正其他錯誤的標準技術,如檢錯糾錯電路(EDAC)抑制。這類記憶體結構的擾亂可歸類為軟錯誤,且只要有抑制措施,就不會蔓延到系統其餘部分。

基於SRAM的FPGA還有另一個與SEU事件相關的憂慮,即FPGA元件的配置記憶體部分本質上是一個大容量SRAM,因此,配置記憶體一旦發生SEU事件,就會以兩種方式之一改變元件的功能性,例如改變走線連接狀態,使原設計中不連接或斷開的線路發生連接或短路,以及改變配置,因而改變邏輯單元和I/O結構的功能,如將某一輸入變成輸出。

|

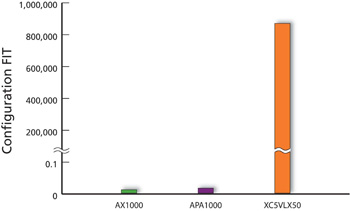

| 圖4 基於反熔絲、SRAM和快閃技術的FPGA的系統擾亂率預測 |

這些錯誤相對於軟錯誤,稱為韌體錯誤,因為會影響元件的功能,且不能即時更正。由於基於SRAM的FGPA中的配置記憶體位元眾多,潛在的SEU風險對系統的穩定性影響極大。如賽靈思(Xilinx)自行估計,工作在40,000英呎高度、中子通量環境中的小容量Virtex-5元件(XC5VLX50),其配置記憶體出錯率是570,125~809,971 FIT,即平均故障間隔時間(MTBF)相當於1.23~2.61個月(圖4)。

由於對SEU的認識逐漸加強,基於SRAM的FPGA製造商提出各種抑制技術。最簡單的方法是直接定期重新配置FPGA,清除積累的任何錯誤。這種方法要成功,設計人員必須確定潛在錯誤的影響,以及這些錯誤蔓延所需的時間,並在這個時間段內重新配置FPGA。雖然錯誤仍會蔓延,但潛在的損害已被重新配置限制。此外,FPGA內的功能僅在重新配置完成之後才可使用。

新一代基於SRAM的元件,使用者可利用配置引擎中,內建的錯誤檢測機制。利用配置記憶體回讀(Readback)功能,可計算每個組態配置資料的迴圈冗餘校驗(CRC)值,並與某一標準CRC比較。如果檢測到不一致情況,則有SEU發生,應用程式就會重新配置FPGA。

另一方面,應用程式也可嘗試糾正錯誤,於背景模式下重寫配置資料。同樣,雖然錯誤仍然會蔓延,但其處於未糾正狀態的時間大幅減少。

無論採用何種方法,抑制都是事後糾錯,換句話說,抑制是試圖減少錯誤的影響。在各種情況下,糾錯方案只能處理配置記憶體中單一位元上的錯誤,多個位元發生錯誤時就須重新配置元件,且實現抑制方案須耗費額外的可靠性分析和工時。所以不可將抑制與免疫視為相同。採用抑制措施後,錯誤仍然會出現,並會在系統內蔓延。

SEU引發責任性問題

除對醫療設備(甚至採取了抑制措施的設備)中潛在SEU事件引起的可靠性擔憂外,潛在的錯誤也產生責任性問題。若某一廠家採用已知易受SEU影響的元件,就可能捲入疏失擔責的糾紛,直線加速器在治療過程中突然失效,產生過量輻射即為一例。若控制電路都在一個FGPA中,人們會認為是某個SEU事件導致該設備失效,而廠家採用此種易受錯誤影響的技術將有過失。

使用具有SEU免疫能力的FPGA不僅能夠簡化系統設計,而且還能讓設備廠家免於任何潛在的法律糾紛。與基於SRAM的FPGA不同,基於快閃和反熔絲的FPGA不會發生配置擾亂,即SEU不會影響配置。因此,設計人員既不必分析這些錯誤對系統的潛在影響,也毋須設計和測試抑制方案。

基於SRAM的FPGA中的配置記憶體先天就有SEU脆弱性。這種脆弱性會導致元件設計功能改變,進而影響病人的生命安全。要抑制這些錯誤,必須清楚了解它們對系統可靠性的影響。相反的,基於快閃和反熔絲的FPGA不會發生配置錯誤,具有更高的系統可靠性。

(本文作者為美高森美SoC產品行銷經理)