在使用每秒千兆次採樣(GSPS)類比數位轉換器(ADC)時,促使相同系統中多重轉換器同步化的需求與之相同非常重要,然而速度以及介面讓這件事難以達成。

使用確定性延遲或是JESD204B介面資料字組當中的控制位元兩種方法,都是JESD204B Subclass 1的特點。

事實上,多重ADC同步化在航太與國防工業當中是一項基本要求,因此市面上的ADC為能夠促進多重轉換器同步化,會兼具12位元、2.5GSPS等特性,並以此做為該元件的標準特點。

同步化的定義是能夠只依據ADC的孔徑抖動、時脈抖動及時脈分配精確度,而使每個轉換器匹配至相當於或是低於單一時脈週期精確度的能力。目前,新款ADC主要採用符合標準JESD204B介面技術的高速串行資料通道。

時間戳記利於大量轉換器同步化

其實,以JESD204B為基礎的轉換器在市場上仍然是相當新的元件,許多使用者第一次採用此項技術對同步化多重元件的能力多所顧慮。然而,若使用簡單的平台測試設定,進而將兩組轉換器同步化並展示其可擴展性,應該就可以紓解部分或是所有顧慮。

要將多重GSPS轉換器一起同步化有兩種獨特選項。第一種方案是使用確定性延遲,其中的延遲必須要針對個別獨立的資料路徑加以調整,藉以修正時序的不匹配。

|

| 圖1 測試設定及其主要相互連結方塊圖 |

第二種選項使用一般被稱為「時間戳記」的方法。其不須要量測每一個轉換器到每一個現場可編程閘陣列(FPGA)的時間延遲,對於大型系統而言特別重要,因為可能會有架設於地面的雷達系統得使用數百個轉換器的潛在需求。

會因同步化而受益的關鍵性應用就是雷達。在這種案例當中,絕對的時間量測結果是不需要的,設計者只須要考量從一組接收元件到下一組元件的相對時間即可。

|

| 圖2 AD9625 FMC電路板w/同步連結 |

在使用時間戳記時最後的資料處理比較沒有那麼密集,因為FPGA或是處理器只需要在每組資料集合中搜尋一個時間標記,透過這個時間標記可以讓設計者針對每顆轉換器路徑從經過定義與同步化的點去將資料對齊,毋須擔心在大量轉換器/FPGA對組中,每顆轉換器到各自FPGA走線長度的距離。此路由甚至可能會穿過多重電路板,使其在應用設計當中更有助益。

業界近期推出的ADC使用的是對於如何執行此同步方法相當重要的Subclass 1。Subclass 1使用SYSREF訊號來對齊串聯輸出資料;將時脈置入轉換器的輸入資料當中,這樣的安排讓SYSREF能夠與轉換時脈同步,並且確保每組分配的SYSREF訊號會在相同時間送達每組轉換器。

這將會產生出一個要放置於JESD204B串聯輸出資料中的標記或是時間戳記,藉以顯示出同步資料分析應該要開始的確切點。

|

| 圖3 電路板連結至開發平台上的FMC1、HPC插槽。 |

當然,新元件會提供兩種使用這個標記的選項。設計者可以使用整個16位元JESD字組中任一部分的獨立控制位元,或是以SYSREF時間戳記取代轉換器的最低有效位元(LSB)。值得注意的是,這些控制位元的執行及用來將多重轉換器同步化的方法並非JESD規格的一部分,在JESD字組中每個控制位元的命名則留給每個獨立轉換器設計去斟酌,而且在不同轉換器之間可能會有所差異。

相位匹配纜線確保時脈同步化

圖1的設定顯示如何將兩顆轉換器同步化。然而理論上來說,能夠加以同步化的轉換器數量是沒有限制的,以經過適當設計的轉換器電路板開始(圖2、圖3),有關於測試的設定需要如下的設備。

訊號產生器為每一顆轉換器(SMA100A)提供2.5GHz的取樣時脈,接著單一輸出會由5350-244 Picosecond Pulse Labs功率分配器拆解成兩組時脈,從這兩組拆解之後的輸出會有一對相位和長度匹配的纜線連結至每組轉換器電路板,可確保時脈在抵達每顆轉換器時是處於同步化的狀態。

脈衝產生器的任務是產生SYSREF訊號,是特別針對此項任務而挑選的,因為該元件能以合理的低抖動提供多重差動輸出;且具有將一組差動輸出相對於另一組差動輸出加以扭曲的能力,此將可以實現把SYSREF訊號位置依據需要以相對於取樣時脈而移動的能力,進而確保設定與保持時間不會相違背。

接著類比輸入也必須能以相同於取樣時脈的方式加以拆解,而使用另一組具有一對相位匹配纜線的功率分配器可確保類比輸入訊號能夠在相同的進入時間抵達每組轉換器的輸入。

|

| 圖4 時間域中原始資料的Matlab重建 |

範例中的轉換器電路板透過一組HPC FMC連結器連結評估用平台。Chipscope與軟體開發套件(SDK)軟體工具被用來與平台連結,並且執行時間戳記程序和擷取資料。

為了手動觸發SYSREF,必須啟動脈衝產生器以便將SYSREF訊號與每一組轉換器對齊,在偵測到SYSREF標記後,每一組FPGA會執行一次資料擷取。一旦資料被成功擷取之後,就會被輸出到Matlab中進行處理。

同步化的結果

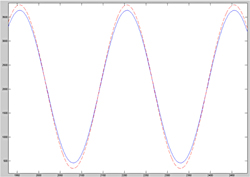

將輸出至Matlab的原始資料分析完之後,來自於每顆ADC的時間域重建資料就可以繪製在上面,如圖4所示。

|

| 圖5 圖4上升緣的放大檢視。 |

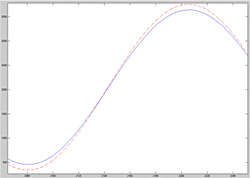

圖5所示為圖4中上升緣的放大檢視。水平軸所代表的是取樣。介於實線與虛線之間的三角代表的是兩組獨立而且同步化的ADC/FPGA擷取,直觀上看來此似乎遠低於一個取樣偏差。

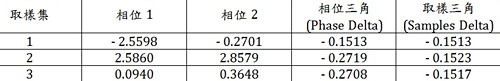

表1重新檢視取樣相位三角的子集,因為它與圖1以710MHz類比輸入之測試的組態設定有關。

|

| 表1 取樣相位三角的子集 |

供應同步取樣時脈/SYSREF輸入 新款IC鎖定時脈

以上的測試結果顯示的是在710MHz下運作的類比輸出,而三組個別獨立的擷取會產生相似的精確結果,每個結果仍然都是同步於±0.5個取樣之內。重要的是,在測試設定中要將兩組源極加以相位鎖定,以便提供同步取樣時脈與SYSREF輸入;假如那兩組邊緣會隨著時間彼此相對的移動,而非相位鎖定的話,那麼統計上的期望值最終就會經常違反設定與保持時間。

透過市場上嶄新以及即將推出的JESD204時脈分配積體電路(IC),每組時脈與SYSREF輸入的相位鎖定將可以自動的獲得照管。

雖然這種方法使用大量的笨重工作台測試設備,卻能很快的藉由新款時脈元件來執行相同的同步化設定,除驗證兩組轉換器同步化,這種概念也可以放大至包含多組轉換器的情況,像是雷達、電子戰,以及軍事通訊應用等領域都能因為在GSPS速度上的新能力,而大幅獲益。

(本文作者皆任職於美商亞德諾)