現代電子設備和裝置在上市之前,都必須先通過當地電磁干擾/電磁相容性(EMI/EMC)的標準與法規檢測。以美國為例,聯邦通訊委員會(FCC)即針對電子裝置所產生的輻射電磁(EM)場,制定了最大功率限制。

為符合如此嚴格的要求,設計工程師在設計電路時,必須想辦法將輻射放射量(RE)降到最低。

掌握六大實作方法 設計人員輕鬆實現低EMI印刷電路板

在電波暗室執行EMI相容性測試之前,先得執行這些步驟,其中包括最低輻射的電子電路設計及兩種先期認證檢測--利用3D電磁軟體進行印刷電路板(PCB)布局模型的模擬EMI分析,以及使用頻譜分析儀進行PCB原型的近場電磁掃描。

磁珠可降低電磁干擾

在設計電子電路或布局PCB時,運用最佳實作可實現低RE。舉例來說,EMI濾波可藉由在訊號端(如電軌、USB資料線、乙太網路(Ethernet)等)加入一些磁珠(Ferrite Bead)來實現。

放置充足去耦合電容

沿著電軌適度放置充足的去耦合電容,以便將電網阻抗降到最低,進而減少數位負載造成的雜訊鏈波之振幅、降低輻射風險。

設計閉迴路補償網路

另外,精密設計的交換式電源供應器之閉迴路補償網路,可實現穩定的閉迴路,讓電壓輸出端的振盪獲得控制,進而將切換雜訊鏈波的振幅減到最小。雜訊鏈波越小,產品原型的EMI風險就越低。

利用走線參考路徑

針對具高頻或高訊號緣變化率的訊號,將其PCB走線參考至連續回返路徑(即參考接地面),以降低EMI風險。要注意的是,走線不可跨越任何分離平面(Split Plane)或空隙(Void)。

當訊號從其中一層經由導孔傳到另一層,設計人員至少應在訊號導孔的旁邊放置一個穿引導孔(Stitching Via),以作為適當的引導路徑,讓回返訊號電流從接收端回傳到傳送端,若沒有適當的參考路徑,則回返電流可能會流到PCB內的任何點位,並成為潛在EMI來源。

留意阻抗匹配

阻抗匹配也是重要的考量因素,因為PCB上面的傳輸線若具有不匹配或不連續阻抗,可能會造成訊號在沿著線路進行傳輸時,於傳送端和接收端間出現反射,因而引發由高頻成份構成的振鈴現象。

這可能會經由串音干擾(Crosstalk)耦合到電路的其他區塊,並且有可能會從PCB往外輻射。將阻抗不匹配降到最低的方法包括導孔和表面黏著技術(SMT)焊點的最佳化、妥善配置傳輸通道的終端(即串聯或並聯),以及在傳送端和扇出之間加入緩衝以縮短支線長度。

加大線寬

藉由三倍以上的線寬來分離訊號,進而減緩串音干擾。因為高頻雜訊有可能因為裝置的PCB內具有電容性或電感性成份而產生耦合,於是對附近的其他電子裝置來說就變成一種輻射干擾源。

其實,若想將EMI威脅降到最低,完美的接地方案同樣也很重要。在任何一種PCB設計之中,都必須避免產生接地迴路,因為它會在回返訊號電流流過的時候成為輻射發射器。

要實現優秀的接地方案,可以將接地設計為寬廣的參考平面。不同類型的電路(即射頻、類比和數位),其接地平面在實體上應該予以分隔,但在電性上透過磁珠加以連接,如此便可幫忙防止高頻雜訊擴散到其他類型的電路。

一旦PCB妥善完成布局之後,應進行布局後的模擬EMI分析,以便在PCB開始製造之前能確保其具有低RE風險,也可幫忙避免金錢和開發時間的浪費;若沒有進行EMI模擬的話,PCB有可能會具有糟糕的EMI特性而必須重新進行設計。

設計人員在確認EMI模擬結果符合規範之後,就可以開始進行PCB的製造,並接著可以使用頻譜分析儀對PCB原型進行近場電磁掃描。這些先期認證檢測(EMI模擬和近場電磁掃描)可提升對原型設計的信心度,確認其具有低EMI的特性。

在先期認證檢測完成之後,待測裝置(DUT)就已經準備好在電波暗室進行真正的EMI相容性測試。

有限元素法可模擬EMI分析

前面提到的最佳實作和關鍵步驟可將產品原型的EMI降到最低,舉例來說,在PCB設計布局完成之後,將布局檔匯入3D電磁模擬軟體(如EMPro 2013.07)以進行3D EMI模擬。

|

| 圖1 PCB布局的3D模型 |

圖1所示的範例為匯入PCB後的3D模型,其中包含實際的疊構(Stackup)資訊,並以一對差動訊號(以深色走線標示),利用軟體的有限元素法(FEM)模式來進行3D電磁模擬。

|

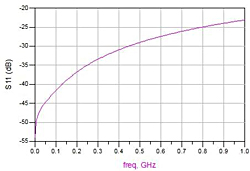

| 圖2 回返損耗的模擬圖 |

透過設定模型的電磁邊界條件及網格大小,3D電磁模擬可實質解出馬克斯威爾(Maxwell)方程式。若想達到更高準確度的模擬結果,邊界大小應設定為PCB厚度的八倍以上,網格的設定必須小於PCB寬度的五分之一。此外,執行3D電磁模擬的電腦至少應具備16GB的記憶體和100GB的儲存空間要,才能確保分析流暢地進行。

|

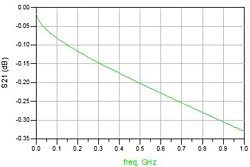

| 圖3 插入損耗模擬圖 |

在選擇的差動訊號走線每一端放入小訊號的激發埠,並執行S參數模擬,其回返損耗的模擬圖如圖2所示。以這一對差動走線來說,在30M~1GHz的範圍有較低的回返損耗(即低於-20dB的曲線),表示訊號反射較小,可以降低訊號振鈴效應的風險。

訊號反射現象可透過回返損耗(即S11)方程式加以解釋,如方程式1所示,為反射波對上注入波,以對數的尺度比例表示。此外,反射效應也可用插入損耗(即S21)模擬圖來表示,如圖3。

|

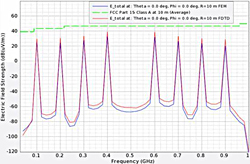

| 圖4 強度(bBuV)對頻率(GHz)的模擬EMI圖 |

..................................方程式1

趨近0dB的曲線顯示大部分的注入訊號會傳送到接收端,這代表訊號的反射為最小。訊號傳輸的效率如代表插入損耗(即S21)的方程式2所示,為傳送波對上注入波的對數尺度比例。

..................................方程式2

方程式1和2的Vr表示傳送端的反射訊號;Vt為接收端的傳送訊號;Vi則是來自傳送端的注入訊號。

要設定遠場感測器來擷取放射電磁場,設計人員可利用EMPro或類似軟體中的EMI放射計算功能可算出遠場放射功率。在此一範例中,電場距離設定在10公尺,同時可繪出其在頻域中的響應,然後在時域有限差分法(FDTD)模式中重複進行3D電磁模擬以便與FEM比較。

接下來可畫出30M~1GHz頻率範圍的模擬電場強度,如圖4所示。值得注意的是,輻射功率大小(曲線A表FEM模式,而曲線B表FDTD模式)低於FCC所制定約45dBuV(虛線)的最大臨界值。

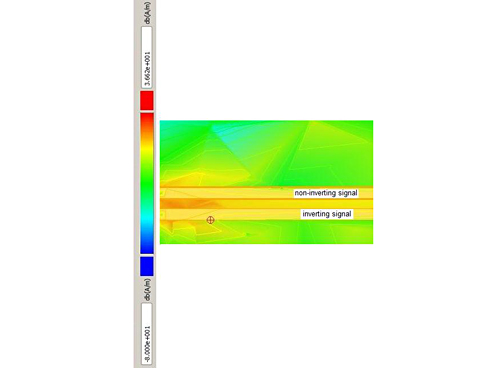

有些3D電磁軟體可以透過3D模型,讓工程師檢視不同距離和不同軸的電磁場分布(以動畫方式呈現),圖5即為一張動畫式電場的截圖,能呈現PCB頂層的電場強度。電場強度的大小(單位為dBA)顯示在圖的左邊,而反向的電場極性以負號數值來表示。

|

| 圖5 模擬電場分布 |

軟體工具能有效掌握量測結果

|

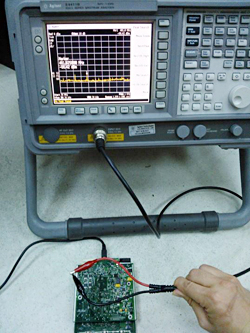

| 圖6 藉由頻譜分析儀進行近場電磁掃描的測試配置 |

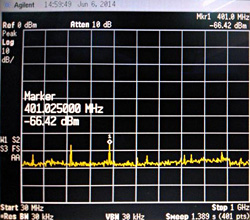

PCB原型在製造和組裝完成之後,會利用頻譜分析儀進行近場電磁掃描,測試配置如圖6所示,連接到分析儀的單圈線圈可擷取到原型所發射出來的近距離磁場。涵蓋30M∼1GHz的頻域波形如圖7所示。

具有最高功率強度(也就是-66.4dBm)的突波會出現在400MHz;當做近距離感測器使用的線圈會在待測物周圍3吋的距離內操作。頻譜分析儀的解析頻寬通常會設定在30kHz,以達到較低的量測雜訊底線(-80dBm),同時也能確保突波(在各個離散頻率的RE)清晰可見;若想在電波暗室以更高的信心度通過遠場(分別為3和10公尺)EMI相容性測試,近距離的突波功率強度就要在-65dBm以下。

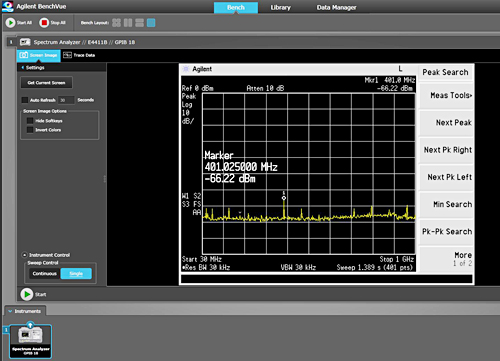

市面上的測試儀器如E4411B,可透過Ethernet或GPIB介面連接到電腦和智慧型行動裝置(智慧型手機或平板電腦),並透過BenchVue軟體工具進行管理,如圖8所示,軟體工具可透過網際網路在世界各地遠端控制測試儀器,並即時檢視量測結果。

|

| 圖7 以電磁場功率(dB)對頻率(Hz)方式顯示的電磁掃描的量測圖 |

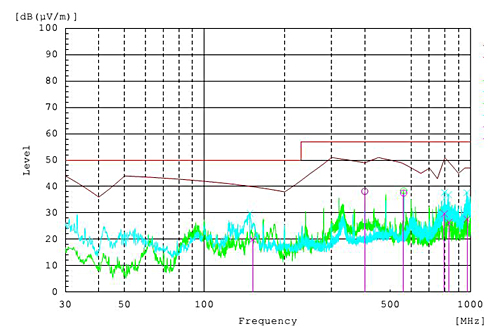

最後,產品原型須進到電波暗室執行3公尺的遠場EMI相容性測試。3公尺RE的結果,如圖9所示,A線代表CISPR 11 Class A電子裝置最高的RE功率位準,從30M∼1GHz須低於56dBμV;輻射波的垂直和水平成份分別以C、D曲線表示。出現在400和560MHz的兩個峰值充分低於最大臨界值,分別測到38dBμV和37dBμV的功率位準。

|

| 圖8 軟體工具可執行電磁掃描並顯示量測結果圖。 |

在設計電路時,若要避免不必要的PCB重製,低EMI和先期認證檢測(也就是3D EMI模擬和近場電磁掃描)遂有其必要性;也能因此省下開發成本和時間、縮短在電波暗室進行遠場EMI相容性測試的時間,也就是說,這些步驟保證能加快電子裝置的上市時間。

|

| 圖9 3公尺RE測試的結果,A線下方鋸齒狀的B線代表是德EMC準則所設定的保險區。 |

(本文作者任職於是德科技電子量測事業群)