在裝置上進行機器學習(ML)是大家熱議的現象。有能力作出獨立決定的智慧裝置,並依據本地產生的數據採取行動,被譽為是消費裝置運算的未來。

在裝置上處理可減少延遲、提升可靠性與安全性,提升隱私與安全,同時還能節省功耗與成本。

驅動邊緣

儘管邊緣裝置的機器學習在短時間內已有相當進展,且全新的網路、演算法與不同的架構近幾年來也相繼問市,但推論引擎的基本運算需求依舊維持不變。由於機器學習是一種重覆與精細化的過程,目的在於理解數量龐大的資訊後形成結論,大部分功能性的提升仍仰賴數據的高吞吐量與高效率來驅動。

變更CPU、繪圖處理器(GPU)或數位訊號處理器(DSP)以實作推論引擎,可說是為邊緣裝置增添機器學習能力的簡便方法。例如,許多嵌入式裝置需要的只是小型、低功耗的微控制器單元(MCU),而目前市場上絕大多數的智慧型手機都在CPU上運行精準、高效能的機器學習。但是當回應性或功耗效率極為關鍵時,CPU可能很難符合其所需的效能要求,而專用的類神經網路處理器(NPU)例如Arm機器學習處理器,可能是較妥善的解決方案。

機器學習處理器

與CPU、GPU及DSP相比,機器學習處理器具有最佳化的設計,透過高效率的卷積、稀疏與壓縮技術,效率可大幅提升。 以Arm針對機器學習工作負載推出的異質運算平台Project Trillium來說,其中一環就是利用可擴充的架構達成即時回應所需的運算確定性,同時提供能跟上演算法快速演進所需的彈性與可編程性。

效能

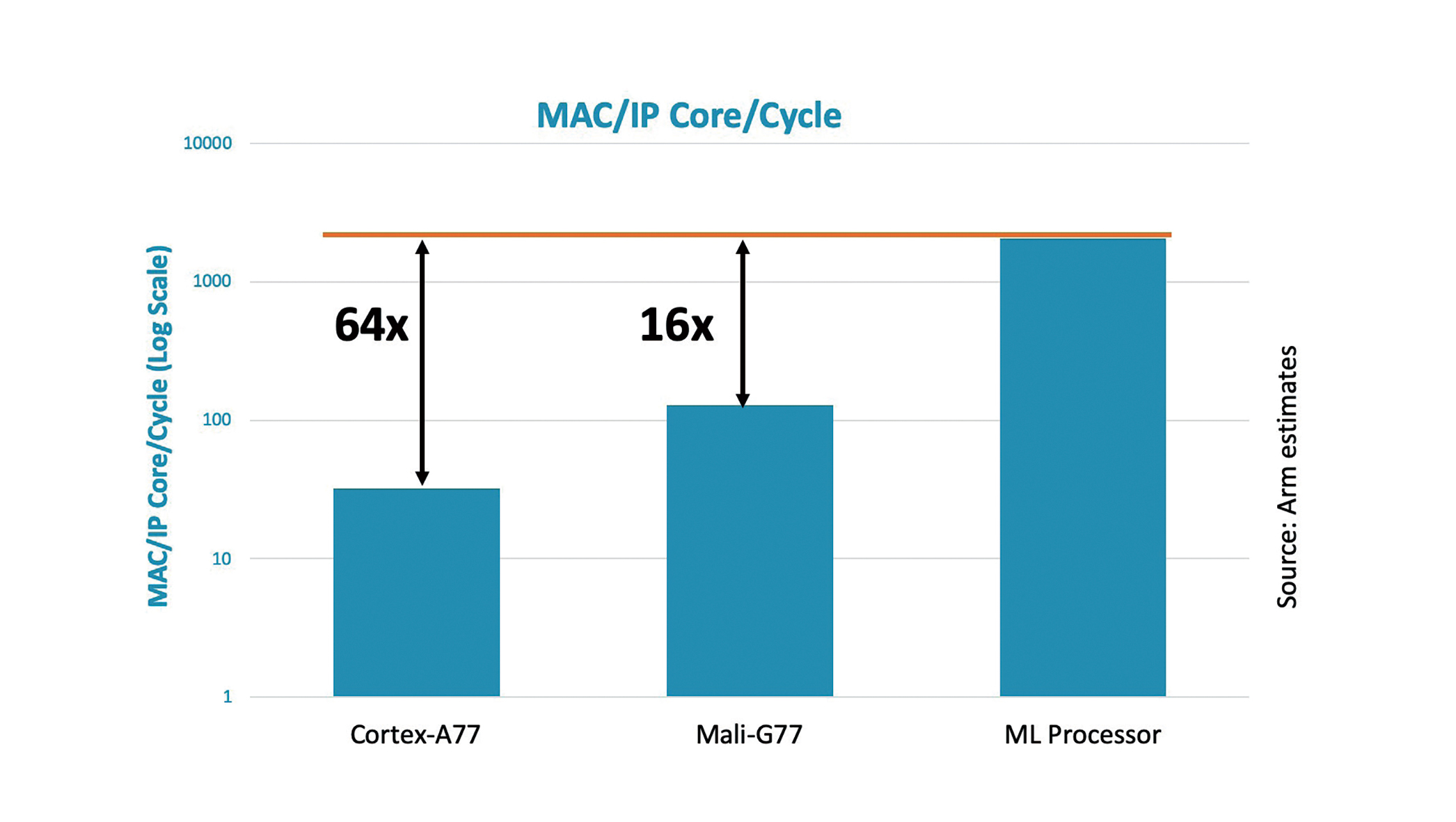

機器學習處理器可以驅動快速、精準的推論,同時保有效率與效能。有鑑於多數邊緣裝置都是體積相對較小、以電池驅動的系統(也就是電池的容量有限),選用機器學習處理器可以給影像監控攝影機更長的運作時間、無人機更長的飛行時間,或電動車更長的行駛距離。 高效能若要發揮作用,就必須搭配效率。機器學習處理器最快可以每秒4TOP的高速吞吐量執行卷積,並在7奈米的尺度內達成每瓦5TOP的高效率運算率(圖1)。

圖1 ML處理器提供<4TOP/s的單核心性能和<5TOPs/W的效率

圖1 ML處理器提供<4TOP/s的單核心性能和<5TOPs/W的效率

多核心效能具可擴充性

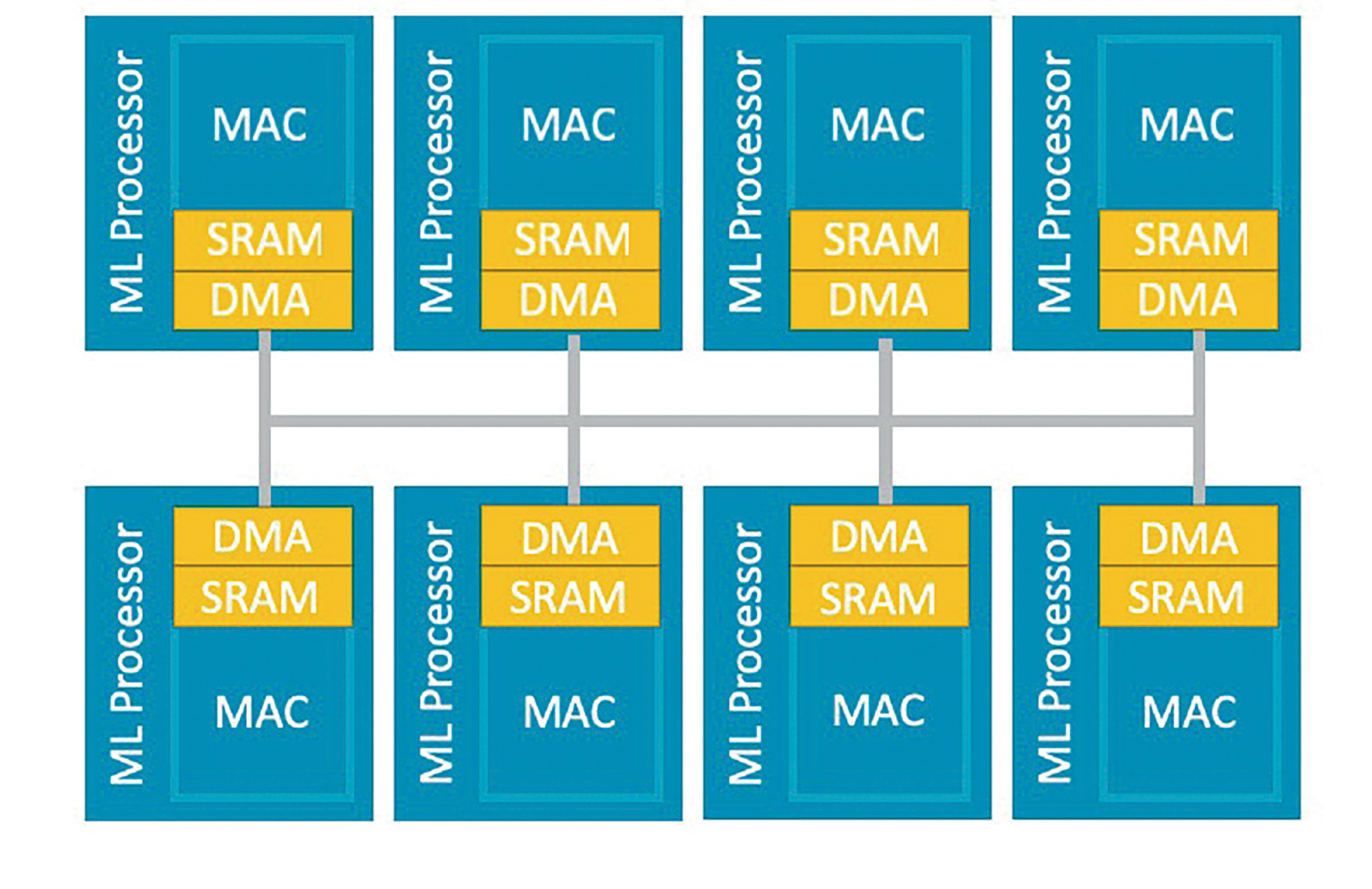

機器學習處理器同時支援多核心的配置,可促成像高解析分隔等要求較高的使用場景。

.<32TOP/s

使用緊密耦合叢集方式最多可安排8個處理器,它們能夠平行處理多個網路,或是由各個核心共同處理單一的大型網路(圖2)。

圖2 多達8個核心,32TOP/s,緊密耦合

圖2 多達8個核心,32TOP/s,緊密耦合

.>250TOP/s

較大型的配置則可透過Arm CoreLink Interconnect網狀結構互連技術獲得支援。

如Arm將類神經網路軟體框架捐贈給Linaro機器學習計畫(Linaro Machine Intelligence Initiative),該計畫目前正以完全開源的方式進行開發。

效率

高效能若真能發揮作用,就必須搭配效率。機器學習處理器提供良好的每瓦5TOP功耗效率,這種高效率是透過像類神經編譯、高效率卷積與頻寬降低機制等尖端技術最佳化而成的。

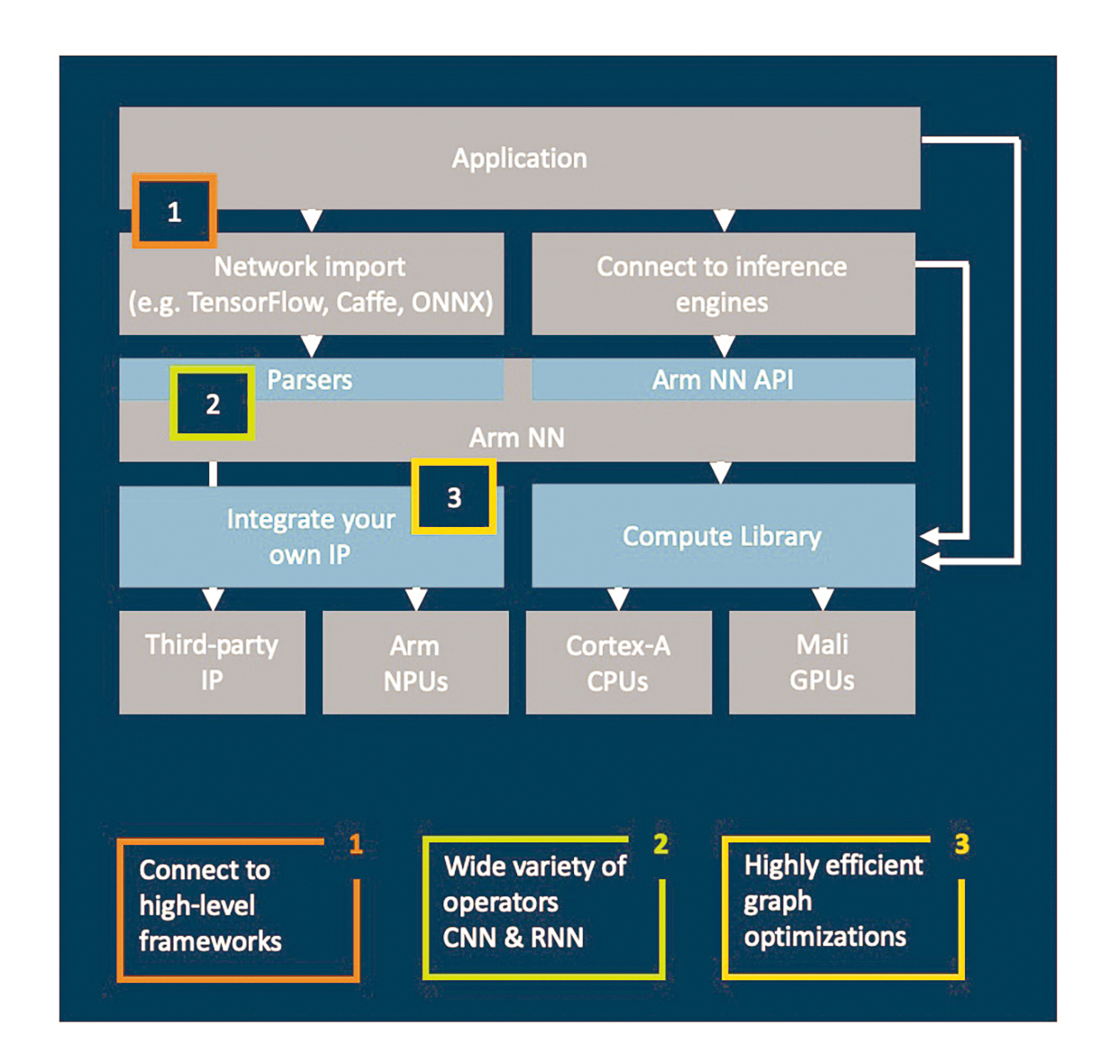

這個處理器獲得Arm類神經網路軟體框架(Arm NN)的支援,Arm NN則是可以促成完整、未來也可適用之解決方案的開源軟體。實作相當簡單的Arm NN可以在TensorFlow、PyTorch與Caffe等現有框架內,促成高效率的NN翻譯,並將編譯工作分布到Arm Cortex CPU、Arm Mali GPU與機器學習處理器上運行。這樣就可以降低特定處理器最佳化的需求,並減少在不同硬體相關的軟體投資。

NN操作

1.把機器學習處理器與所有普遍使用的框架連結:透過ONNX連結TensorFlow、TensorFlow Lite、PyTorch、Caffe,以及其它框架;

2.在機器學習處理器與Arm平台上,支援越來越多的運算子(Operator);

3.透過整合的圖形最佳化與運算子融合,驅動高效率的執行(圖3)。

圖3 Arm類神經網路軟體框架

圖3 Arm類神經網路軟體框架

神經編譯

神經編譯可讓更多的數據儲存在晶片上,並在融合層之間再度使用,如此可避免存取DRAM,並大幅降低功耗。Arm的壓縮技術同時也為DRAM節省1.5到3倍的外部記憶體頻寬。與其它的NPU相比,運行Winograd效率較高的卷積加速共用過濾器,其速度高出225%,並可在更小的面積上促成更高的效能。

編譯器會取用完整的網路圖形、自動將工作分塊並排到16個運算引擎,並把64kB的靜態隨機存取記憶體(SRAM)切片裝配到每個運算引擎,這相當於為整個處理器裝配完整的1MB的SRAM。它同時使用確定性與靜態排程來簡化作業並提高效率、讓開發全新神經功能較不費力、隱藏複雜的記憶體轉移,並進一步提升電池的續航力。

接下來,編譯器會檢視神經網路,並把它映射到指令流;這個指令流則是為了供機器學習處理器內的元件使用而特別設計的。這個指令流隨後針對高效率的直接記憶體存取(DMA),以及高階控制任務與執行卷積的運算引擎之間更簡單的流程控制,進行任務的排程(圖4)。結果是,最佳化工作負載可以更高利用率運行,達到更快速且更有效率地執行,並且提升核心的整體回應性。

圖4 由Arm NN驅動的高效運作程序

圖4 由Arm NN驅動的高效運作程序

因記憶體存取是可預測的,因此不需要複雜的記憶體快取階層來支援排程。給予每一個運算引擎專屬的SRAM,也讓記憶體的作業更靠近運算作業,達成更快速的處理。結果是更具效率、且更可預測的硬體效能,用來定義相依性與明訂處理順序也更有彈性。這種針對零值的閘控技術,可協助讓卷積層的功耗降低最多達50%。

卷積實現高效率

共用的神經網路包含70%~90%的卷積。這些卷積作業的核心,是相當耗時的乘積累加運算(MAC)。架構越深化,就需要更多的MAC,處理每個工作負載也會花費更多時間;這點以邊緣裝置來說,會使用戶產生挫折感。

為了緩和這種情況,負責執行大多數卷積運算的機器學習處理器的MAC引擎,設計上注重效率的提升,並有能力在每個週期執行八個16×16的8位元點積(DP)運算。換句話說,MAC引擎中每個寬度16的DP單元,可以與32位元的累加器一起執行8位元、深度16的DP運算。這相當於每週期256次運算;如果拿它乘以16個運算引擎,結果等於每週期4,096次運算,最後在1GHz時脈達成每秒4TOP的運算率。

處理器同時用上多種技術,讓卷積的速度更快,且效率更高:

.分享特徵圖

如同圖5顯示,輸入數據或啟動透過放送網路進行讀取與分享,並減少冗餘、高耗能的記憶體讀取次數。每個引擎會收到相同的啟動指令,並把它與獨特的權重結合;權重則在每個引擎都不盡相同。權重會在本地進行壓縮或解壓縮,以便把執行每一部分運算所需的距離與能源消耗降到最低。這些運算的結果就是多個輸出特徵圖(OFM);當每個運算子運算結束時,OFM就會被推送到外部記憶體。

圖5 ML處理器中的卷積層運算

圖5 ML處理器中的卷積層運算

.運算子融合

多個運算作業也會智慧地融合在一起。這些運算可能是來自MAC引擎或可編程層引擎(PLE)引擎的順序運算,或是來自兩者的順序運算。當融合發生時,產出的OFM會在本地儲存,並作為下一個運算子的啟動被再度使用。如此利用時序的局部性可以減少DRAM記憶體異動的次數,進一步降低能源的消耗。

.零值的功耗閘控

為了避免把運算浪費在最終會被截斷成零的運算作業上,數據路徑運用特殊技術預測零值的啟動,並關閉部分相關的邏輯與硬體。這種針對零值的閘控技術,最高可以協助卷積層降低50%的功率消耗。

.Winograd

MAC引擎同時也包含Winograd卷積的硬體加速,同時需要轉型。Winograd與其它的NPU相比,共用濾波器的加速速度快上225%,在使用3×3卷積過濾器的網路上可以達成更高效能的執行,例如Inception v1-v4、Resnet-v1、Resnet-v2、VGG以及YOLOv2。

降低頻寬

機器學習處理器不但能帶來高效率的效能,同時也可最小化記憶體頻寬。一開始設計時就考量到記憶體,對於完整的系統整合與確保一致的數據流,極為關鍵。為了達成這點,本文使用多重的最佳化技術,例如無損壓縮(端對端的橫跨整個處理器)、叢集、修剪以及工作負載並排。

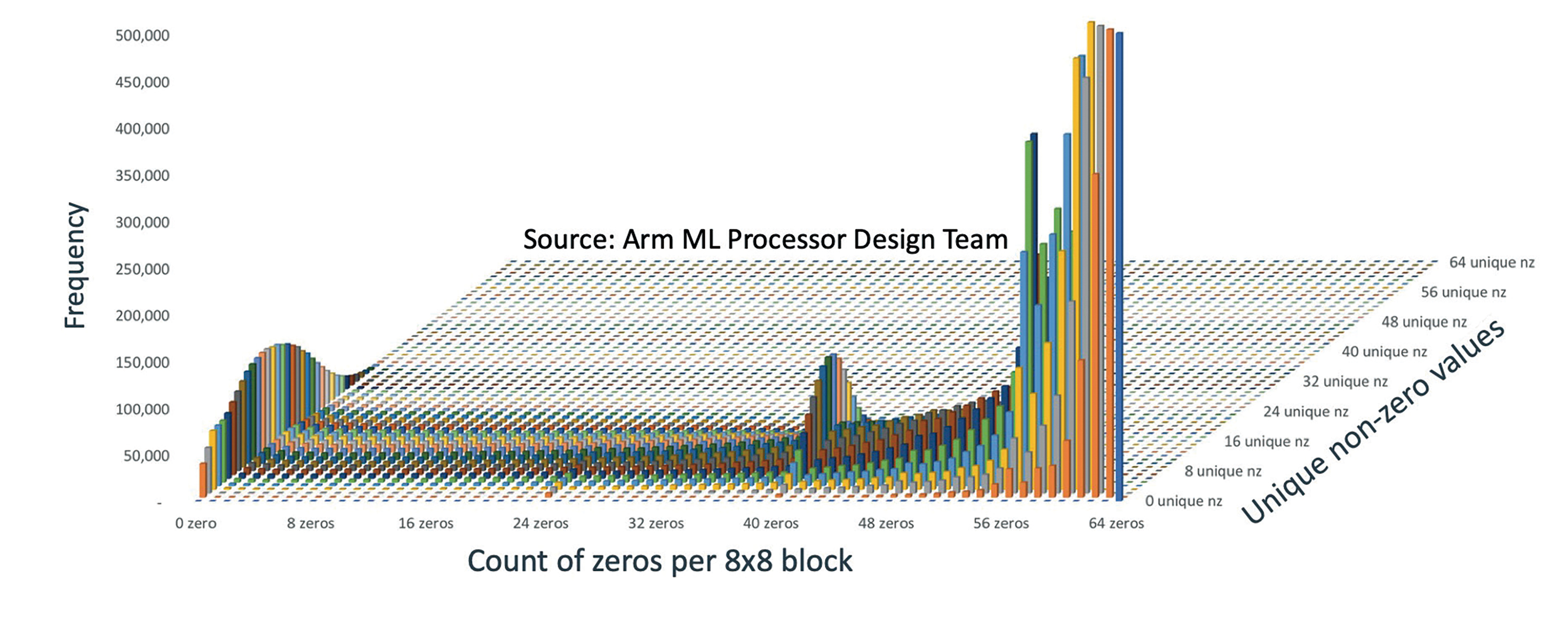

.無耗損壓縮

機器學習處理器同時使用無耗損壓縮,來縮小權重與啟動的大小,並為DRAM作業節省大量的能源(或頻寬),同時進一步提升效率,同時也會使用壓縮來管理零值與非零值,與未使用壓縮技術的架構相比,整體頻寬最多可以降低近三倍(圖6)。

圖6 常見神經網路中運算數值分布概覽

圖6 常見神經網路中運算數值分布概覽

.端到端的壓縮

模型從內部SRAM被讀取之前,機器學習處理器在整個工具鏈可以對模型進行壓縮,為往往權重使用較多頻寬的網路較後層級提升效率。如此一來就可以提升效能,特別是當較多數量卷積層的深度卷積神經網路(CNN)一起作業時。

.叢集與修剪

處理器同時提供叢集與修剪的硬體支援。叢集是一種模型部署的技術,可以識別與「叢集」類似的輸入型態與群組,或是把剩餘的非零權重「折斷」成可能為非零值的較小集合,並讓它們更易於管理。修剪則把網路中的不需要的節點整個移除,以減少連接的數量與需要的計算。為了獲得叢集與修剪的好處,處理器在編譯階段會允許神經網路模型進行離線壓縮,而且當系統從每個引擎的本地記憶體進行讀取時,可以提供硬體支援。

.工作負載並排

編譯器架構的排程,可以進一步降低頻寬。排程藉由把工作集維持在SRAM內,可以更有效地使用記憶體頻寬。並排地使用,也就是在各個運算引擎套用或「並排」卷積作業,可以避免DRAM的存取。此外,也會使用同樣的輸入特徵圖與不同的權重,平行計算多個輸出特徵圖。中間的階段則透過管線安插在MAC引擎與PLE之間。這些功能都可以讓頻寬最小化,並讓機器學習處理器效率更高。

安全性

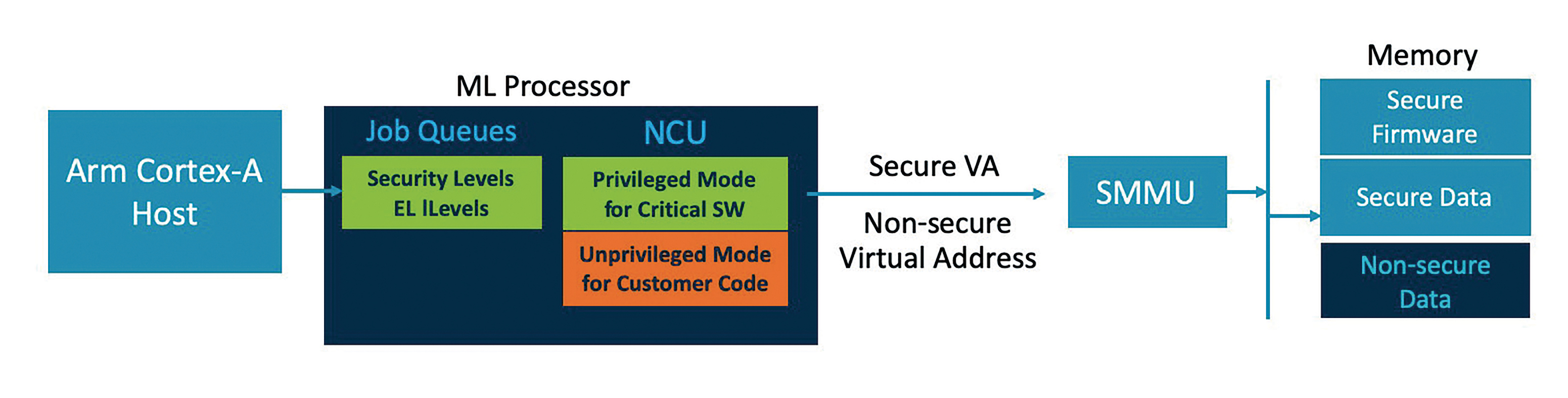

安全性是系統設計必要的一環。其中一個關鍵的概念就是縮小受攻擊面;在理想的情況下,受攻擊面會很小、很簡單,可供稽查。

為了因應此需求,機器學習處理器允許數個實作選項,以應對多個風險情況與各種使用場景,包括以下顯示的一些場景。它使用經業界實證的Arm微控制器技術,具備標準的特權層級與確定可以用在SRAM的韌體,讓稽查更簡便。

透過可配置的安全佇列,可以選用在可信任或安全執行環境(TEE或SEE)中,支援處理必要的系統記憶體管理單元(SMMU),對系統進行配置,並針對可能正在處理高價值媒體串流內容的多個使用者提供支援(圖7)。

圖7 ML處理器安全和彈性的操作模式

圖7 ML處理器安全和彈性的操作模式

Arm對於安全採取的端對端方法,為處理器、次系統、加速與卸載,提供遍及整個系統的分層保護。Arm的平台安全架構(PSA)是針對共用安全最佳實務的框架。Arm與安全性相關的產品選項,協助合作夥伴們防範各種攻擊,進而部署適合其應用需求的安全層級。

未來仍可適用

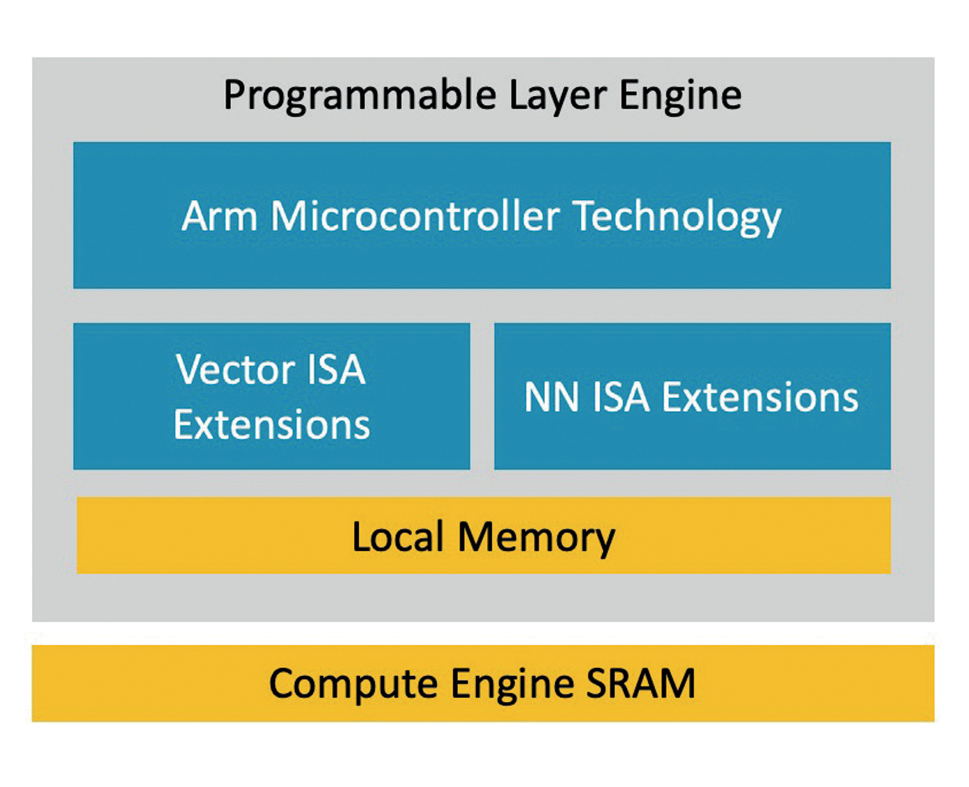

機器學習正持續演進中,因此設計工作要能跟上進化時程相當重要,才能持續以最佳的情況運作。為了應對這一點,PLE在硬體完成設計後,可讓軟體開發出新的運算子。這些新的運算子可包含在未來的韌體更新內,於設計定案或裝置出貨後,實現功能的更新。

PLE可精細化與強化MAC引擎產出的結果,提供剛出現的全新技術的實作方式,即便是與卷積作業無關的新技術。它包含針對不同指令集架構(ISA)加入強化附加功能的Arm微控制器技術,包括向量與神經網路擴充技術。這些擴充技術往往瞄準非卷積作業,例如池化、ReLu與Transcendental。

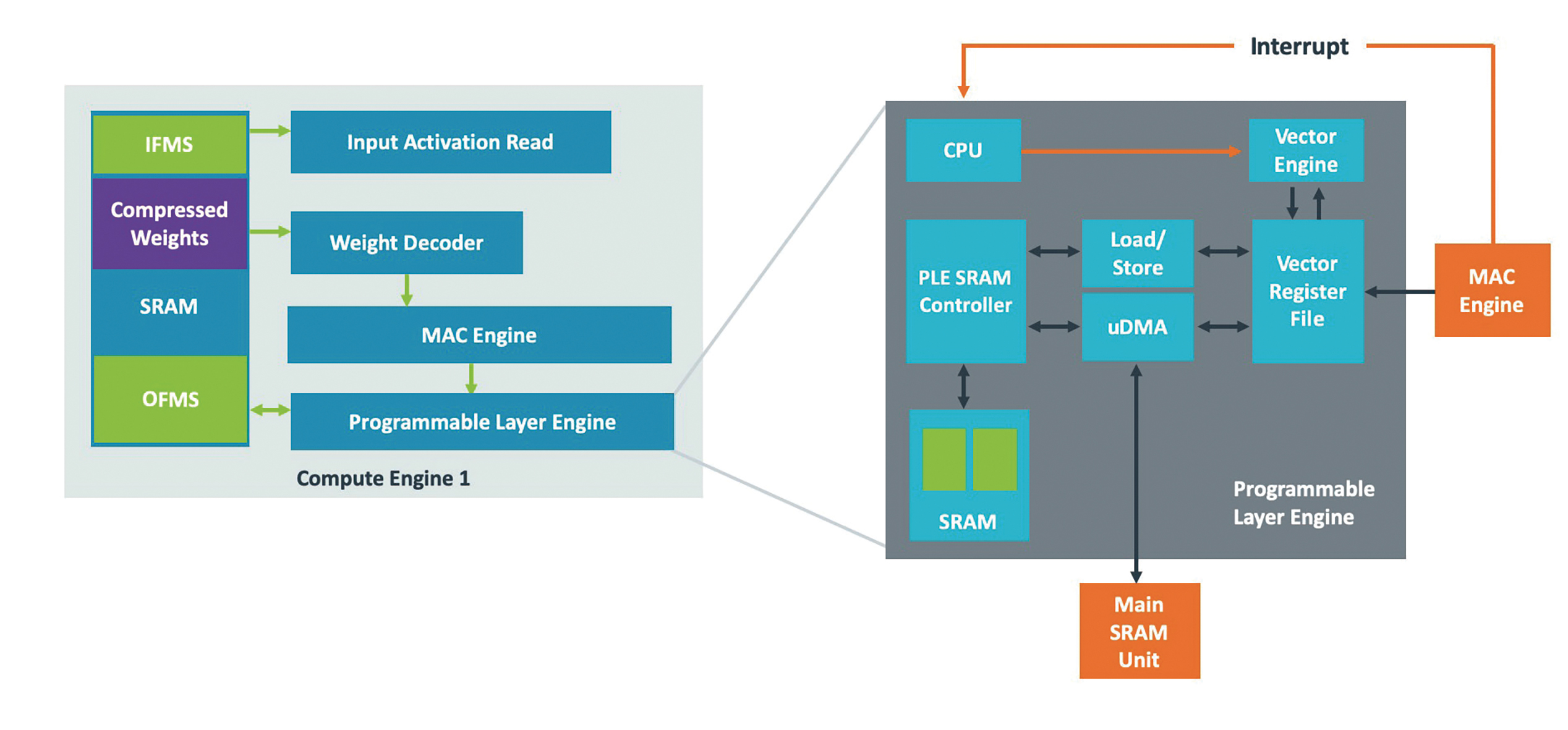

如圖8顯示,PLE會接收來自MAC引擎的運算結果,並把它填入PLE的暫存器檔案。系統隨後會送出中斷訊號來啟動PLE處理。由於作業目的通常是池化或降低,它們多數由寬度128位元、16通道的向量引擎來執行。結果會被送回到PLE的SRAM,然後由Micro-DMA單元把它寫成每個運算引擎中,主SRAM的輸出特徵圖(OFM)。這些PLE結果隨後會再拉回運算引擎中進行處理(圖9)。

圖8 ML處理器中的可編程層引擎(PLE)

圖8 ML處理器中的可編程層引擎(PLE)

圖9 PLE運作程序

圖9 PLE運作程序

無縫整合 跨界支援

機器學習處理器是廣泛的機器學習平台的一環,強調的是可互通性與方便性,設計用意在於能在各種Arm的產品上穩定運作,包括編譯器、驅動程式與函式庫,以及可以降低複雜度、支援可擴充性,並讓開發更輕鬆省力的框架。

這個獲得多元且蓬勃發展生態系支援的寬廣平台,正透過設計上的彈性、最佳化的效能與更快的產品上市時程,驅動次世代的智慧裝置。

(本文作者為Arm資深軟體工程師)