對於高速數位訊號處理器(DSP)密集型系統的設計,降低功耗變得越來越重要,例如在通訊系統中,通訊必須以週期猝發(Burst)方式來實施,以避免放大器和系統其餘部分的電路一直消耗功率。

感測器網路的要求是定期關斷工作中的感測器(例如用於交通影像或天氣感測器),或者定期打開它們(例如在地震情況下),以及在設備回到睡眠模式前以猝發的方式將資訊上傳。對於具有相對較低取樣頻率的醫療監測設備,以及可攜式解決方案,低功耗是不可或缺的特性,而實施週期性的操作則是將功耗降到最低的方法。

特殊電源模式加持 FPGA挑戰最低靜態功率

對於注重降低功率的DSP密集型系統設計,設計人員不僅要提供最低的靜態功率,更重要的是讓總體功耗愈低愈好,尤其在高頻率和高溫條件下,而現場可編程閘陣列(FPGA)能以一種綜合設計方法實現功耗最小化的目標。

此種方法包括製程技術、架構和邏輯配置,以及SERDES、DDR2/3和DSP模組的嵌入式特性,同時還加進一種特殊的電源模式,此一模式可將功耗降到比靜態功耗還要低的等級。

在過去20年裡,許多先進的中央處理器(CPU)和微控制器(MCU)都已開發出各種節能模式,以應對DSP密集型設計中更高頻率、更高整合度帶來的功耗挑戰。但是只有先進的FPGA能提供類似的低功耗能力,並且支援更高頻率的元件;此外,最近也出現了一些FPGA元件可用來解決早期建基於SRAM解決方案的洩漏問題,同時備有低功耗模式以提供額外節能能力。

一般而言,靜態功率、動態功率及浪湧功率這三種功率成分左右了與FPGA功率預算相關的總體功耗;為了實現最低功耗,必須對這三種功率進行有效管理。

要管理這些功率成分,需要固有的低洩漏電流;如果要讓FPGA元件支援DSP密集設計的功率需求,這便是一項重要的特性。與使用SRAM單元的FPGA元件相比,建基於快閃記憶體技術的FPGA解決方案,以單一(而非六個)電晶體來構建,而且配置功率和浪湧功率(上電期間)均為零,擁有相當優勢。

SRAM FPGA在一種未配置狀態下上電,須完成初始上電及重定順序。首先,許多配置位元處於未知狀態,必須在每個電源週期初始化,因此會帶來浪湧電流,可能會產生高至數安培或長至數百微秒的尖峰,進而引致浪湧功率。

為減緩此一尖峰電流,許多SRAM FPGA元件都會為系統增加複雜的上電順序要求,而建基於快閃記憶體的非揮發性FPGA則不需要外部的配置元件重新進行程式設計,在啟動階段就可省去數百微瓦(mW),且也省去用於減緩尖峰電流的外部元件(圖1)。

|

| 圖1 使用建基於快閃記憶體的FPGA元件,可以在元件啟動和配置階段省去數百微瓦(mW)功率。為避免大電流峰值,SRAM FPGA需要複雜的上電排序,因此增加了元件成本和占位面積。 |

在某些情況下,與建基於SRAM的解決方案相比,建基於快閃記憶體的FPGA可以把每單元洩漏電流降低一千倍,並且具有超低靜態電流和免去外部元件兩種優勢。

建基於快閃記憶體的FPGA除了天生功率較低外,還可以利用額外的特性以進一步降低功率。現今建基於快閃記憶體的FPGA元件將硬IP模組和FPGA架構結合在單一裸晶(Die)上,並且將此一FPGA與功能齊全的微控制器系統、增強的FPGA架構、高速串列和記憶體介面整合在一起。

額外的功率敏感特性和其他特性包括:

增強的SERDES功能

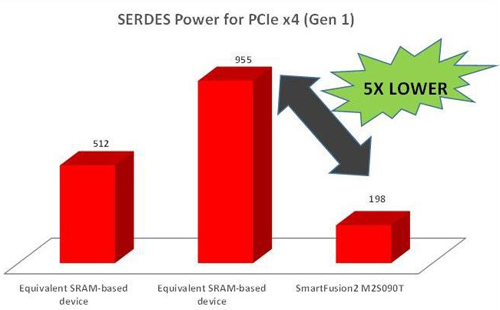

最新款的FPGA將每一SERDES通道的每Gbit/s功率降低至13毫瓦,比功能相似的其它FPGA解決方案降低多達五倍(圖2)。

|

| 圖2 主要FPGA製造商的SERDES功耗值 |

在較小的元件中整合許多不同的硬IP和其他資源:藉由加入更多I/O、收發器、PCI Express端點和高性能記憶體子系統,就可以讓體積更小、功率更低的元件提供更多功能。

嵌入式RAM和數學模組

建基於快閃記憶體的FPGA元件內建針對密集型DSP應用的硬RAM模組和數學模組,這些模組在低功率下提供高水準性能。圖3為不同FPGA製造商的RAM功率比較。

|

| 圖3 主要FPGA製造商的記憶體和數學模組功耗值 |

固有低功率的嵌入式處理器子系統

某些子系統提供多種低功率模式,包括睡眠模式和深度睡眠模式。使用低功率模式可以實現FPGA架構和相關I/O的快速停止和啟動,同時保存FPGA架構的狀態,並且大幅地降低功耗。

元件大約花100毫秒(ms)來進入睡眠模式,再花大約100毫秒退出這個模式;然而,FPGA退出睡眠模式的狀態可以被保存下來,以便從該狀態繼續運作。

使用附加工具來將功率減到最小

使用者可以憑藉各種工具來計算功率配置,以及實現智慧式平面配置規畫(Floor-planning)和功率優化布局布線,從而進一步優化其設計以降低功耗。

所有這些降低功率的特性和功能,在高速DSP密集型系統設計中都十分重要。

記憶體頻寬需求大 濾波器設計至關重要

DSP密集型系統設計需要複雜的數學運算和高記憶體頻寬要求,以及具有動態重新配置功能的高速序列傳輸,為了在高性能水準的情況下滿足這些要求,會消耗掉很大的功率。

新一代FPGA元件不但要能處理這些需求,且功耗要越低越好,同時還不可以犧牲性能。DSP系統設計人員在設計中會用到多個不同構件(乘法器、記憶體、收發器等),而不同系統架構實施方案的功耗會有顯著差別,這取決於所使用的FPGA元件。

所有FPGA元件都會把硬乘法器當作基礎運算單元,這個硬乘法器在總體系統功率預算方面具有舉足輕重的分量。為此,美高森美深入研究了不同架構的有限脈衝回應(FIR)濾波器,並且根據乘法器數目與運作頻率的對比關係,來對各個元件進行功耗分析。

FIR濾波器是一個DSP模組,經常在各種應用中用於消除不必要的雜訊,同時提升訊號品質,或者形成訊號頻譜;其擁有數種架構,包括轉置或收縮(有或沒有對稱性)。這兩種架構均具有與總體初始延遲、DSP模組數目、輸送量或性能,以及管線暫存器數目相關的特性。

兩種架構之間的區別如圖4所示,圖中顯示16接頭FIR轉置和收縮的對稱版本。

|

| 圖4 對稱轉置和收縮16接頭FIR的架構比較 |

收縮架構使用管線級並且減少輸入扇出以提高運作頻率;同時,N接頭收縮FIR的初始延遲是(2*N-2)週期。相較之下,雖然轉置架構的運作頻率較低,但其初始延遲較好(N-1週期),而且使用較少的順序(Sequential)資源。比較這些架構時,還要考慮其他的因素,其中一個最重要的因素是濾波器的穩定性,尤其是必須考慮大量分接頭(Tap)數目和加權特性。

例如,在需要回音消除(Echo Cancellation)的語音處理應用中,於存在大部分回音的近端,權重必須較高;在回音較少的後續濾波器分接頭上則要較低。

根據使用的架構不同,FPGA的功耗可能會有很大差別。在一項使用功耗預估工具的研究中,以FPGA開發工具套件在32、64和128接頭轉置FIR實施方案中測量不同溫度下的實際矽元件,結果顯示設計和實施恰當的FPGA元件可提供顯著的節能特性,在較低頻率和高溫下甚至會更加顯著(圖5)。

|

| 圖5 不同FPGA供應商的32、64、128接頭FIR之總體功耗值 |

另一項重要的發現是,最佳性能FPGA元件的功耗與分接頭數目成線性關係。換句話說,如果分接頭的數目少,某些性能較差FPGA的功耗值會更差;對於其他元件,在分接頭數目高時,它們的性能更差。

現階段,以DSP為中心的系統設計在減小功耗方面正面臨不斷增加的壓力。基於快閃記憶體技術的FPGA不只是減少靜態功耗,而是減少總體功耗,所以正是實現下一代高速DSP密集型系統設計的重要因素,這些設計要求必須在不斷縮小的外形尺寸中提供卓越的演算法性能,並且功耗也要盡可能低。

(作者皆任職於美高森美)