封裝天線(Antenna-in-Package, AiP)技術,是將一個或多個天線與前端射頻電路整合成一個完整的收發器模組。

此技術已廣泛應用於60GHz手勢感測器、77GHz汽車雷達、94GHz相控陣列天線,甚至是122GHz毫米波成像雷達,以及300GHz的無線傳輸。5G毫米波頻段具備充足的頻寬,是創造更佳用戶體驗及產業應用發展的下一代通訊基礎。

封裝天線於未來通訊扮要角

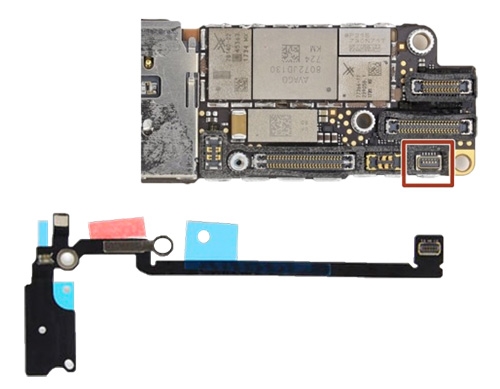

相較於毫米波為新領域,Sub-6GHz射頻技術已發展數十年。傳輸路徑損耗在該頻段從來不是主要的問題。以iPhone 8 Plus為例,其Wi-Fi及LTE的天線模組,仍然能利用軟排纜線以及連接器去連接主板,這種設計給予智慧型手機設計者安排模組位置的自由,同時也使得維修變得直接且簡單(圖1)。 然而,使用毫米波作為載波,工程師就得面臨訊號損耗高的物理現實。透過纜線以及連接器的傳輸結構遂成為過去式。降低路徑損耗的解決方案是將高頻損耗較大的接頭移除,讓天線盡量接近放大器(Amplifier)及其他電路系統。因此整合天線到SiP模組成為實踐毫米波前端射頻模組的較佳作法,這就是封裝天線技術即將在5G及未來通訊扮演重要角色的原因。

圖1 iPhone 8 Plus連接器設計降低維修難度

圖1 iPhone 8 Plus連接器設計降低維修難度

毫米波的前端射頻模組(FEM)需求不斷成長,AiP不但是較可靠的實踐技術,更讓陣列天線具有尺寸及成本上的優勢。但此技術的挑戰及門檻也相對較高,需考量多重工程因素,例如材料及製程的選定,會影響設計的權衡取捨。其他諸如熱管理、晶片控制設計、RF性能、校準等等多維工程問題。這些都需要大量的毫米波設計經驗和能力才能開發出好的產品。除了設計外,量產是更大的挑戰,特別是提升Over-the-Air(OTA)測試速度,以及降低測試設備成本,將會是主要的考量因素。

簡而言之,AiP是5G毫米波,甚至是6G低軌道衛星(Low Earth Orbit, LEO)較佳的解決方案。在本文中,將介紹相關業者如稜研(TMYTEK)的AiP技術能力,以及能為5G毫米波產業作出的貢獻。首先將介紹設計的技術能力;其次,將闡述AiP的模組製程;再者,將會解說OTA量產測試解決方案。最後,則將分享成功案例來總結。

一個AiP產品的成功關鍵取決於許多細節。在設計階段,應確保設計能符合選定的製造技術所要求的設計規則(Design Rule)。在生產過程中,如何快速且準確地評估模組的性能,對成本和生產效率至關重要。本文的目的正是講述業者如TMYTEK為5G產業和毫米波應用帶來的價值。以下各節將更深入地討論每個主題。

模組設計能力至關重要

毫米波前端射頻模組的架構類似Sub-6GHz無線系統,包括天線、放大器,雙工器和切換開關。

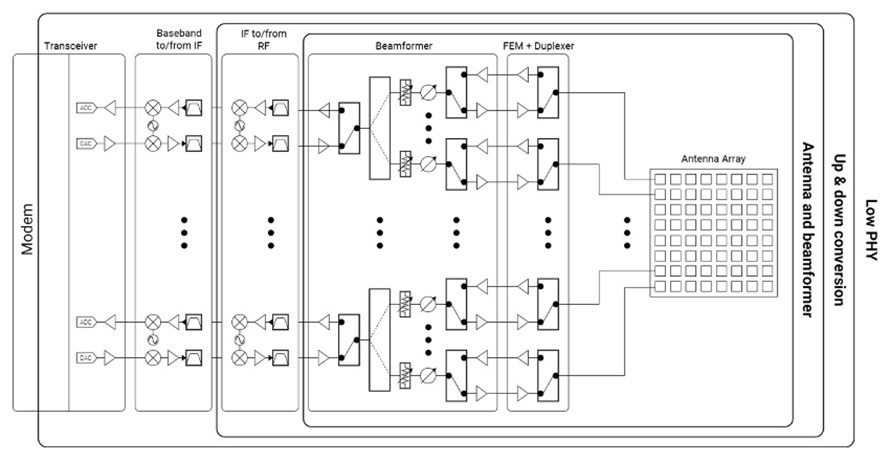

其主要差異在於毫米波前端模組是使用「陣列天線」及「波束成形電路(Beamformer)」。由於毫米波波長短、路徑損耗較大,因此需要透過陣列天線將訊號集中在一個方向,以利提升傳輸的距離。雖然解決了路徑損耗的問題,卻讓覆蓋率因此而降低。為了解決覆蓋率的問題,「波束成形」技術被採用來克服此缺陷。波束成形電路正是用以控制陣列中每個天線傳輸的相位和振幅,以實現波束掃描功能。圖2包含5G陣列天線的三種架構。最內層的架構一,是具備類比波束成形功能的前端射頻模組,包括天線陣列、雙工器和波束成形電路。其中雙工器與波束成形電路都已經被整合到5G毫米波波束成形晶片中,此架構用以實現射頻強波器(Repeater)的其中一個解決方案。

圖2 FEM架構

圖2 FEM架構

架構二,則為整合IF-RF轉換上下變頻(Up & Down Conversion)到系統中。由於變頻器會大大影響通訊的品質,將其嵌入系統中則能夠降低損耗以及減少系統整合時可能造成的其他問題。

然而,整合混頻器(Mixer)和濾波器(Filter)到封裝中是極具挑戰的工作。除此之外,在多模組拼貼式的大型陣列中,本地振盪器(LO)訊號分配也是另一個設計難題。

架構三,則是根據Open-RAN(ORAN)的規格採用Split 7.2選項,將Low PHY層以及數位、類比轉換電路整合到模組中,以卸載無線接取網路(Radio Access Network, RAN)中的前傳網路(Front-haul)的系統負載。後續的篇幅會簡要介紹ORAN。在這層架構中,因含有類比數位轉換及基頻訊號處理,挑戰會更加艱鉅。

目前市面上的波束成形晶片整合了功率放大器(PA)、低噪放大器(LNA)、移相器(Phase Shifter)、可調式衰減器(Variable Attenuator),以及Tx/Rx切換器(TR Switch)。CMOS、CMOS SOI,以及BiCMOS,雖然輸出的功率不像GaAs及GaN等III-V化合物半導體來得優越,但CMOS、CMOS SOI,以及BiCMOS具有整合數位電路的優勢,因此仍是優先被採用的製程。如TMYTEK評估且使用過市面上所有的波束成形晶片,清楚知道如何選擇合適的晶片來滿足客戶在不同產品以及場景所需的規格。在多維工程考量中,晶片扮演重要角色,除考慮輸出功率外,還要注意PA的Back-off機制已滿足5G通訊中所使用正交頻分多工(OFDM)所需。這些都是影響AiP模組的EIRP值以及功率效率的因素(表1)。

傳統的平面化天線設計不足以因應AiP技術所需,封裝所採用的製程特性也是需要被考慮的因素。如TMYTEK團隊擁有十多項天線專利,具備超過二十年的天線及前端射頻系統設計經驗。該公司針對不同類型的天線進行廣泛的研究和建模,包括貼片(Patch)、偶極子(Dipole)及基片整合波導(SIW)天線。其中的關鍵考量包含天線的10dB頻寬、極化;指向類型如Broadside或Endfire、半功率波束寬度(Half Power Beam Width, HPBW);X和Y軸的掃描覆蓋角度、隔離度、反饋損耗,以及實作的可行性等。而AiP封裝天線的具體考慮因素,包括材料的介電常數、均勻性、以及厚度等。

降低路徑損耗是設計毫米波模組的最高指導原則之一,而AiP技術的優勢就是把系統高度集積化、縮小內部傳輸線尺寸,並降低損耗。無論採用封裝的IC或裸晶,能夠針對不同製程使用鎊線(Wire Bonding)或覆晶封裝(Flip-chip)等技術進行晶片封裝,便為其中關鍵之一。與離散天線相比,在AiP中,天線非常靠近射頻前端,在適當的阻抗匹配(Impedance-match)設計下,可以獲得較小的路徑損耗以提高傳輸效率,並同時降低收訊時的雜訊。

舉例而言,TMYTEK曾設計製造過16層PCB堆疊的AiP模組、以及26層堆疊的低溫共燒多層陶瓷(Low Temperature Cofiring Ceramic, LTCC)模組,皆取得良好的成果。

帶通濾波器(Band Pass Filter, BPF)的性能取決於元件尺寸。因此可提供給濾波器使用的面積越大,則越容易設計出Rejection Performance佳的元件。然而AiP高集積度的波束成形IC已占用許多面積,因此濾波器的設計仍考驗著設計人員的功力。此外,濾波器在高熱工作環境的穩定性及再現性也相當具有挑戰性。以微帶線結構而言,介電常數、正切損耗、厚度及蝕刻尺寸的公差,都應被謹慎地模擬及設計,才能在28/39GHz以及任何其他目標頻段獲得最佳性能。

多個AiP模組通常會安裝在母板上形成大型陣列,所以將濾波器設計在母板上是另一種可能的架構。濾波器設計時一般會盡量設計在靠近希望濾除的訊號,因此在母板上的濾波效能需要被妥善考量。另外,被動元件對工作環境溫度的穩定性也必須被仔細設計,濾波器性能在不同的工作溫度須保持一致。

由於需要將IC輸出的訊號均勻分配給每一個陣列天線的單元,因此好的功率分配網路也在系統中扮演重要的角色。在AiP模組中,功率分配網路設計並不容易。與跟濾波器不同,功率分配網路無法置放於模組外。阻抗匹配和功率/相位平衡度是衡量功率分配網路性能的重要指標。通常有兩種方法進行設計。第一種方法是以平面電路設計實現功率分配網路,然而這會增加面積以及訊號處理困難度。另一種方法則是採用立體結構,將功率分配網路直接設計在Beamformer IC下方,然而此方式的設計難度更高。為了取得最佳的EIRP,功率分配網路的設計相當重要。

OTA測試解既有暗室量測困境

AiP技術所製造出的毫米波模組已經將天線與主被動電路封裝在一起,因此接觸型測試(Conductive Testing)的方法已無法使用來測試模組特性。

當天線與前端射頻模組缺乏連接器與測試點時,唯一測試模組的方法僅剩OTA。

傳統上,需要一個體積龐大的暗室及一個或多個機械定位器,才能精準且正確地測量待測物(DUT)的輻射場型圖。時至今日,緊湊場(CATR)技術縮小了暗室的尺寸,但仍需要機械式定位器來取得DUT的輻射場型圖。數十年來,此套測試方法已成為研究和生產時的標準。然而,即將到來的5G和LEO時代,產線上需要測量的設備數量,將使這種舊技術不堪重負。

體積龐大的暗室或CATR,對於研發來說是絕佳的工具,但對於生產線而言過於緩慢且笨重。

現代最新的CATR技術已經可以在幾分鐘內量得場型,已比傳統方式快上許多。然而產線需要更快的速度以因應未來幾年內要生產製造的數億到數十億個毫米波模組、智慧型手機,以及基地台等裝置。因此把測量時間縮短到「秒」級乃時勢所趨。除了速度,是否容易與產線自動化整合是另一個重要考量。而傳統方法所需的機械式定位器,較不利於實現產品線自動化。

有產線OTA量測方案針對5G毫米波AiP模組或裝置製造商打造,如XBeam。它採用全新的方法來滿足產線上的測試需求。為了加速OTA量測,從設計上捨棄了機械定位器,取而代之的是基於TMYTEK BBox技術的延伸以量測毫米波模組或裝置的RF性能,包括EVM、功率、相位以及其他射頻參數。另外,並開發OTACali技術:以OTA方式幫助客戶快速且準確地校準陣列天線。

低溫陶瓷共燒陣列天線展現波束成形能力

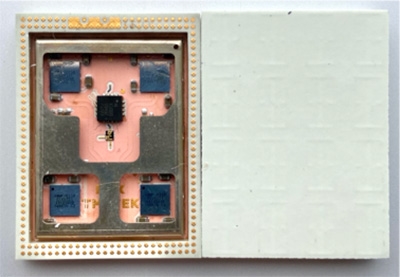

如TMYTEK與日本排名前三的LTCC技術公司NTK合作,並開發出4×4 LTCC AiP模組,頻段為5G FR2 n261(27.5~28.35GHz)。不僅如此,更透過在母板上並排四個模組來完成更大的陣列(8×8),並高度整合多種技術。

x5G毫米波射頻前端的天線陣列尺寸會根據不同的應用而各自迥異:2×4、4×4、16×16甚至更大的陣列都有可能。因此模組化設計遂成為一種更好的實現方式:利用並排單元模組來配置所需的相控陣系統。

以下將介紹一個4×4 LTCC封裝天線前端模組(AiP FEM),以及一個28GHz 8×8相控陣系統,它同時結合四個4×4 AiP FEM、功率分配器和鎖相振盪器(PLO)。最後,在星座圖和EVM結果中展示了波束成形能力及結果。

單元AiP FEM模組整合4個四通道Beamformer晶片、功率分配網路、Up/Down Converter、Frequency Doubler及16個SIW天線。電路及疊構由TMYTEK設計、軟硬整合以及測試;LTCC製造夥伴則負責生產基板。主要輸入及輸出包含:發送與接收IF訊號、本地振盪器、數位控制訊號及DC電源。每個通道的相位和振幅可獨立控制,以實現波束掃描及成形功能。SPI控制介面則用於控制波束成形,SPI的最高時脈為50MHz。此AiP的尺寸為29.3×22.1×4.1mm。如圖3所示,模組背面採BGA引腳設計方便以SMT方式運用,並利於組成不同尺寸的相控陣列。

圖3 LTCC AiP

圖3 LTCC AiP

此8×8相控陣系統將四個單元AiP並排於一個母板上形成8×8陣列;本地振盪器並未嵌入於AiP中,而是置於母板上。系統照片如圖4所示,這裡特別指出,系統旁邊有兩具風扇以利於散熱,該風扇未在圖中顯示。

圖4 8×8陣列母板

圖4 8×8陣列母板

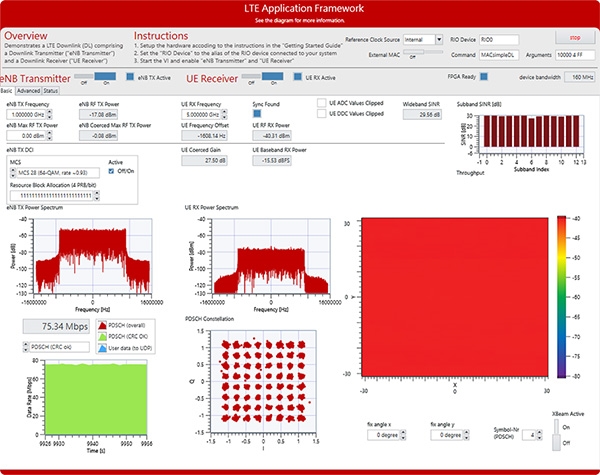

圖5顯示的結果,使用的是NI USRP系列產品作為基頻,並用不同解調變方式,取得不同的OTA測量結果。實驗結果顯示無論系統增益、SNR或Throughput均與預期高度吻合。

圖5 不同OTA測試結果

圖5 不同OTA測試結果

(本文作者為稜研科技共同創辦人暨副總經理)