多年來,晶片功能和資料傳輸量的要求不斷增加,推動晶片產業從較低資料傳輸率的並行連接進階到高速串列連接。串列器-解串列器(Serializer-Deserializer, SERDES)的主要功能即在高速差動對線上傳輸串列化的資料,而非在低速平行匯流排上傳輸。一個絕佳的例子就是傳統的三十二位元64MHz的PCI匯流排被單條PCI Express通道所取代,前者的資料傳輸量有2.112Gbit/s,而後者只用四根線卻能在2.5GHz運行,資料傳輸量可達4Gbit/s。簡單來說,SERDES協定使得資料傳輸的速率更高,而用到的接腳更少。

圖1顯示在一個現場可編程閘陣列(FPGA)實現的複雜系統中各種可能的SERDES介面,這個例子是一個以網路處理器作為系統核心的高性能板卡,SERDES的應用以黑色區塊標出;可以用FPGA實現的晶片則用白色顯示。

|

| 圖1 典型SERDES應用 |

SERDES依實現時脈方法分類

SERDES介面可以分為兩類:同步訊號源(Source Synchronous, SS)協定和時脈資料回復(Clock Data Recovery, CDR)協定,這兩個協定的根本不同就在於其各自實現時脈的方法。同步訊號源介面有一個單獨分離出來的時脈訊號伴隨著資料傳輸,而CDR則沒有單獨的時脈訊號,而是將時脈嵌入到資料交換中。也就是說,CDR接收器將對資料訊號本身進行鎖相來取得時脈,表1概括這兩者的一些基本區別。一般來說,CDR協定可以更快的速度運行,並傳輸更遠的距離,因此也面臨更大的設計挑戰。

| 表1 同步訊號源和時脈資料回復兩種SERDES介面 |

| 介面類型 |

I/O標準 |

時脈 |

典型應用 |

資料傳輸速率 |

例子 |

| 同步訊號源 |

LVDS |

分離 |

晶片至晶片(英吋) |

100M~1Gbit/s |

系統封包介面(SPI4.2)、相機鏈結視訊(7:1LVDS)、DDR記憶體、數位類比及類比數位轉換器的數位介面 |

| 時脈資料回復 |

LVDS、CML |

嵌入 |

晶片至晶片與至背板(英吋至英呎) |

600M~3.5Gbit/s |

PCI Express、高速乙太網介面(1GbE、SGMII)、Serial ATA、Serial Rapid I/O和SONET |

CDR透過資料訊號交換取得時脈

顧名思義,一個CDR接收器必須從資料訊號中回復被嵌入的時脈,更準確地說,時脈是在資料訊號的交換中得到的,CDR發送器先將要發送的資料串列化,然後將資料按8b/10b或類似的編碼方案進行編碼,這種編碼將八位元的資料轉換為十位元的字符。8b/10b編碼可以使得資料線路上傳輸的1和0一樣多,從而減少字符之間的干擾,即差動訊號向主導的邏輯位準漂移,並且提供足夠多的資料源,使接收器能對流入的資料鎖相。發送器會增加系統時脈來得到傳輸的位元率,然後以這個位元率,在TX的差動訊號對上發送那些編碼為8b/10b的資料。

CDR接收器的工作則先是要對RX差動位元流進行鎖相,然後將每次回復時脈中接收到的資料進行按位元對齊(Bit Align);接下來,資料會按照接收器的參考時脈來按字對齊。最後,將8b/10b的資料進行解碼,得到資料後供系統使用。

在CDR系統中,發送和接收的系統一般來說有著完全獨立的時脈,關鍵點在於這兩個時脈必須在一個指定的變異範圍內,這個臨界值一般在幾百PPM左右。

CDR收發器抖動問題待克服

CDR介面的主要設計難題就是抖動(Jitter),簡單來說,即實際資料和理想狀態下期望出現的訊號之間的位移。完全抖動(Total Jitter, TJ)是定量性抖動和隨機性抖動的組合,大部分的抖動都是定量性的,包括字元間干擾、串音、工作週期失真和週期性抖動等,例如交換式電源帶來的干擾。隨機性抖動是半導體熱效應的副產品,遠遠不如前者可預測。

發送參考時脈、發送鎖相迴路、串列器和高速輸出緩衝器都對發送抖動的產生有很大影響,發送抖動通常是以在一個位元時期內,或者資料眼(Data Eye)內,發生抖動的單位間隔(Unit Interval, UI)所占的比例來描述。例如,一個2UI的發送抖動就意味著抖動占位元週期的20%。對於發送抖動來說,較低的UI值更好,因為這意味著更少的抖動。

與上述類似,CDR接收器會指定一個它在某個位元率上能容忍抖動的最大數量,典型的位元誤碼率(BER)標準在1e-12,即每1e12個位元中能允許出現一個錯誤。接收抖動同樣也是以UI來表示,較大的UI意味著接收器能容忍更多的抖動,典型的接收器規格是8UI,意思是即使位元週期的80%是噪音,接收器仍能可靠地接收資料。抖動一般用統計鐘形分配來量化描述,這種分布在其頂端有著理想的訊號源配置。

分析眼圖 了解SERDES抖動情形

由於抖動是SERDES系統的主要挑戰,所以它也是量測上所關注的焦點。測量抖動時,一般用一台高性能示波器掛載在SERDES的訊號上,並觀測資料眼圖(Data Eye Diagram)或者只是眼圖。簡單來說,所謂眼圖就是指定差動訊號對其許多狀態轉換的重疊覆蓋,如果採樣視窗夠大,使得圖中的兩個鄰近的交叉點都被包括在其中,則生成的圖看起來像一隻大眼睛,這種圖顯示訊號品質和抖動的一種直觀視覺形象。一般來說,眼睛睜得越寬,訊號品質越好。

圖2顯示示波器上看到的一個典型的眼圖,在此圖中,V表示眼睛睜開的高度,而電壓的整體波動範圍(邏輯0到邏輯1)在1.2伏特之間。圖中有三個寬度(或是時間)的度量,包括UI量測完整的位元週期,H量測在共模電壓下眼睛睜開的最大寬度,以及T表示從最小與最大啟動電壓之間的寬度。H、T和V值增大,眼睛就會變寬,且會得到更好的訊號和更少的抖動。

|

| 圖2 數據眼圖 |

利用FPGA測量抖動數值

為了檢測傳輸抖動,位元誤碼率檢測器(BERT)會產生一個測試圖樣(Test Pattern),並把它發送到評估板的SERDES接收埠。與之類似,時脈產生器也被連接到評估板的SERDES時脈端。FPGA內部設定測試的通道折回(Loopback),所以接收到的測試圖樣被傳送到TX的管腳上,而示波器被連接到這個SERDES的TX連接器上,因此可以分析傳輸抖動的眼圖。所有的評估板SERDES連接,用的都是五十歐姆SMA連接。

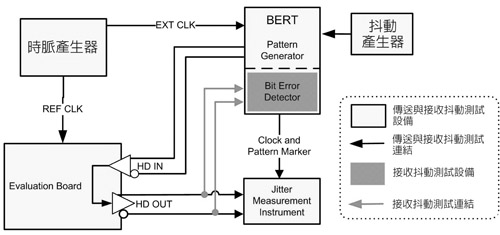

接收抖動的容錯性能測量,是透過先在FPGA的SERDES接收埠引發抖動,然後監控SERDES輸出端所產生的位元錯誤來實現。其設置如圖3所示,首先是將一個抖動產生器和一個BERT圖樣產生器連接在一起,然後BERT產生器將一個偽隨機模式序列(PRBS)發送到評估板的SERDES SMA輸入。這樣的配置可以使工程師能夠以一種可控的方式來向SERDES的RX埠引入抖動,FPGA被配置為折回,並且SERDES的TX埠與BERT的位元誤碼率偵測器埠相連接。這樣工程師就可以引入抖動,然後觀測FPGA產生的位元誤碼率,當BER值不在規格範圍之內時,工程師就知道抖動容限已經被超過,這個數值應該大於或者等於FPGA所指定的接收抖動容限。

|

| 圖3 抖動測試設備配置 |

測量高速背板性能

工程師要測量一個FPGA的背板SERDES連接傳輸特性,須要透過配置背板來驅動FPGA的TX訊號,然後再分析在背板輸出的眼圖來實現。首先用一個BERT圖樣產生器,把一個偽隨機模式序列(PRBS)位元流輸入到一個FPGA檢測板的RX SMA埠。在FPGA被設置為折回的情況下,這個PRBS位元流將會出現在檢測板的TX埠上,並且還會被驅動到同軸電纜中,這條同軸電纜將向背板提供訊號,例如Tyco XAUI Z-Pack HM-Zd。然後背板將這個位元流驅動到同軸電纜連接示波器的另外一段。系統需求所規定的測試參數包括PRBS模式選擇、背板和FPGA檢測板間的距離、同軸電纜的長度、預強調(Pre-emphasis)和等化器設置,操作溫度和VCC電源等。

圖4顯示九幅眼圖,這些圖都是在一顆FPGA上,透過使用以上的測試設置採樣而得到。各眼圖下的數字是測得的眼高,即圖2中的度量V。而隨著預強調的增加,在各個位元率下的眼圖也得到改善,預強調是SERDES傳輸器對線纜和背板中所出現訊號衰減的補償。這顆FPGA要求的眼高是85毫伏特,所以,只有運行在3.8Gbit/s下,且預強調為16%的那幅眼圖是不能滿足要求的樣本。

|

| 圖4 透過FPGA採樣所得眼圖 |

最後還有一點,那就是工程師在選擇FPGA時,必須考慮通道的配置靈活性、介面速度、SERDES的IP核心例如PCS、傳輸規格以及電氣需求等方面的要求。FPGA和SERDES介面的速度和市場表現都在不斷成長,藉由理解這兩者的長處和挑戰,設計團隊可以在縮短產品上市時間的同時,增加其產品的功能和可靠性。

(本文作者任職於萊迪思)