由於各個天線或感應器都各自需要訊號鏈,因此許多類比數位轉換器(Analog-to-Digital Converter, ADC)供應商將多個高速類比數位轉換器整合為單一的IC設計。這使得硬體設計人員能夠製作體積更小且功耗更低的多通道數位化元件。

不過,單一晶片整合多個ADC通道可能在通道之間產生串音(Crosstalk)現象。串音會使得ADC出現不相關的雜訊,使得訊噪比(SNR)降低,同時耦合(Coupler)訊號會產生類似諧波(Harmonic)的突波(Surge)雜訊,使得無雜訊動態範圍(Spurious-Free Dynamic Range, SFDR)及總諧波失真(Total Harmonic Distortion, THD)降低。

大多數的多通道ADC資料表都只提供一般單一串音的數值,而這個一般的測量數值通常是非使用中通道的測量數值,通道內完全沒有任何輸入電源,而且整個功率音調(Intonation)是注入相鄰的「干擾源」通道中。這雖然可說明多通道ADC的基本串音表現,但是並非系統的實際情形,在工作中會有可變訊號以不同的強度輸入於各個通道中。

首要工作—配妥實驗設定

為了在實驗室取得更接近實際應用的測量數值,須要將不同強度及頻率的兩個訊號注入多通道ADC,並且分析輸出中類似互調失真(Intermo- dulation Distortion, IMD)的雜訊、諧波及混合訊號。為了進行這項分析,於是針對ADS62P49這款由德州儀器新推出的14位元250MSPS雙通道ADC進行基準設定,並且搭配TSW1200EVM資料擷取卡,此擷取卡所含的圖形使用介面(GUI)能夠分析雜訊、諧波及IMD元件。

這項實驗使用三組訊號產生器(Signal Generator),第一組產生245.76MHz的時脈訊號,第二組產生輸入ADS62P49EVM通道A連接埠的170MHz輸入頻率(IF),第三組則產生輸入通道B的184.3MHz輸入頻率。各個訊號都會由窄頻LC濾波器進行濾波,以確保盡可能達到最確實的測量結果,而且ADS62P49EVM的設計將輸入電路與時脈電路之間的間隔加大,因此能夠將電路板的訊號耦合情形減至最低。

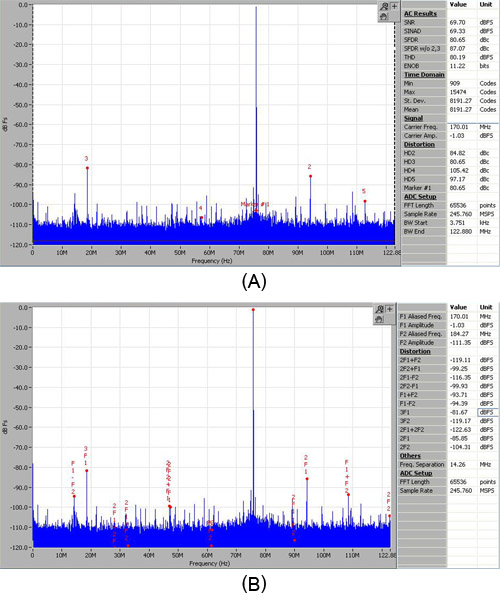

圖1顯示此次實驗的一般輸出頻譜。其中–1dB全刻度(Decibels Relative to Full Scale, dBFS)訊號是以170MHz輸入通道A,而–1dBFS訊號是以184.3MHz輸入通道B。通道A的分析結果分別顯示在兩張圖中,其中圖1A顯示單音分析,而圖1B顯示雙音分析。在此設定中,資料表所記載170MHz輸入頻率的71dBFS一般SNR略微降至69.7dBFS,而通道B未使用時,由此EVM擷取到的SNR值為70.08dBFS。從這些數值中可以看出,雙音分析中出現的主要串音元件是IMD2產品。由於F1+F2元件為92.71載波相對分貝(Decibel relative to carrier, dBc)而F1-F2元件為93.39dBc,因此IMD2高於通道A訊號的第四、第五及更高階諧波產品。其他較低能源的串音元件則是103.31dBc通道B訊號(2×F2)及98.25dBc(2×F2+F1)IMD3的第二階諧波產品。

|

| 圖1 A和B分別為以170MHz、-1dBFS訊號輸入的通道A和184.3MHz、-1dBFS訊號輸入通道B的單音及雙音調分析。 |

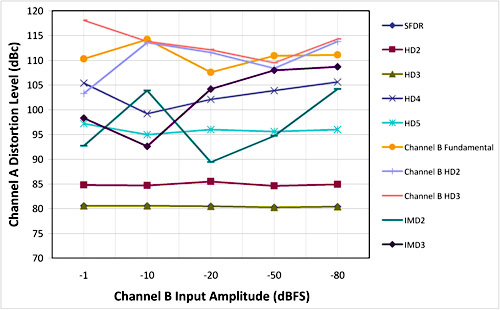

考量從通道B洩漏到通道A的電量以及通道A中將據以調節的電量,圖1顯示的數值可說是最不理想的狀況,而在實際情況中,大訊號振幅(Amplitude)會輸入通道中,而小訊號振幅會輸入干擾源通道中,反之亦然。圖2顯示170MHz、 –1dBFS輸入(HD2、HD3、HD4及HD5)的通道A中前五項諧波元件,其中通道B的輸入振幅介於–1dBFS至–80dBFS之間。圖中也顯示電量洩漏到通道A的通道B串音元件,其中包括通道B基本、第二階諧波、第三階諧波及互調產品IMD2與IMD3。

|

| 圖2 通道A在245.76MSPS的SFDR和串音元件,以170MHz、–1dBFS訊號輸入到通道A,並以不同振幅的184.3MHz訊號輸入通道B。 |

一如預期,HD3是通道A中最嚴重的突波,並且在所有情況中將SFDR設定為略高於80dBc,HD2則是次高的突波,大約為85dBc,而第三高的突波則會隨著通道B的振幅而變化。在較高輸入振幅的情況中,IMD2及IMD3會達到與通道A的HD4及HD5相同的高度。只有在較低輸入振幅的情況中,這些元件才會降低到通道A次高階諧波元件以下。

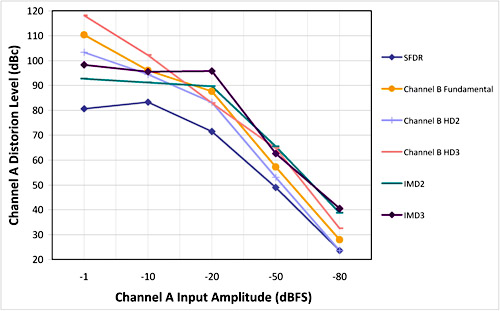

另外,必須注意完整功率訊號輸入干擾源通道時,讓目標通道的輸入減少所產生的影響。圖3顯示通道A的SFDR,其中出現184.3MHz、-1dBFS訊號輸入通道B的170MHz輸入頻率變化振幅訊號。此圖顯示,通道A出現高輸入振幅時,IMD產品便會是最嚴重的串音元件。然而,通道A的SFDR仍然由訊號輸入最低達到–50dBFS的訊號相關的諧波元件所決定。對於低於此程度的訊號而言,通道B的串音元件才會達到與通道A諧波元件相同的高度,特別是基本及第二階諧波元件。

在–80dBFS的情況中,最嚴重的串音元件會比輸入通道A的諧波元件高出15dB,值得注意的是,這些元件在此情況中會達到65,536點資料擷取的雜訊位準(Noise Floor)。另外,通道A的輸入振幅等於或低於–10dBFS以下時,如果通道B在非使用中或已插入–1dBFS訊號,則SNR幾乎相同。

串音免不了 但影響不大

圖2及圖3顯示,在大多數情況中,將訊號輸入目標通道的諧波產品會設定SFDR。當訊號出現在通道B時,雖然串音能源總是會輸入通道A中,但是一般不會高於通道A輸入訊號的第二階或第三階諧波元件。除了透過仔細的頻率規畫,使第二階或第三階諧波元件超出頻帶外的例子,串音並不會對於使用多通道高速ADC的系統造成任何限制。另外,對於ADS6225及ADS62P45的其他ADC也進行過類似的實驗,這些ADC雖然採用不同的核心架構,但是達到與本文所述相同的結果。

|

| 圖3 以變化振幅訊號進行的通道A單音及雙音調分析,其中通道A的輸入訊號為170MHz,通道B的輸入訊號為184.3MHz、-1dBFS。 |

不過,這項試驗只是為了證明ADC晶片中不可避免的串音不會對使用多通道高速ADC造成任何限制。不同訊號輸入ADS62P49之類ADC的各個通道時,必須特別注意ADC周圍的電路配置。訊號會在電路板耦合,造成與ADC內部常見突波相類似的突波,不過程度較更高。位於ADC輸入前端的低通(Low Pass)或疊頻消除濾波器(Anti-aliasing Filter)可限制其他元件產生的諧波耦合進入相鄰通道,但會使得目標訊號減弱。另一種會造成單通道及多通道ADC的效能降低的常見電路板訊號耦合是時脈訊號與輸入訊號混合,或者是電源供應的鏈波與輸入訊號耦合而產生IMD突波。

(本文作者任職於德州儀器)