AI技術不斷進步,如何確保高速訊號在AI應用設備中傳輸時,仍能保持穩定,且不受干擾,是許多工程師面臨的挑戰。本文將說明如何透過高速訊號傳輸相關測試,確保產品順利通過規格驗證。

在當今技術環境下,無論是AI伺服器、加速運算卡、交換器,還是AI邊緣運算設備如PC、遊戲主機、繪圖卡、機上盒、監視器及電視,所有這些設備都需要面對高速訊號傳輸的挑戰。從訊號的干擾排除到材料的選擇,每一個設計環節都可能影響最終產品的性能和市場表現。PCIe Gen 6、乙太網路400/800G等高速規格的普及,更使得產品測試與驗證成為設計過程中不可或缺的一環。市場上許多企業,尤其是涉及AI應用的開發者,迫切需要高效的測試方案來解決高速傳輸中的潛在問題,並確保產品能順利通過市場驗證。

AI應用下更高速的運算環境,除了對訊號傳輸的穩定性、除錯需求及散熱管理帶來新的挑戰,亦引發一系列的技術難題,從高速訊號中繼IC(Re-driver)做訊號補償/訊號重整的導入需求,到電路板材料的升級,甚至是傳輸線材與連接器規格的提升,產品設計與測試面皆面臨更多的困難與要求。

本文將討論高速傳輸的幾個測試面向,包括前端設計模擬評估、印刷電路板(PCB)特性分析、埠實體層(Port Physical Layer)測試驗證與客製化治具設計,並以iST宜特的測試項目和實際案例為範例,說明此類測試如何幫助產品因應高速訊號傳輸挑戰。

前端設計模擬與評估

在高速訊號傳輸產品中,訊號完整性(SI)和電源完整性(PI)模擬是確保產品競爭力的關鍵。隨著電子技術進步,特別是在AI高頻寬應用中,阻抗不匹配、結構設計不良或導孔(Via)排布不合理,容易引發訊號間干擾、串擾、失真及延遲,影響訊號品質。隨著運算速度和密度提高,高頻切換與大電流會導致電壓波動和雜訊,進而影響電源完整性及系統性能。因此,訊號完整性和電源完整性評估至關重要,可確保系統在高速運行下的穩定性。

以宜特的訊號完整性及電源完整性的模擬服務為例,業者只需要提供線路圖與Gerber相關檔案,透過Ansys & Cadence模擬軟體,即可在產品開發階段執行前端設計評估。在試產前期進行訊號模擬,將有助降低因設計缺陷所帶來的成本風險。

SI/PI相關測試

(1)S參數:反射損耗(Return loss)/插入損耗(Insertion Loss)/串擾(Crosstalk)

(2)時域反射(TDR)

(3)眼圖分析(Eye Diagram)

(1)直流電(DC)電壓降(IR-drop)分析:分析Power Net壓降,確保其不超過允許範圍,以避免系統異常。測試指標包括壓降分布、電流密度、直流電阻(Direct Current Resistance, DCR)和功率損耗。

(2)交流電(AC)配電網路(Power Delivery Network, PDN)分析:檢查設備端阻抗,確保維持低AC (Alternating Current,交流電) 阻抗。高阻抗可能導致IC運作異常和電源雜訊,影響系統穩定性。

案例分享

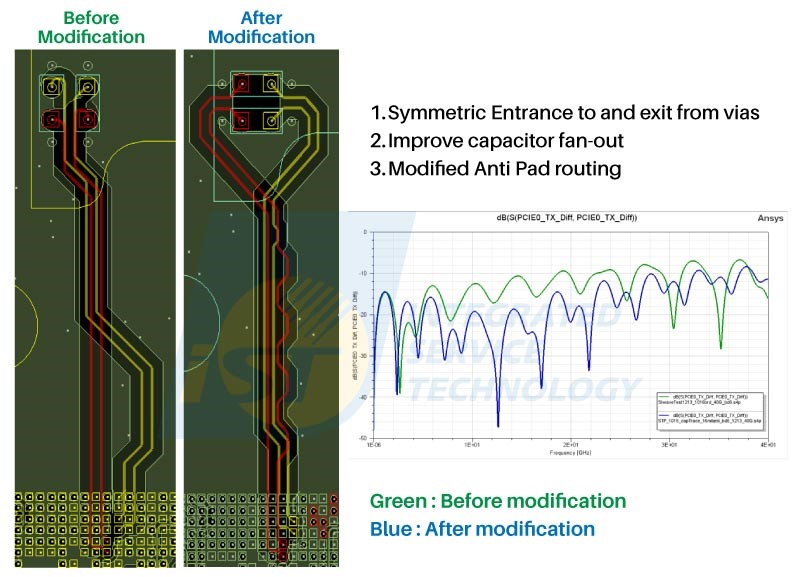

此案例在完成布局(Layout)設計後,進行了訊號完整性分析以確認訊號品質。模擬過程中發現,訊號在工作頻段(基頻8GHz)有較高的反射率,特別是在走線進出導孔處及電容附近存在改善空間。接著,針對這些區域進行了優化,將導孔走線對稱化,並改善電容下方的反焊墊走線(Anti Pad Routing),解決了電容過大導致的阻抗不連續問題。經過調整,基頻及倍頻的反射率顯著降低,確保了訊號完整性(圖1)。

圖1 優化前後訊號反射率(S11)結果比較 (圖片來源:宜特科技)

圖1 優化前後訊號反射率(S11)結果比較 (圖片來源:宜特科技)

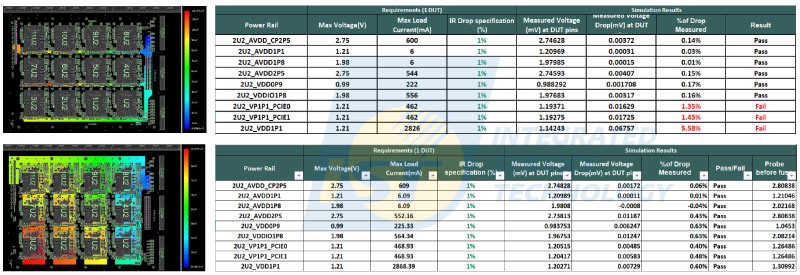

此案例在設計板子時,遇到了隨著傳遞距離增加而造成的電壓損耗過多的問題。透過Power DC模擬結果分析,觀察到Power Plane的壓降過高,進一步檢查後發現Power Plane過於破碎是主因。針對此問題,調整了Power Plane的完整度與分布,降低了整體壓降,並優化了Sense補償位置及方式,最終達到對各Site壓降差異的需求(圖2)。

圖2 修改調整Power Plane後,IR-drop結果皆為通過 (圖片來源:宜特科技)

圖2 修改調整Power Plane後,IR-drop結果皆為通過 (圖片來源:宜特科技)

PCB板材特性測試

在高速訊號傳輸的環境下,損耗越來越大,PCB使用的板材對訊號品質的影響變得更加重要。為了確保印刷電路板(PCB)的板材品質符合標準,不僅在設計階段需要進行評估,還需要透過實際測試來驗證其性能。

PCB/PCBA相關測試

(1)阻抗測量(Impedance Measurement):測試PCB材料的阻抗特性,確保訊號傳輸的穩定性。

(2)S參數測量(S-parameter Measurement):分析高速訊號的傳輸品質。

(3)Intel Delta-3.0/4.0測試(Intel Delta-3.0/4.0):在正常溫度及變化溫度下(Temp. Normal/Variation),驗證PCB在不同溫度條件下的性能表現。

(4)板階除錯測試(Board Level Debug):進行端到端通道損耗測試(End-to-End Channel Loss),找出並修正電路板訊號傳輸中的問題。

案例分享

在此案例中,當訊號驗證結果未能符合協會規範時,建議針對PCB進行時域反射及S參數測試,以確保PCB的設計阻抗和生產過程符合設計要求(圖3)。

圖3 使用網路分析儀進行PCB板內測試,包括阻抗(TDR)測試結果、插入損耗(IL)及反射損耗(RL) (圖片來源:宜特科技)

圖3 使用網路分析儀進行PCB板內測試,包括阻抗(TDR)測試結果、插入損耗(IL)及反射損耗(RL) (圖片來源:宜特科技)

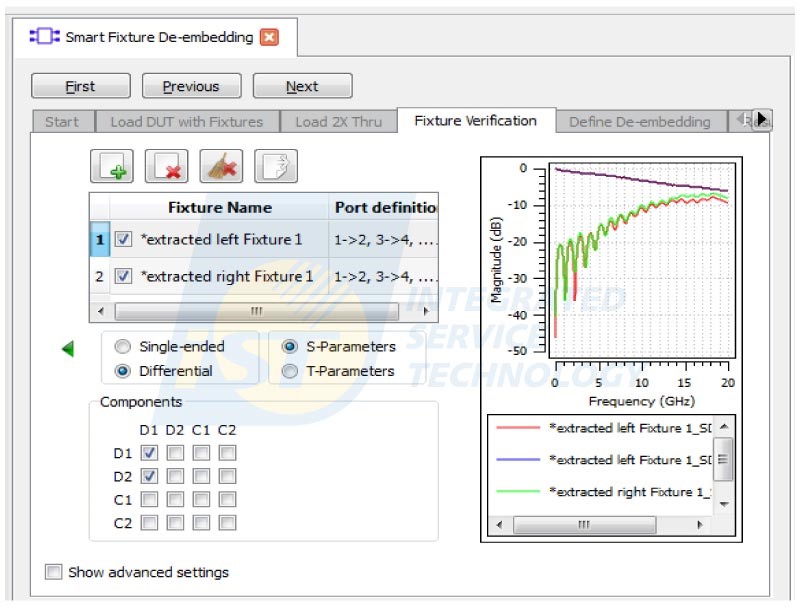

在測試PCB特性時,探棒或治具會增加額外的損耗。為了消除這些影響,可使用軟體進行去嵌化處理(De-embedding),以獲取更準確的測試結果(圖4)。

圖4 透過軟體後處理方式,去除探棒或治具對測試結果的影響 (圖片來源:宜特科技)

圖4 透過軟體後處理方式,去除探棒或治具對測試結果的影響 (圖片來源:宜特科技)

埠實體層符合性測試

Port Physical Layer是網路協定中的埠實體層,負責資料在設備與網路或其他設備間的傳輸。實體層符合性測試用於測試設備的實體層是否符合特定協定的技術規範,確保其能穩定、有效地傳輸資料,避免訊號失真或干擾。

業者只需要提供半成品板和介面資料,即可進行測試驗證,協助在硬體或是系統層面符合特定標準,確保其正常運作,並滿足規範要求;同時也可以進行故障診斷與排除(Debug)服務,確保產品順利運行。

實體層相關測試

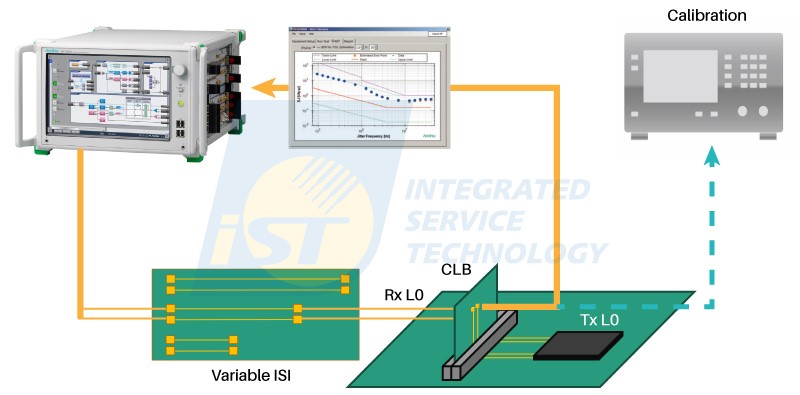

(1)PCIe 5.0/6.0預符合性測試(Tx/Rx/100M Clock):測試PCIe 5.0和6.0的傳輸性能,確保其符合預定的時序和訊號完整性要求,包含PCIe電氣特性(PCIe Electrical Test)與協定測試(PCIe Protocol Test)。

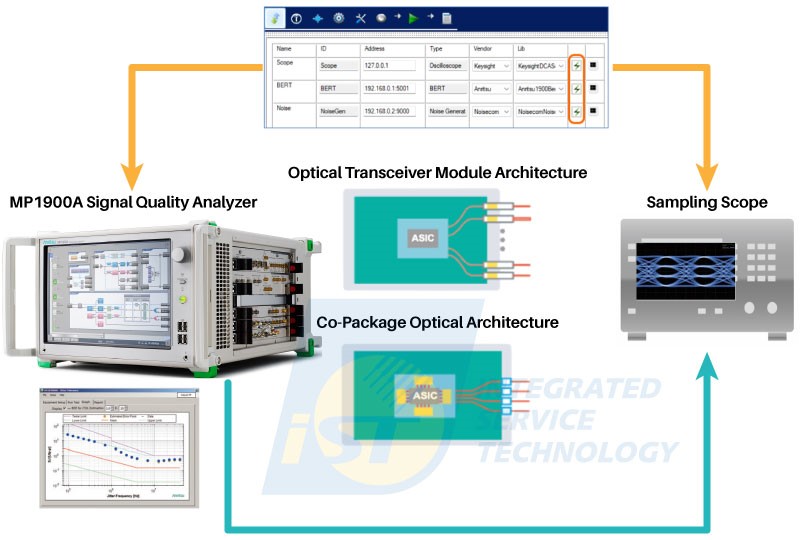

(2)Ethernet 400/800G符合性測試(IEEE 802.3bj/bs/ck):驗證Ethernet 400G和800G的性能是否符合援QSFP-DD及OSFP等高性能光纖模組標準,確保其在高速資料傳輸中的可靠度。

圖5 PCIe5.0/6.0 Rx測試解決方案 (圖片來源:安立知/編修:宜特)

圖5 PCIe5.0/6.0 Rx測試解決方案 (圖片來源:安立知/編修:宜特)

圖6 100G BaseE CR/KR Ethernet Rx測試解決方案 (圖片來源:安立知/編修:宜特)

圖6 100G BaseE CR/KR Ethernet Rx測試解決方案 (圖片來源:安立知/編修:宜特)

客製化測試治具設計

在高速訊號測試過程中,客製化測試治具除了可提升測試效率、縮短開發週期,還能避免不合適治具導致的測試誤差,確保產品的高性能與可靠度。宜特可根據客戶需求,設計專屬的測試治具,並提供從計畫、設計、測試驗證到生產的一條龍服務,確保測試設備的效果和符合特定要求。

AI推出高速訊號傳輸需求 測試分析確保產品性能

生成式AI的興起,加速了高速訊號市場的成長。測試實驗室所提供的解決方案及服務有助業者因應AI趨勢推出相應產品,例如,宜特訊號測試實驗室便憑藉多年來累積的高速訊號測試經驗,結合業界相關設備,以及和全球標準組織如USB-IF、HDMI協會及VESA所建立的緊密合作關係,提供精準的測試和分析。不論是伺服器、交換器、AI加速運算卡,還是邊緣運算裝置如PC、遊戲主機、繪圖卡、機上盒、監視器及電視等的設計開發,宜特都能協助產品迅速進入市場。

(本文由宜特科技提供)