今日,研發者在市面上擁有眾多的類比數位轉換器(ADC)選項,而在進行選擇時,所要考量的其中一項重要參數,便是元件內含數位輸出端的類型。目前高速轉換器主要採用三種最常見的數位輸出端類型,其分別是互補式金屬氧化物(CMOS)、低電壓差動訊號(LVDS)、以及電流模態邏輯(CML)。

ADC採用的這些數位輸出端各有其優缺點,因此研發者應考量它們在特定應用中運作的情境。其中應考量的因素,包括ADC的取樣率與解析度、輸入資料率、系統設計的電源需求等。本文將探討每種輸出的電氣規格,以及每種輸出端適合的特定應用。另外,接下來也將比較這些輸出端的實體建置、效率以及它們適合的應用。

CMOS驅動器實現多輸入/低電流

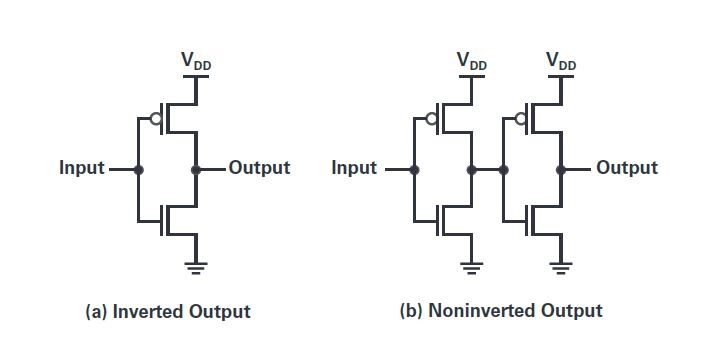

對於取樣率低於200MSPS的ADC,採用的數位輸出端通常為CMOS。一般採用的CMOS驅動器內含兩個電晶體,一種為NMOS,另一種則是PMOS,其用來連結電源(VDD)以及接地端,如圖1a所示。這種結構會使輸出反轉,因此如圖1b所示的背對背(Back-to-back)結構可用來避免輸出端出現反轉。CMOS輸出驅動器的輸入屬於高阻抗,而輸出則是低阻抗。在驅動器的輸入端,兩個CMOS電晶體的閘極阻抗相當高,原因是閘極和所有導電材料之間隔著閘極氧化層。輸入端的阻抗範圍介於kΩ到MΩ之間。驅動器的輸出端方面,阻抗受到汲極電流ID所影響,該電流一般都相當低。在這種情況中,阻抗一般都低於數百歐姆。CMOS的電壓在VDD 到接地之間的範圍擺動,在VDD的影響下,此電壓通常相當高。

圖1 典型CMOS數位輸出驅動器

圖1 典型CMOS數位輸出驅動器

由於輸入阻抗相當高,而輸出阻抗相對偏低,因此CMOS有一項優點就是一個輸出能驅動多個CMOS輸入。CMOS另一項優點就是較低的靜態電流。唯一會出現大量電流的情況就是CMOS驅動的切換事件。當驅動器處在低態(Low State)、上拉至接地(Ground)、或是處在高態(High State)上拉至VDD,在這些狀態中流經驅動器的電流都相當低。但當驅動器從低態切換至高態,或是從高態切換至低態時,在VDD到接地端之間就會形成一個瞬時低電阻通道;當轉換器速度超過200MSPS時,促使輸出驅動器須採用其他技術的其中一項原因,就是這種暫態電流。

轉換器在處理每個位元資料方面也需要用到CMOS驅動器。若轉換器為14位元,那麼就需要14個CMOS輸出驅動器來傳送這些位元。在一個元件封裝中通常會裝入超過一個轉換器,一般在一個封裝內最多會有8個轉換器。在運用CMOS技術時,這意謂著光是資料輸出就需要多達112個輸出針腳。這樣的配置除了無法封裝,還會使功耗變得極高,而且電路板的布線也更為複雜。因此為了解決這些問題,業界開始趨向採用LVDS介面。

LVDS驅動器低電壓驅動並消除電磁干擾

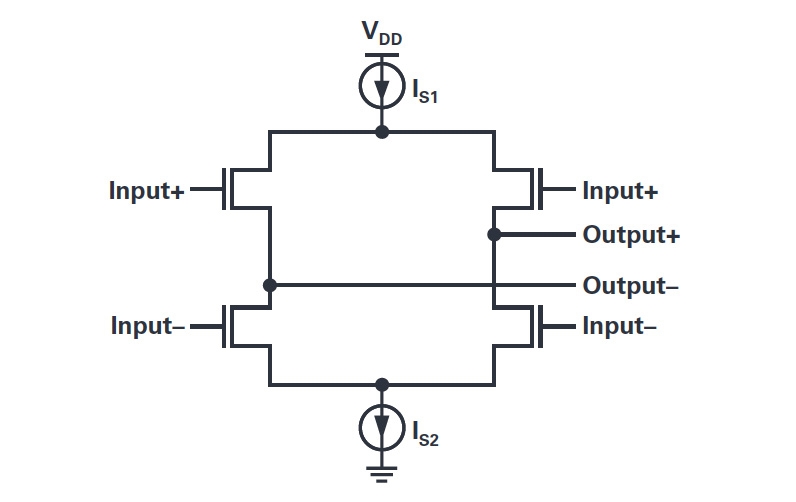

LVDS提供幾項勝過CMOS技術的優點,包括能以大約350mV的低電壓訊號運作,以及採用雙端的差動,而不是單端型態。此外,較低的電壓擺幅會形成更快的切換時間,同時也消除了電磁干擾的問題。另外由於採用差動訊號,因此也具有共模拒斥的優點。這意謂著混入到訊號中的雜訊,通常會同時出現在兩個訊號通道,而且大多數會被差動接收器消除。LVDS的阻抗必須更嚴密地控制。在LVDS中,負載電阻必須為100歐姆,通常是由LVDS接收器的並聯終端電阻達成。此外,LVDS訊號必須藉由控制阻抗傳輸線路來繞送。單端阻抗必須為50歐姆,而差動阻抗則維持在100歐姆。圖2則顯示了典型的LVDS輸出驅動器。

觀察圖2裡LVDS的拓撲,可以看出電路的運作導致輸出端供應固定的直流負載電流。這種機制可防止一般CMOS輸出驅動器在輸出邏輯瞬態時出現的電流突波。電路中額定的流入/流出電流設定為3.5毫安培,因此使用100歐姆終端電阻時,輸出電壓擺幅為350mV。電路的共模值通常設為1.2V,而且相容於3.3V、2.5V,以及1.8V的供電電壓。

圖2 典型LVDS輸出驅動器

圖2 典型LVDS輸出驅動器

目前業界針對LVDS介面規範了兩項標準,其中最常被採用的是低電壓差動訊號介面電路的電氣特性(ANSI/TIA/EIA-644);另一種則是IEEE協會的1596.3標準,名為低電壓差動訊號針對可擴充整合介面(SCI)規畫的IEEE標準。

在LVDS中,確實需要特別留意訊號繞線的實體配置,但在取樣率超過200MSPS的環境中,它能為轉換器提供許多優勢。LVDS驅動器的恆定電流讓系統能驅動許多輸出,不像CMOS必須消耗大量電流。此外,低電壓差動訊號能在雙倍資料率(DDR)模式下運作,透過同一個LVDS輸出驅動器同時繞送兩個資料位元。這樣的機制所需用到的針腳數量比CMOS少了一半。此外,輸出相同數量資料所耗用的電力也會降低。

LVDS確實在轉換器的資料輸出方面提供許多勝過CMOS的好處,但它本身也和CMOS一樣存在許多限制。當轉換器的解析度提高時,LVDS介面需要的資料輸出數量會導致電路布線更為困難。此外,轉換器的取樣率最終會促使介面所需的資料率超出LVDS能力範圍。

CML提高資料傳輸率並減少針腳數

轉換器在數位輸出介面的最新趨勢,就是在採用的序列介面中運用電流模態邏輯輸出驅動器。通常轉換器如需要較高的解析度(≥14位元)、更高的速度(≥200MSPS),且希望封裝更小、功耗更低,就會採用這些種類的驅動器。最新轉換器採用的JESD204介面,其內部就用到CML輸出驅動器,運用CML驅動器搭配序列JESD204介面,可讓轉換器輸出端的資料傳輸率能提高到12Gbps(支援JESD204B規格的最新改版)。此外,輸出針腳的數量也可以大幅減少。另外由於時脈已嵌入到8b/10b編碼資料流,因此不需要另外單獨一個時脈訊號。資料輸出針腳的數量也會隨之減少,最低只需用到兩個。隨著轉換器的解析度、速度,以及通道數量增加,資料輸出針腳的數量也可跟著提高,以因應更高的吞吐量需求。CML驅動器所搭配的介面通常是序列式,但針腳增加的數量相較於CMOS或LVDS卻明顯偏低(這是因為CMOS或LVDS傳送資料屬於平行模式,因此需要的針腳數量要高得多)。

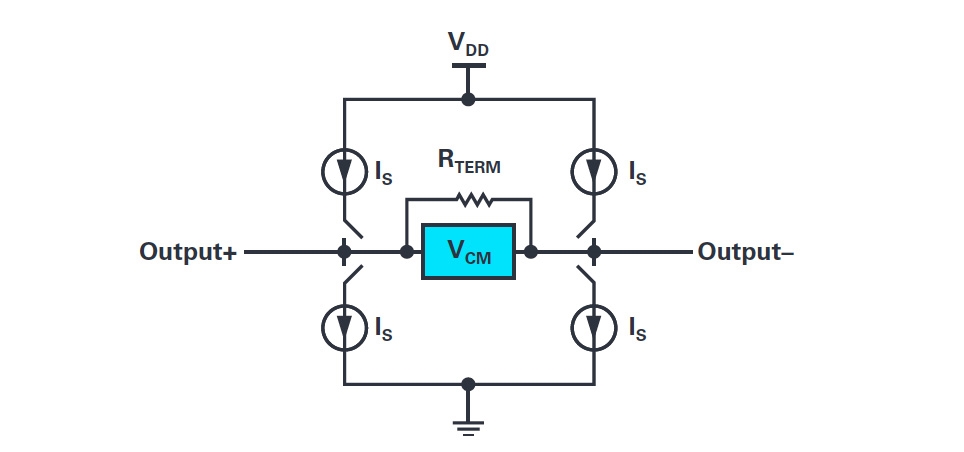

由於序列化資料介面採用CML驅動器,因此所需的針腳數量大幅減少。圖3便顯示JESD204或同類型資料輸出標準的轉換器採用了典型CML驅動器,圖中顯示CML驅動器的典型架構。電路的輸入端負責驅動電流源的切換器,而電流源則會驅動邏輯值,該值會影響兩個輸出終端。

CML驅動器類似以恆定電流模式運作的LVDS驅動器,這項特性也讓CML驅動器擁有功耗方面的優勢。由於在恆定電流模式運作,以致需要的輸出針腳也比較少,整體功耗也得以降低。反觀LVDS,則需要負載終端機制,同時控制阻抗的傳輸線路也需要50歐姆的單端阻抗,以及100歐姆的差動阻抗。而驅動器本身也需要終端機制,如圖3所示,以防止像高頻寬訊號產生的反射。在採用JESD204標準的轉換器方面,依據運作速度的不同,差動以及共模電壓方面各有不同的規範。像是在6.375Gbps速度運作時,額定的差動電壓為800mV;當速度低於12.5Gbps,規範的差動電壓值則為400mV,而共模的電壓則大約為1.0V。隨著轉換器速度與解析度持續攀升,CML輸出需要驅動器能提供夠高的速度,以因應轉換器在各種應用中的工作需求。

圖3 典型CML輸出驅動器

圖3 典型CML輸出驅動器

數位驅動器時序具多考量因素

這些種類數位輸出驅動器的時序關係必須嚴加監視。由於CMOS與LVDS有多個資料輸出,因此注意焦點應放在訊號的繞送路徑,將訊號偏斜(Skew)減至最低。倘若偏差過大,接收器就無法達成正確的時序。此外,時脈訊號也需要繞送並和資料輸出進行校準。時脈輸出與繞送路徑之間也需要仔細考量與注意,另外還有資料輸出,以確保偏斜不會過大。

在JESD204介面的CML方面,還須注意數位輸出之間的繞送路徑。由於要管理的資料輸出大幅減少,因此這方面的工作比較容易,但也不該將其忽視。在這個案例中,由於時脈已嵌入在資料中,因此和資料輸出以及時脈輸出之間的時序偏斜沒有關係。該注意的是接收器上適合的時脈與資料回復線路。

除了偏斜之外,CMOS與LVDS方面還須注意建立(Setup)與保留(Hold)時間。資料輸出必須驅動到適合的邏輯狀態,而且必須在時脈曲線邊緣轉換之後繼續維持在邏輯狀態足夠的時間。這方面的能力會受到資料輸出與時脈輸出之間偏斜的影響,因此重點在於必須維持良好的時序關係。LVDS由於訊號擺幅較低以及差動訊號機制,因此擁有勝過CMOS的優勢。LVDS輸出驅動器不必將這麼強的訊號驅動到多個不同的輸出端,而且不像CMOS驅動器在各邏輯狀態之間切換時會從供電電源消耗大量的電流,因此在變更邏輯狀態時比較不會出現問題。倘若有多個CMOS驅動器同時切換,電源電壓可能會被拉低,進而出現許多問題,影響到把邏輯值送到接收器的能力。而LVDS驅動器能維持在恆定的電流值,因此不會出現上述的問題。此外,LVDS驅動器由於採用差動訊號,因此對於共模雜訊的抗擾性更強。至於CML驅動器也擁有類似LVDS的優點。這些驅動器也同樣具有恆定的電流,但不同於LVDS的是,由於其採用序列資料傳輸,因此需要的數量會比較少。此外,CML驅動器由於也採用差動訊號,因此對共模雜訊也具有抗擾性。

隨著轉換器技術朝更高的速度與解析度持續攀升,其採用的數位輸出驅動器也隨之演進以因應傳輸資料的各種需求。CML輸出越來越受歡迎,因為轉換器內的數位輸出介面逐漸轉向序列資料傳輸。然而,目前許多設計所採用的依舊是CMOS與LVDS數位輸出。由於每種數位輸出特別適合某些應用,因此這樣的採用策略也較為合理。每種輸出都面臨許多挑戰以及設計方面的考量因素,每種輸出也各有其優點。對於取樣速率低於200MSPS的轉換器而言,CMOS仍是適合採用的技術;而當取樣速率提高到200MSPS以上時,在許多應用中LVDS則成為比CMOS更為可行的選項。為進一步提高效率與降低功耗與封裝尺寸,可採用CML驅動器,並搭配如JESD204這類的序列資料介面。

(本文作者為ADI產品應用工程師)