散熱設計與分析是改善元件可靠性的關鍵。本文分為三部分,將概述散熱設計的基本原理,包括客戶應用中的Qorvo元件熱阻分析,並提供詳細資訊說明,以協助工程師進行系統層級設計。

(承前文)RF元件散射設計系列文章的最後一部分,將著重討論高功率GaN元件的散熱考量,以及系統層級的散熱分析,並提供實作建議。

高功率GaN應用考量

針對高功率GaN應用,需要透過精準熱量測和適合的材料及設計來優化元件的散熱性能。

熱量測

若要執行GaN元件和單晶微波積體電路(MMIC)的散熱分析,建議採取元件建模、實證量測(包括顯微拉曼熱成像法)和有限元素分析(FEA)模擬的整合式做法。此方法經過證實,是最有效也最準確的做法。使用此方法後,一旦基線熱模型發展完成,便會採用FEA準確預測元件層級的通道溫度和熱阻。

如果無法執行顯微拉曼熱成像法和FEA建模,且只有紅外線(IR)攝影機可用的話,則必須明確瞭解IR成像的準確度限制。IR攝影機具有大於FET通道閘極長度的空間解析度,並且會產生面積平均值的表面溫度,此數值將顯著低於實際的最高通道溫度。建議與GaN元件應用團隊密切合作,以確保GaN元件在應用中的運行溫度足夠低。應用團隊也可提供產品的總體熱模型,以便套用至系統層級熱模型,進而在系統層級模型中更準確地估算元件運行環境,並確認所得的接面或通道溫度。

改善應用的熱傳導係數

採用不同黏著封裝方案的應用具有不同散熱考量,以下分別說明各式應用能夠如何優化散熱表現。

若採用GaN晶粒元件,晶粒應直接黏著在可導熱的散熱片材料或中間載板上(例如die-on-tab)。黏著晶粒時,應使用金錫共晶焊料(為佳),或高導熱環氧化物。散熱片則可與下一層級組件整合,或者使用焊料或導熱環氧化物,將die-on-tab直接黏著於下一層級組件的散熱片。

金錫焊料和許多導熱環氧化物的熱阻值低,並且能夠因應熱膨脹係數(CTE)的不對等應力 (常見於將GaN晶粒黏接至高導熱材料時)。金錫焊點需要確保沒有任何孔隙,尤其是晶粒作用區域下方。如果使用導熱環氧化物,則黏接必須一致且無空隙,並且形成一道薄接合線(以發揮最大熱傳導效果)。

整體來說,除非黏著至高導熱塊(如銅塊)以確保充分散熱,否則並不建議將GaN晶粒功率元件直接黏著至印刷電路板(PCB)。

GaN QFN和表面黏著封裝元件均直接黏著於PCB上。這些GaN放大器一般用在處於CW模式或脈衝應用的中等功率消耗應用。在這些應用中,需要透過銅質散熱導孔建立可將熱流導往系統散熱片的散熱路徑。導孔的大小、排列方式、類型與鍍銅量應仔細選擇,以優化PCB設計的整體熱傳導。若採用QFN封裝的GaN元件,一般會盡可能減少PCB的厚度(如0.008吋),藉此降低熱阻。使用搭載高密度導孔陣列(Via Array)的薄型PCB至關重要,對於高頻GaN MMIC來說尤其如此。

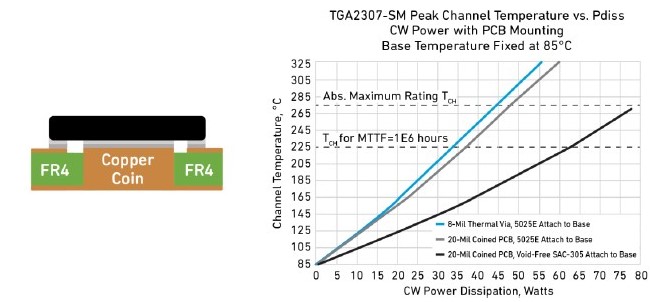

傳導路徑通常是將熱能排出元件最有效的方式。若放大器採用QFN和表面黏著封裝,且封裝底部面積平均CW熱通量(Heat Flux)大於1W/mm2,則十分建議使用散熱塊PCB,以便為系統散熱片提供更佳散熱路徑(影響程度請見圖13範例)。熱通量只要超過2W/mm2,則封裝下方皆應設有銅塊。如圖13所示,一旦功率高於10至15瓦,最好使用搭載銅塊的PCB,以確保應用符合可靠性與效能標準。

圖13 GaN元件下方銅塊結構(左)及導孔和散熱塊比較(右)

圖13 GaN元件下方銅塊結構(左)及導孔和散熱塊比較(右)

在高功率GaN封裝電晶體或封裝MMIC與散熱片之間提供優質的熱介面非常重要。封裝不佳是散熱失敗的主因。在高功率情況下,如果選擇黏著凸緣式封裝,建議採用厚度2至4密爾(約50~100微米),並且是以導熱材料製成的熱介面材料(TIM),如銦片(Indium Sheet)或石墨烯薄膜(Graphite Film),或者使用厚度1~2密爾(約25~50微米)的一層散熱膏或散熱材料,將這些散熱材料覆蓋整個封裝底部區域。

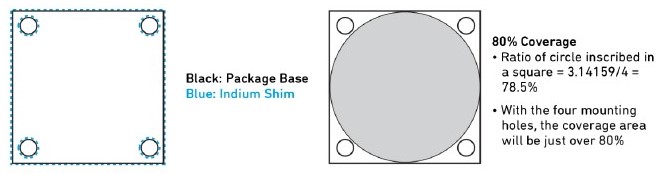

關於熱介面材料,有一件事需要特別注意:此材料需要有足夠的壓力才可發揮良好的熱傳輸效果。使用散熱膏或散熱材料時,覆蓋率至少必須達80%。關於銦片或散熱材料的建議使用方式,請參考圖14。

圖14 已封裝GaN元件下方的銦片(Indium Shim)與散熱材料範例

圖14 已封裝GaN元件下方的銦片(Indium Shim)與散熱材料範例

系統層級散熱分析

成功的系統層級設計重度仰賴可將熱能從半導體排出至外部環境的良好散熱路徑。從元件、封裝、PCB到最終散熱片的所有層級,都必須審慎考量熱流路徑。高功率GaN元件需要採用風扇冷卻系統的散熱鰭片或液冷系統,才能達到足夠的冷卻效果。

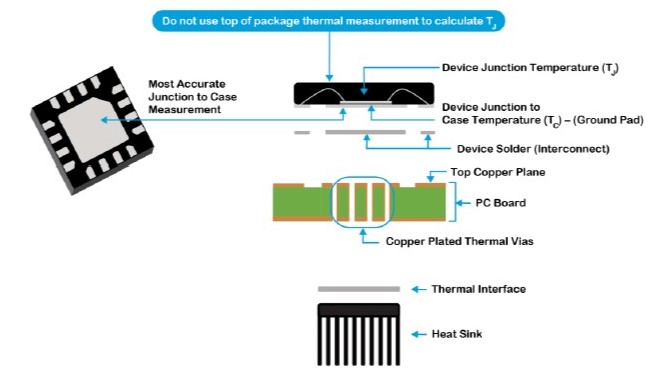

藉由估算元件的最大接面或通道溫度所決定的預期使用壽命,是評估半導體可靠性的一部分依據。這些數值可以透過對熱阻、功率消耗與熱傳輸進行量測與建模的方式來蒐集。在應用中,最大接面或通道溫度是關鍵指標,僅參考單一方式並非最佳做法;熱電偶/熱敏電阻量測、建模、IR影像等皆應採用。在如圖15所示的封裝類型中,應使用模型來確認元件下方的最大外殼溫度,以便以封裝熱阻為基準來估算接面溫度。

圖15 已封裝元件的外殼熱量測參考圖(一)

圖15 已封裝元件的外殼熱量測參考圖(一)

在系統層級散熱分析中,半導體元件的總體熱模型也將有所幫助。半導體供應商所提供的模型有助於設計人員模擬元件的輸出熱通量,進而幫助他們預估產品後端(Backside)的最高溫度值,以及元件在系統設計中的運行情況。此外,總體熱模型也可針對鄰近元件如何受到該半導體元件所排出的廢熱影響,提供更出色的見解。

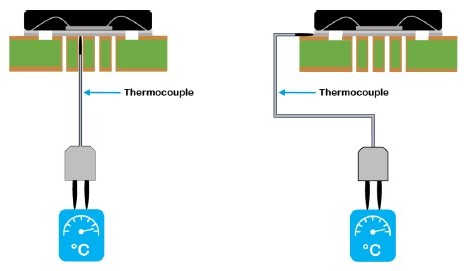

圖16 已封裝元件的外殼熱量測參考圖(二)

圖16 已封裝元件的外殼熱量測參考圖(二)

接面或通道至底部溫度(圖16),使用熱電偶以提供封裝底部的溫度。此方法固然可行,但應謹慎留意,確保熱電偶所讀取的區域正確無誤。如圖15所示,應於封裝接地墊或盡可能接近其底面(Underside)之處進行量測。如果在焊墊處(Pad Location)進行量測,則建議執行更多分析,例如使用產品的總體熱模型建立系統模型。

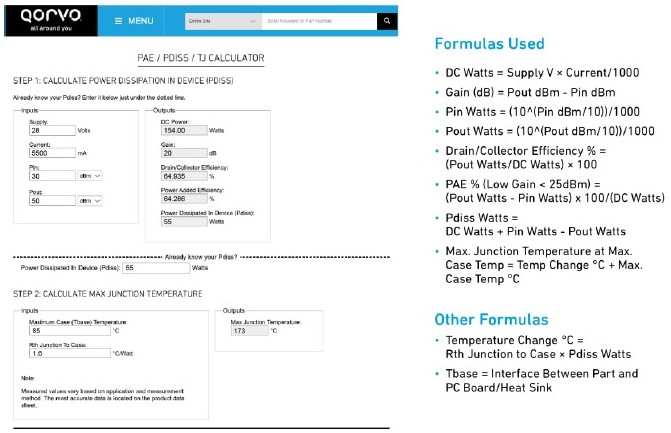

圖17 Qorvo PAE/Pdiss/TJ計算器

圖17 Qorvo PAE/Pdiss/TJ計算器

取得此外殼溫度後,下一步可計算功率消耗。Qorvo針對此需求提供線上計算器(圖17)。線上計算器也可用於計算元件的功率消耗與最高接面溫度。Qorvo教學影片[1]顯示如何以GaN元件使用此計算器。若為一般應用,可參考以下個案,以進一步了解此計算器的使用方式。使用PAE/Pdiss/TJ計算器的流程如下。

- 在計算器的STEP 1中,輸入元件的供應電壓、運作電流、輸入功率與輸出功率。

- 計算器會顯示這些數值的輸出,包括元件耗損功率(Pdiss)。

- 根據STEP 2的產品規格表,輸入外殼(TBase)最高溫度和Rth(J-C),以查看最高接面溫度。如果已知消耗的功率,則可在「已知Pdiss?」中輸入消耗的功率,接著輸入STEP 2中的兩個輸入值,以查看最高接面溫度。

半導體元件散熱效能至關重要

瞭解並確認半導體元件和系統設計的散熱效能是確保產品發揮最佳功能、可靠性與正常運作的關鍵。此系列文章的用意並非取代有限元素分析法及在此類量測與分析中所使用的軟體工具,而是提供散熱分析設計的指南。此系列所概述的方式與工具可為系統工程師提供實用的設計考量與熱量測方法。

(本文由Qorvo提供)

參考資料

[1] https://www.qorvo.com/design-hub/videos/understanding-gan-thermal-analysis

RF元件散熱設計(1) 解析熱量測/散熱基本原理

RF元件散熱設計(2) 材料選擇/PCB布局要點揭密

RF元件散熱設計(3) 高功率GaN/系統設計實作解析