從2020年起,預計今後10年每年將發射大約1,000顆衛星,提供電信、電視廣播、地球遙感觀測、天基(Space-based)網際網路及導航服務。

對於高傳輸量服務的需求以每年26%的速度成長,預計到2028年將達到8,000Gbps。豐富多樣的赤道同步軌道(GEO)和非GEO相關應用將創造150億美元的收入。

大多數衛星將代表Space 2.0營運商發射。他們計畫組建小型太空船(Spacecraft)構成的星鏈,針對利潤豐厚的天基網際網路和地球觀測資料分析市場。一般情況下,受功耗和成本的制約,這些小型太空船將在近地軌道(LEO)上停留三年到五年。Space 2.0營運商還樹立了更大的宏願,開始透過在其他軌道上提供競爭業務,推動市場多元化並挑戰傳統供應商。

此外,國防產業也在利用更廉價、更小型的衛星和更低廉的發射成本,計畫在所有軌道上組建行星鏈,為軍方提供高傳輸量、低延遲的通訊服務。

為提供優於競爭對手的性能和附加價值,傳統營運商和Space 2.0營運商都在尋求超高傳輸量有效載荷,以交付新一代衛星服務。

現有航太等級FPGA板載處理尚有局限

為解決數百Gbps範圍內的即時超高傳輸量的系統性能需求,需要新型可編程設計邏輯的架構設計方法。無論具體應用是以寬頻數位有效載荷為主的電信衛星、傳輸即時遙感資料的地球觀測太空船,還是回傳超高解析度影像的火星漫遊車,需要處理的訊息量都極為龐大。

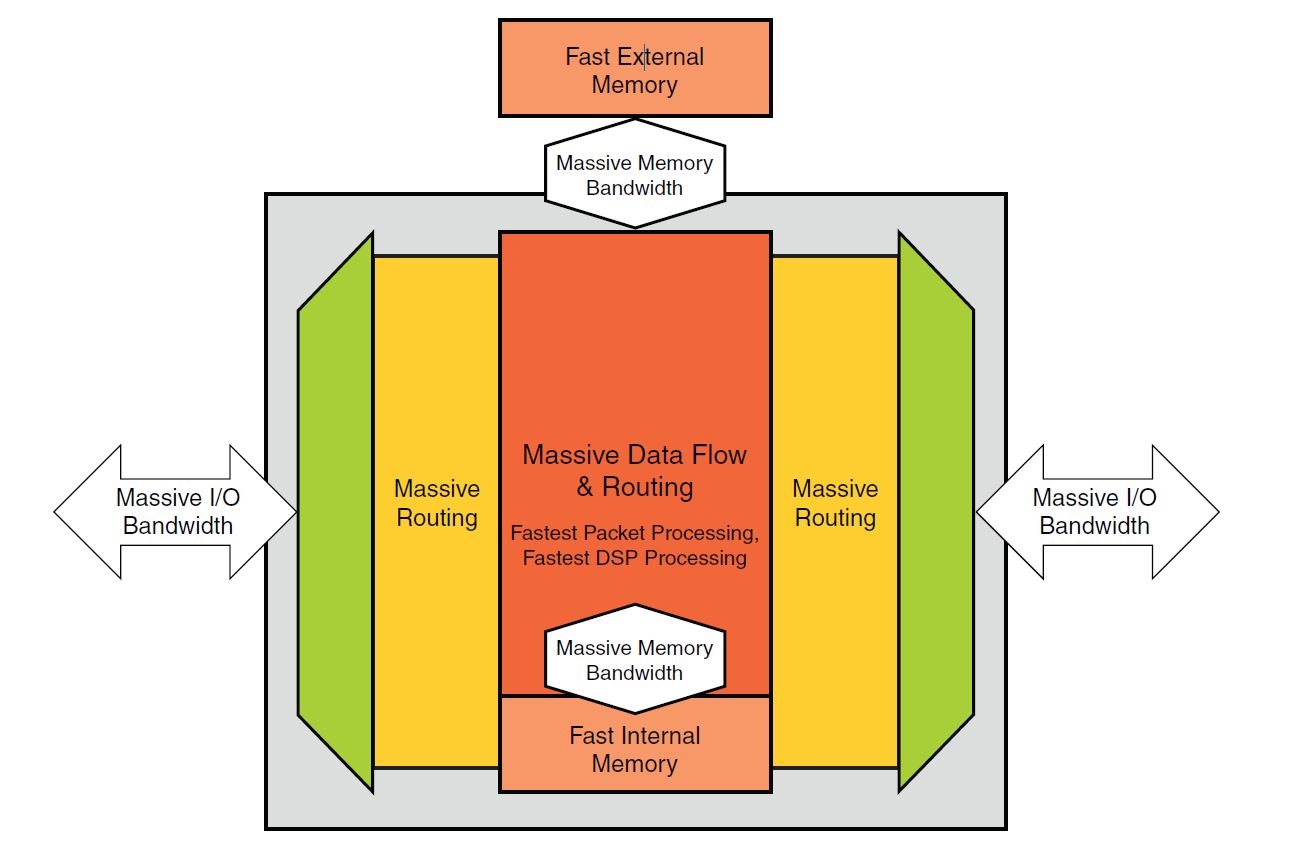

在系統中傳輸巨量資訊帶來的難題如圖1所示:數量達到數百Gbps的資料流透過I/O組或高速串列收發器,從左側輸入並從右側輸出。未來的有效載荷需要即時處理這些資料,並且隨著資料進入FPGA,就必須立即扇出,以匹配單晶片資源的資料流程、路由和處理能力。

圖1 需要大規模頻寬的高性能系統

圖1 需要大規模頻寬的高性能系統

例如,假定左側和右側的埠I/O頻寬是400Gbps。這就要求FPGA的邏輯、運算和記憶體資源必須處理至少400Gbps的流量。設計工程師一般使用寬度在512位元到2,048位元的大寬度匯流排來管理這樣的傳輸量。

運作在高頻率但使用較窄資料路徑的設計,經常受時序(Clocking)偏差而性能劣化的不利影響,極端情況下時序偏差可接近總時序週期的50%。這使得執行實際運算的時間所剩無幾,導致設計人員不得不高度地管線化其設計。除了消耗大量的寄存器資源以外,大量管線化還會給總體系統延遲造成顯著影響,這在今天的高性能系統中是不可接受的。

較寬的匯流排實現方案不僅可能需要較低的系統時序頻率,而且因為缺乏支援大寬度匯流排所需的布線資源,還會造成顯著的時序收斂難題。加上部分FPGA廠商使用陳舊類比退火演算法的布局布線演算法,不能反映壅塞程度或總線路長度等全域設計指標,這使得情況進一步惡化。因此,設計人員被迫考慮需要降低系統性能(一般不應是選項)的折衷方案,如以增大延遲,或以可用元件資源總體利用率不足為代價的大規模管線化。無論針對哪一種情況,這些解決方案被證明要不是低效,便是不敷使用。

在應對數百Gbps資料量的應用時,布線資源普遍不足是如今所有的航太等級FPGA中存在的根本問題。這種情況導致的後果不是根本不可能實現新一代超高傳輸量衛星應用,就是將以極低的元件利用率或嚴重延遲為代價實現上述應用。

挑戰在於如何可靠地管理大量資料流程—輸入的高速資訊應在低時序偏差下扇出並路由到處理邏輯,同時用高傳輸量運算模組或DSP等超高頻寬功能模組處理即時運算所需的超高資料速率。輸入資料或中間結果必須迅速儲存在系統內(貼近處理單元的位置),或使用提供高記憶體頻寬的介面,儲存在靠近有效載荷的外部大量存放區內。處理完畢後,資料必須路由到I/O組或高速輸出收發器以進行再傳遞。

隨著內部資料匯流排加寬,需要處理的實體訊號數量增多,且往往透過大幅增加高速串列收發器數量實現板載化,設計的複雜程度也隨之增大,因此三大挑戰逐漸顯露出來;

・路由決定系統總體延遲

・時序偏差會消耗更大比例的可用時序裕量

・次優邏輯布局會降低系統性能

新FPGA設計瞄準航太應用

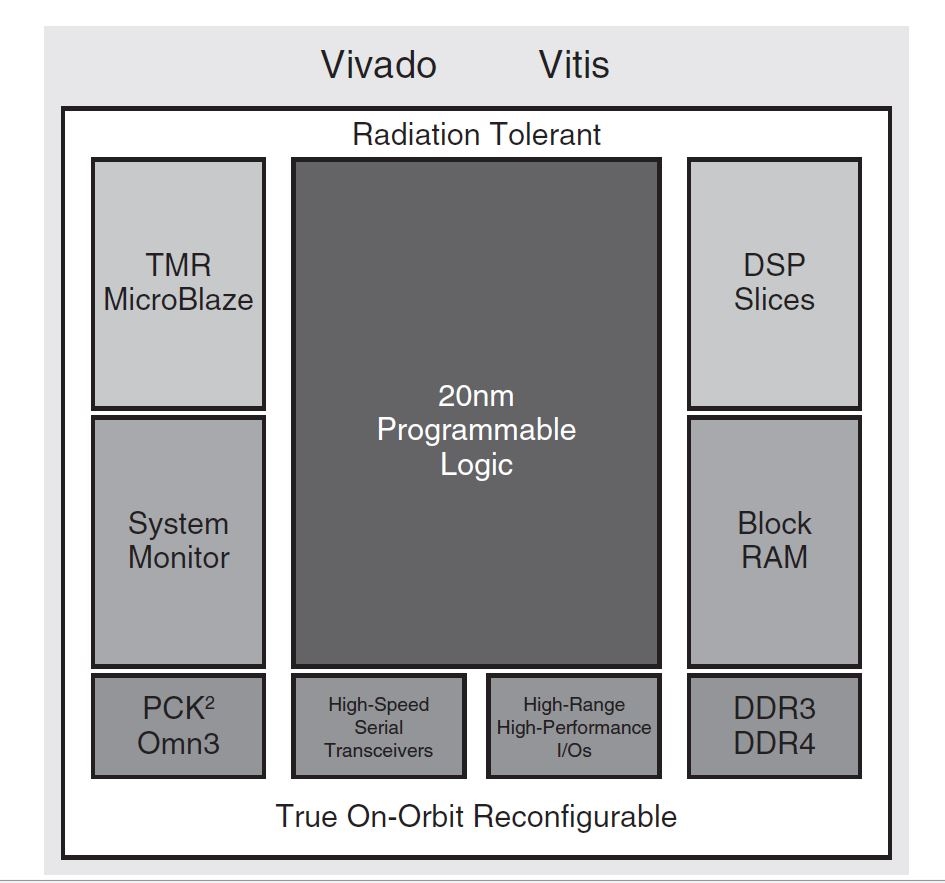

本文以賽靈思(Xilinx)RT Kintex UltraScale FPGA為例,其設計用於解決與高傳輸量、超大頻寬衛星有關的新一代系統等級性能要求。為解決上述問題,新架構的開發中採用了大量的創新和強化。

為了高效接收、緩衝、處理和發送新一代超高傳輸量衛星有效載荷所需的巨量資料,UltraScale FPGA架構從根本上改善單晶片通訊、I/O和記憶體頻寬、DSP功能、時序、關鍵路徑優化和互聯,以解決巨量資料流程與即時資料封包和影像處理需求(圖2)。具體創新包括:為大寬度匯流排優化的巨量資料流程支援數百Gbps的低延遲傳輸量;高度優化的關鍵路徑和整合高速記憶體,透過級聯消除DSP和資料封包處理中的瓶頸;功能得到強化的DSP切片,整合27×18位乘法器和雙加法器,實現定點和IEEE 754標準浮點運算性能和效率提升;大I/O和記憶體頻寬,包括支援DDR3和DDR4介面連接,同時大幅降低延遲。

圖2 RT Kintex UltraScale平台原理圖

圖2 RT Kintex UltraScale平台原理圖

同時,多區域類ASIC時序,提供時序偏差較低、性能擴展能力強的低功耗時序網路,並針對多種功能要素提供擁有強大靜態和動態電源閘控功能的電源管理,大幅降低功耗;而大規模路由能力,則能智慧化地解決典型瓶頸。這樣能顯著緩解布線壅塞,在基本或完全不劣化性能的情況下增加資源利用率。而在採用大規模平行匯流排架構的系統中,毋需使用會產生延遲的管線化,提高系統速度並增強功能;同時消除潛在時序收斂問題和互聯瓶頸(即使系統要求資源利用率達到或超過90%)。此外,採用AES位元流解密和身分認證、金鑰混淆和安全元件程式設計等先進方法,實現新一代安全功能。

透過綜合運用這些強化功能,可助設計團隊開發出與以往相比功能更強、運行速度更快、能夠提供更高單位功耗性能的系統。

新路由朝利用率/性能/運行遞進

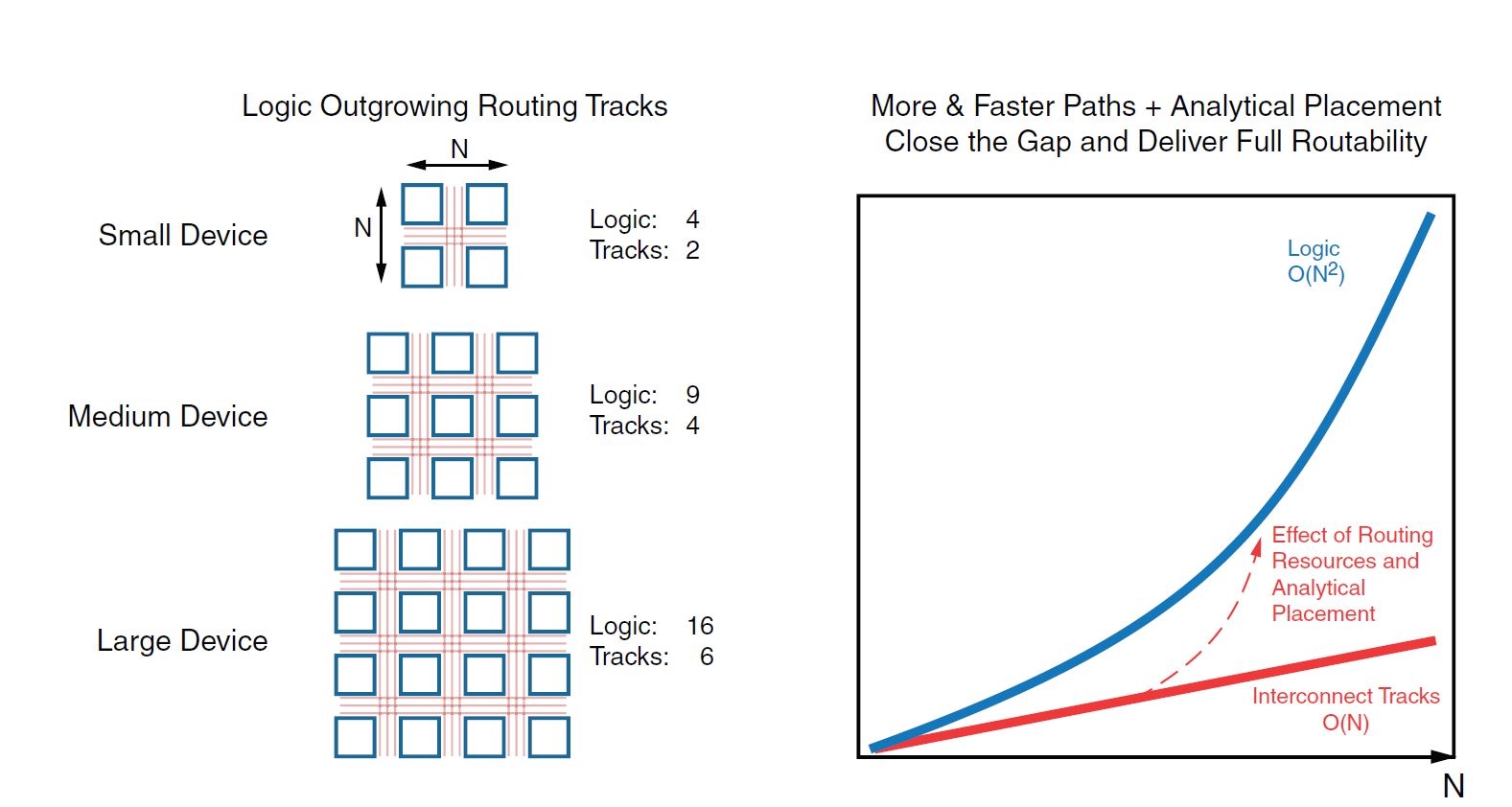

在採用常規FPGA架構時,邏輯資源以矩陣方式布局,構成行與列的互聯。隨著FPGA元件的密度增大到數百萬邏輯單元容量(相當於數千萬ASIC閘)時,按倍數平方(N2)遞增的邏輯數與按倍數(N)遞增的互聯通道數,兩者間的差異成為制約設計成功路由,實現所需性能水準的因素。

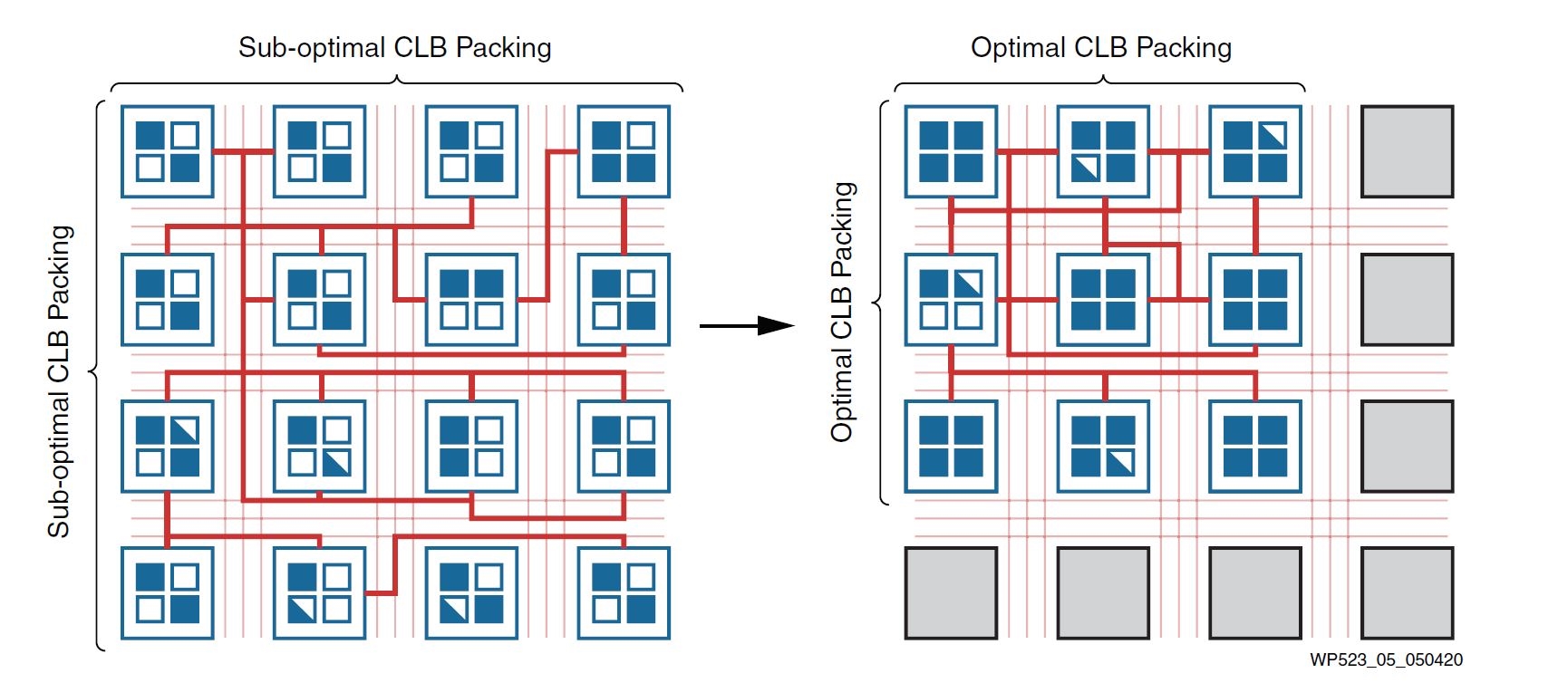

UltraScale架構透過增加所有元件中的互聯通道數量,在A、B之間提供更多直接路由,同時為軟體工具提供更多選項,以最快速度、最低功耗的配置連接邏輯資源,最終解決了這一難題(圖3)。

圖3 在UltraScale架構中添加路由

圖3 在UltraScale架構中添加路由

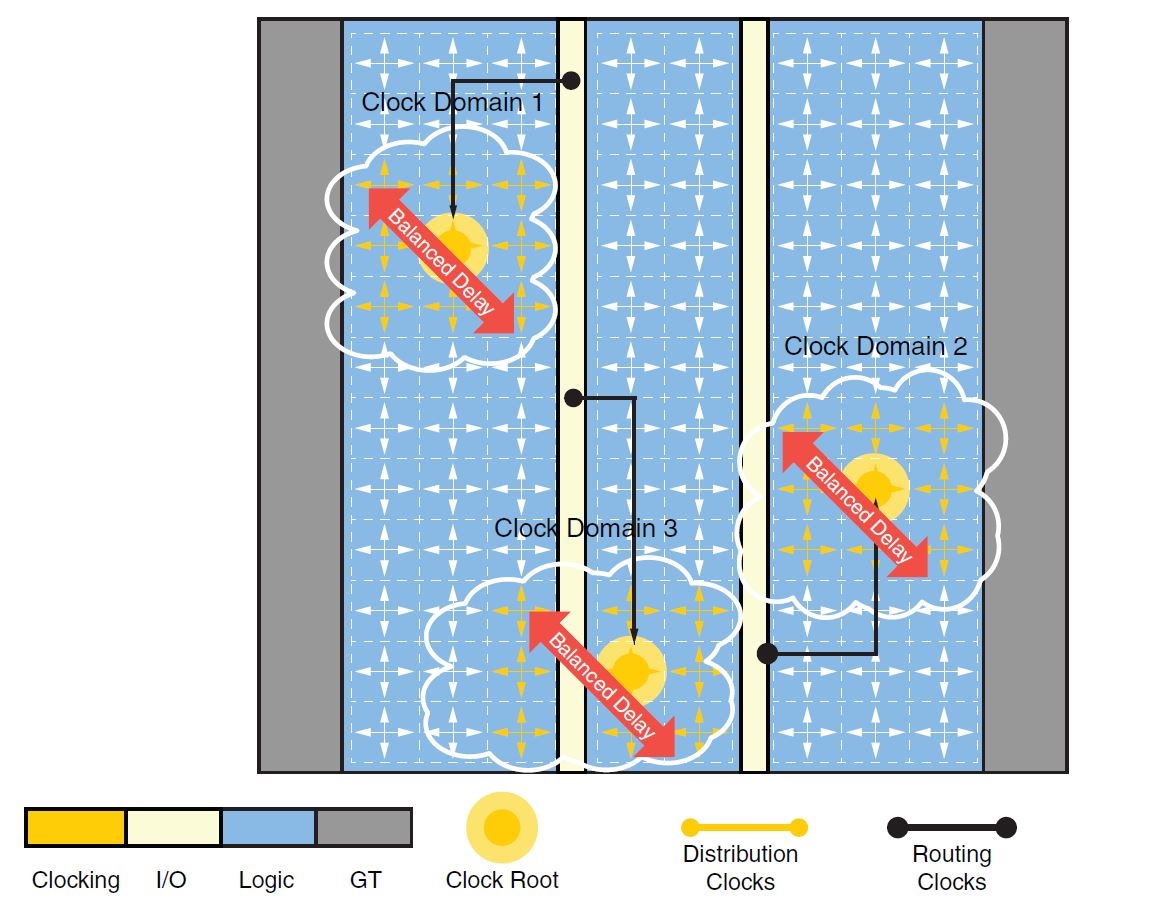

ASIC類時序助大幅提高性能

在該架構之前推出的FPGA主要採用幾何居中時序方案的扇出,將全域資源布局在元件中央。這些資源被扇出到FPGA的最邊緣,累積偏差。隨著容量不斷增大、系統性能不斷提高,整個晶片的時序偏差對於設計的總時序預算造成不利的影響。

而該架構下的時序路由和緩衝器經過重新設計,與既有的FPGA架構相比,可提供較高的彈性—其在橫向和縱向都提供充裕的時序路由和分配通道,全域時序緩衝器的數量是前幾代產品的20倍。從根本上談,時序網路的中心(即偏差開始累積的地方)可以布局在FPGA中的任意時序域內。這便於時序網路僅向需要的地方擴展,也只消耗從時序源向時序目的地傳輸時序訊號的功耗,就像ASIC一樣。

從系統設計人員的角度來看,布局大量獨立的高性能時序源有助於消除偏差問題。這可以避免進行大規模管線化及由此產生的延遲(圖4)。

圖4 UltraScale時序架構

圖4 UltraScale時序架構

設計中減少使用CLB縮短線路長度

在時序和資料訊號抵達邏輯資源後,UltraScale架構提供增強型CLB以高效利用可用資源,目的在於減少互聯,即線路總長度。全面分析現有的CLB結構,以探索如何更高效地運用CLB組件。由此綜合強化項目,讓Vivado設計套件能夠在CLB內布局數量明顯增多且往往無關聯的組件,實現更緊湊的布局。雖然運作在高頻率下,但透過實現最佳的總體元件利用率,這樣的設計可將功耗消耗降至最低。

CLB內的大量調整,為封裝選項增加了更多的彈性:每個6輸入LUT結合兩個分別擁有專用輸入輸出的觸發器,讓所有元件都能結合使用或是彼此獨立。觸發器受益於控制訊號數量的增多、彈性的增強,同時可用時序賦能訊號數量翻倍,時序賦能和重置埠提供可選的「忽略」選項,重置反轉支援在同一CLB內並存活躍高電平和活躍低電平重置觸發器,為移位暫存器和分散式RAM功能提供額外的時序訊號。 結合該架構布線資源完善和高度靈活的時序架構,CLB連接的大幅增加便於開發緊湊封裝的高性能設計,提高FPGA利用率,同時降低元件總功耗(圖5)。

圖5 邏輯資源的高效布局

圖5 邏輯資源的高效布局

新設計套件提高元件利用率

該FPGA架構使用Vivado設計套件來實作IP,其用於開發實現大型Tbps速度等級的低延遲超高傳輸量I/O、大寬頻匯流排和超大記憶體頻寬應用。坊間同類產品的布局布線工具採用類比退火演算法,既不能針對有數百萬LUT的設計進行擴展,也不能考量到總線路長度或壅塞。而該設計套件可使用布局布線分析技術找到可布線解,在不影響性能的情況下將元件利用率提高到90%以上。

為了對設計進行分析,確定瓶頸和問題發生的位置,並在這些問題發生前解決,因而開發了此設計套件。透過在封裝中緊湊排列邏輯單元,它們之間的線路長度有所縮短,進而不僅降低布線延遲,功耗也有所改善。此外,由於邏輯單元之間的距離有效縮短,驅動這些單元的時序訊號能夠以更短的傳輸距離覆蓋設計,進而降低時序偏差。此設計套件提供更高的元件利用率,同時也提高了用戶生產力。

如XQRKU060得到Vivado設計套件2019.1版(或更高版本)的支援,能夠編程設計FPGA,並將元件配置儲存在受支援的外部非易失性記憶體內。

FPGA新設計減輕且耐受輻射效應

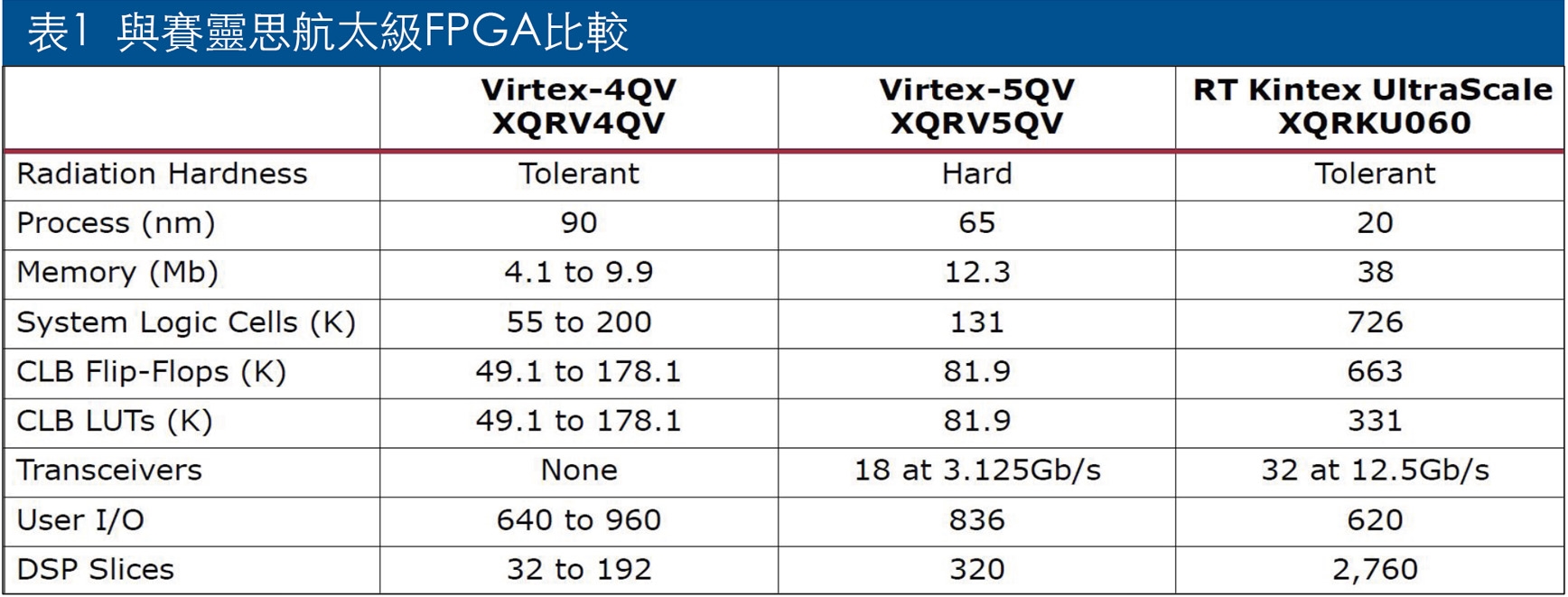

與之前推出的航太等級FPGA相比,新款FPGA可提供大幅增加的處理資源。航太產業首次能夠充分發揮20nm製程的優勢,採用專為最高板載性能優化的邏輯並降低功耗(表1)。

在與前一代65nm FPGA進行比較時,新款的功耗預算為前代產品的70%,收發器能力提高12倍、邏輯單元數增加5倍。透過在每一等級應用功耗降低策略,動態和靜態功耗都得以降低。

平面電晶體技術的CMOS縮放已從根本上減輕該款FPGA受全干擾和閂鎖效應的影響。配置記憶體單元的布局採用SEU設計規則加以優化,同時運用創新電路技術降低軟錯誤率,防止多位元翻轉。用戶借助Mentor Graphics或新思(Synopsys)提供的產業標準工具,能夠手動或自動配置三重多餘邏輯並將EDAC添加到FPGA的記憶體,以提高總體輻射耐受性。而像賽靈思SEM IP有助於進一步減輕輻射作用,可在配置記憶體中用於單粒子翻轉(SEU)的檢測、糾正和分類。針對翻轉,SEM IP使用Readback CRC功能定位和糾正錯誤;對於SEU分類,則使用Essential Bits技術進一步提升系統可用性,以便使用者管理系統等級回應,降低停運時間。

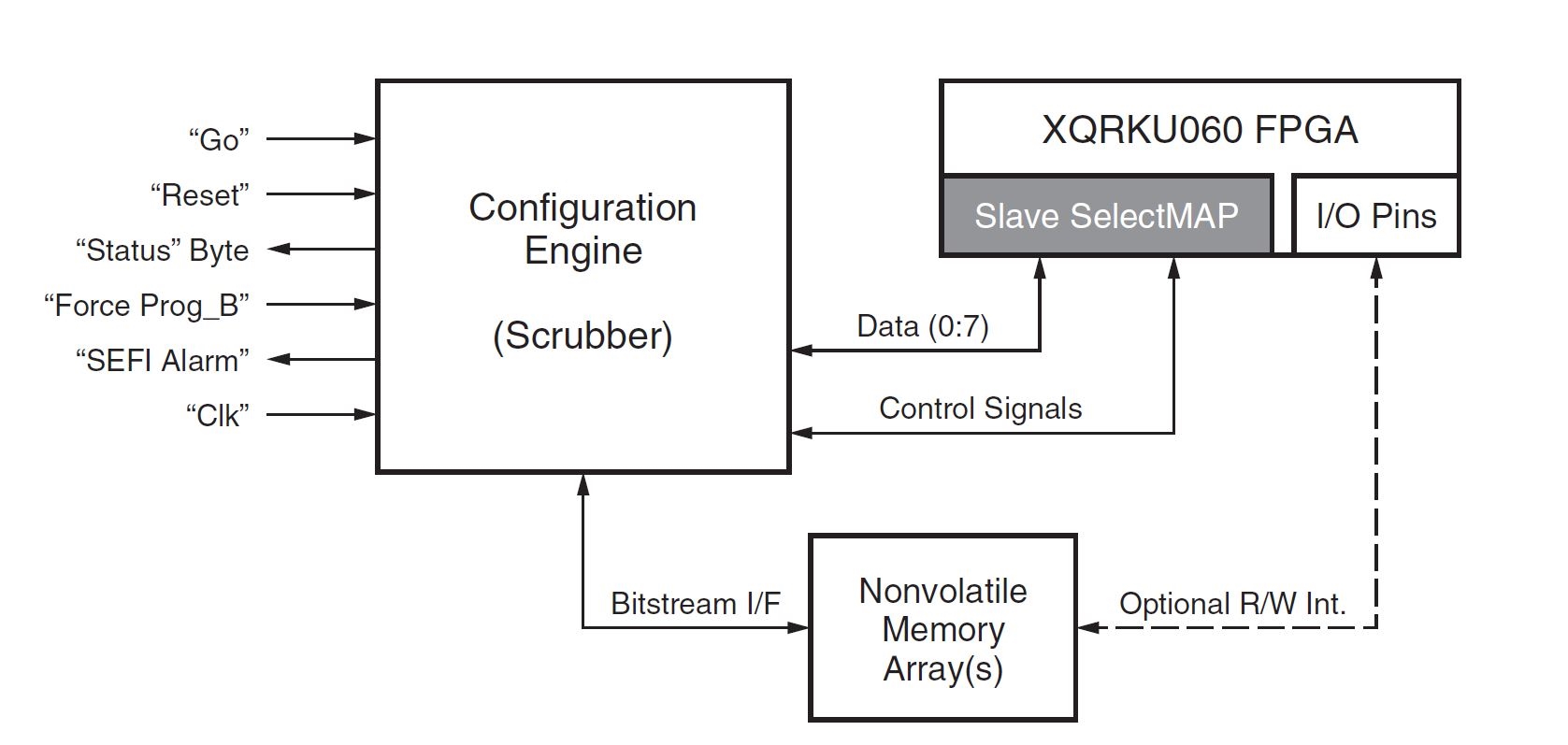

此外,也可以使用擦除功能強化可靠性,應用範圍從LEO太空載具在每個軌道運行期間的定期元件重組,到透過FPGA操作為GEO任務透明檢查並重寫單個訊框。如賽靈思提供外部RTL解決方案,進而配置FPGA套件,擦除該元件以防止SEU累積,同時檢測並糾正翻轉(圖6)。 第一階段的靜態和動態重離子測試已經在用戶要求的關鍵模組上完成,且未觀察到破壞性單粒子效應(SEE)。未來計畫對其餘模組開展進一步測試,最新結果將在賽靈思的SpaceLounge上公布。

圖6 外部擦除器

圖6 外部擦除器

測試使用1MeV的鈷60伽瑪(Gamma)、質子和重離子源,測量全干擾、SEL、SEU的回應;同時,在125℃、高供電電壓下,在高達80MeV-cm2/mg的情況下,未觀察到閂鎖效應。這其中包括高達3.3V的高壓供電I/O。相較之下,超深亞微米快閃記憶體型航太等級FPGA,在2.5V及3.3V I/O條件下,SEL敏感度有所提升。

根據2019年歐洲元件及其系統輻射效應會議(RADECS)上報告的進一步測試,全干擾耐受性達到120krad(Si)。實驗結果顯示,架構核心漏電最高增加7%,模組RAM、GTM收發器、I/O和DSP模組漏電<2%。在室溫偏置條件下經過一個星期的退火處理,所有元件都透過參數化AC和功能測試,最大傳輸延遲<1%。此外,報告也提供配置記憶體和模組RAM的重離子和質子測試的SEL和SEU資料。

使用CREME96太陽活動極小期模型,加上100mil的鋁遮罩,運算出的CRAM敏感度對LEO是2.4E-7次翻轉/位/天,對GEO是1E-8次翻轉/位/天;預估的模組RAM敏感度對LEO為4.7E-7次翻轉/位/天,對GEO為2E-8次翻轉/位/天。

2019年RADECS報告的結果認為使用賽靈思SEM IP能夠將可靠性和可用性提高3倍。該資源占據XQRKU060 FPGA配置記憶體將近4%總容量的空間。

FPGA具軌道重組能力

XQRKU060是一種使用SRAM的FPGA,方便在實驗室硬體開發階段和發射後在軌道進行重新程式設計。同類的航太等級抗熔斷FPGA只能配置一次,不僅無法進行原型設計,而且也帶來了時序驗證難度大、成本高等問題。

該FPGA對在軌重組的次數沒有限制,而使用快閃記憶體的同類FPGA產品則存在次數限制。90nm和45nm的同類航太等級ASIC的功能固定,完全無法重新程式設計。

該FPGA能夠在軌重組,賦予營運商較大的彈性,方便他們上載新的且更優異的通訊標準,以提高系統性能;對於技術展示衛星,能夠使用單個有效載荷完成多項實驗的原型設計工作;而對於需要儘快發射的任務,則能夠根據需要在發射後重新部署FPGA韌體。板載重新程式設計能夠縮小有效載荷硬體的大小,有助於使用各種演算法對應用、系統安全和容錯進行改善。

該FPGA的配置組支援多種記憶體介面以及各種串列及並行模式。在軌重組的替代選項是使用能儲存多個位元流的大型非易失性記憶體。其他方法包括使用板載電腦本地控制處於從模式的SelectMap和JTAG埠,或者透過TT&C載波或主上行鏈路上載新功能。

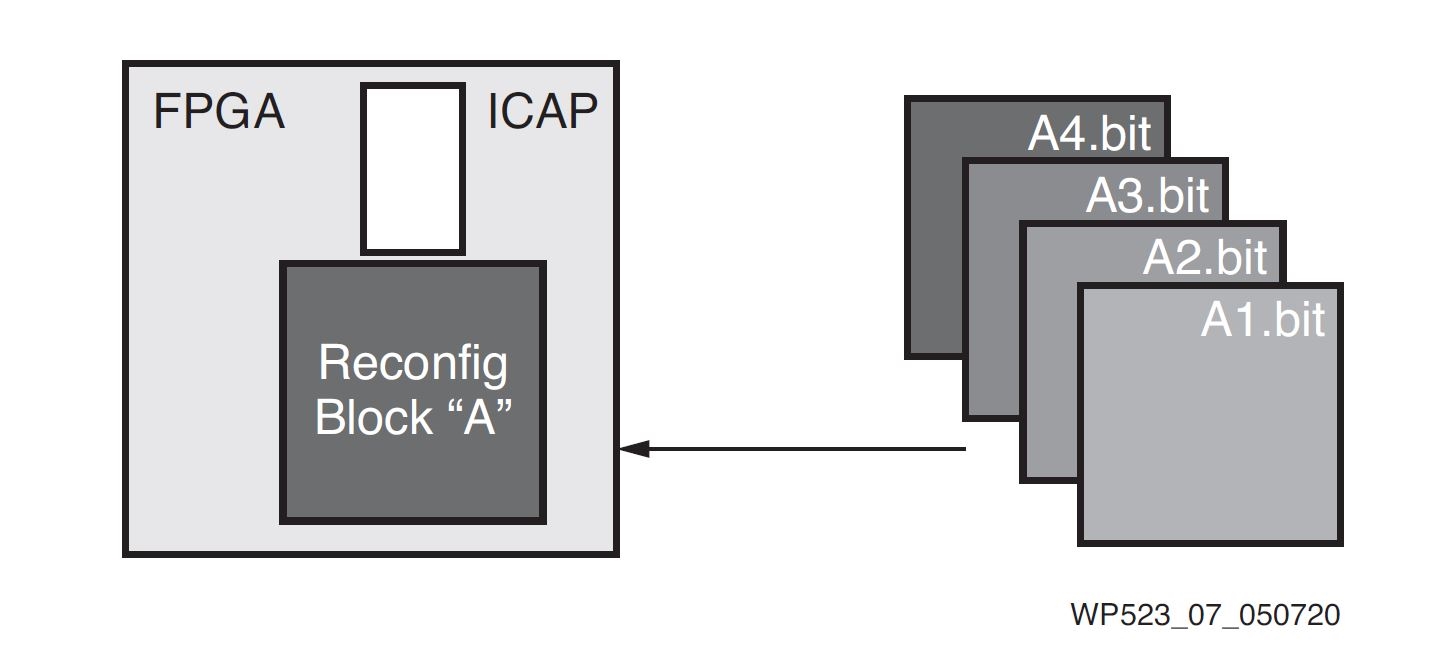

此外,在軌重程式設計還能在該FPGA於使用狀態下時動態即時完成,即在不影響元件內其他區域運行應用(使用導入的邏輯)完整性的情況下,用部分重組在FPGA內修改特定活躍區域。若使用ICAP或SelectMAP,可根據需要將模組換入或換出單個FPGA(圖7)。

圖7 特定使用者邏輯模組的部分重組

圖7 特定使用者邏輯模組的部分重組

元件可用性與認證

XQRKU060 FPGA為賽靈思B類(相容QMLB)和Y類(等效於QMLY)認證及DLA認證設計。所有可靠性等等級均達到-1M速度等級,額定工作溫度範圍為-55℃至+125℃,符合ECCN9A515.e.1出口管制要求。

封裝

該款FPGA的塑膠工業封裝(XCKU060)和陶瓷耐輻射封裝(XQRKU060)在設計中可採用相同的PCB占板面積。後者為前面兩種認證流程提供40×40mm 1509引腳CGA或LGA封裝,相容商用型A1517引腳分配。而為支援可靠性測試和環境測試,也提供菊輪鍊封裝。

容錯型CPU

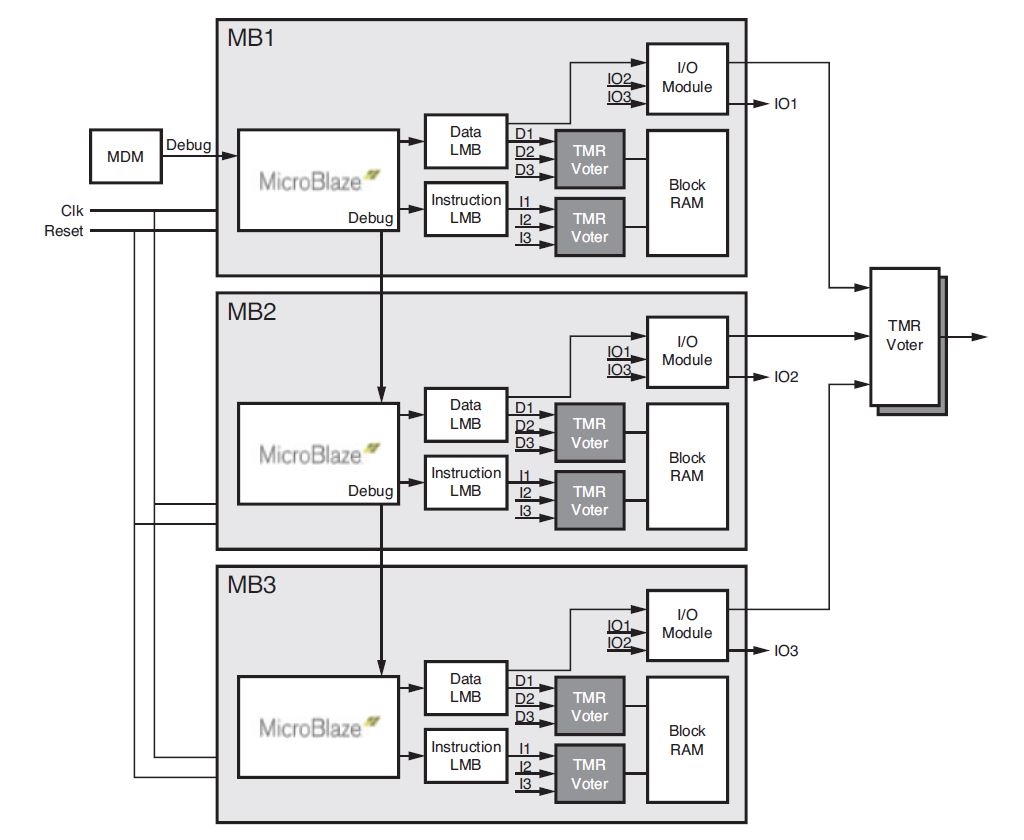

作為該款FPGA的補充,賽靈思也提供使用其MicroBlaze處理器技術的容錯型故障安全32位元RISC CPU,可產生實體在該FPGA內。該軟體IP的性能超過300MHz,需要大約7,400個LUT和6,400個觸發器,已使用TMR方案完成實現,如圖8所示。

圖8 容錯型故障安全TMR MicroBlaze處理器原理圖

圖8 容錯型故障安全TMR MicroBlaze處理器原理圖

數位波束成形電信衛星靈活因應需求

電信衛星營運商需要隨時隨地為行動客戶提供靈活的資料與廣播通訊服務,才能充分滿足即時的用戶需求和日新月異的流量需求。全域化的事件與需求瞬息萬變,如對飛機的持續監測,即時、日常或季節性的通訊需求,這包括對衛星發射訊號的覆蓋範圍、形狀、大小和功率的需求以及對衛星訊號的頻寬和通道容量需求等。

電信衛星越來越廣泛地使用相控陣天線和數位波束成形技術,將多個單獨的天線單元組合起來,以提升整體性能、增大增益、抵消干擾,同時將陣列定向在靈敏度最高的特定方向上。這便於營運商根據不斷變化的鏈路要求,即時改變和優化接收與傳輸。靈活的有效載荷方便營運商改變和調整頻率計畫和通道化頻寬,並提供「軌道通訊切換」,將上行鏈路路由到特定下行鏈路。

再生有效載荷透過在板解調,恢復上行鏈路損耗,提高系統整體性能,並減小下行鏈路天線尺寸。

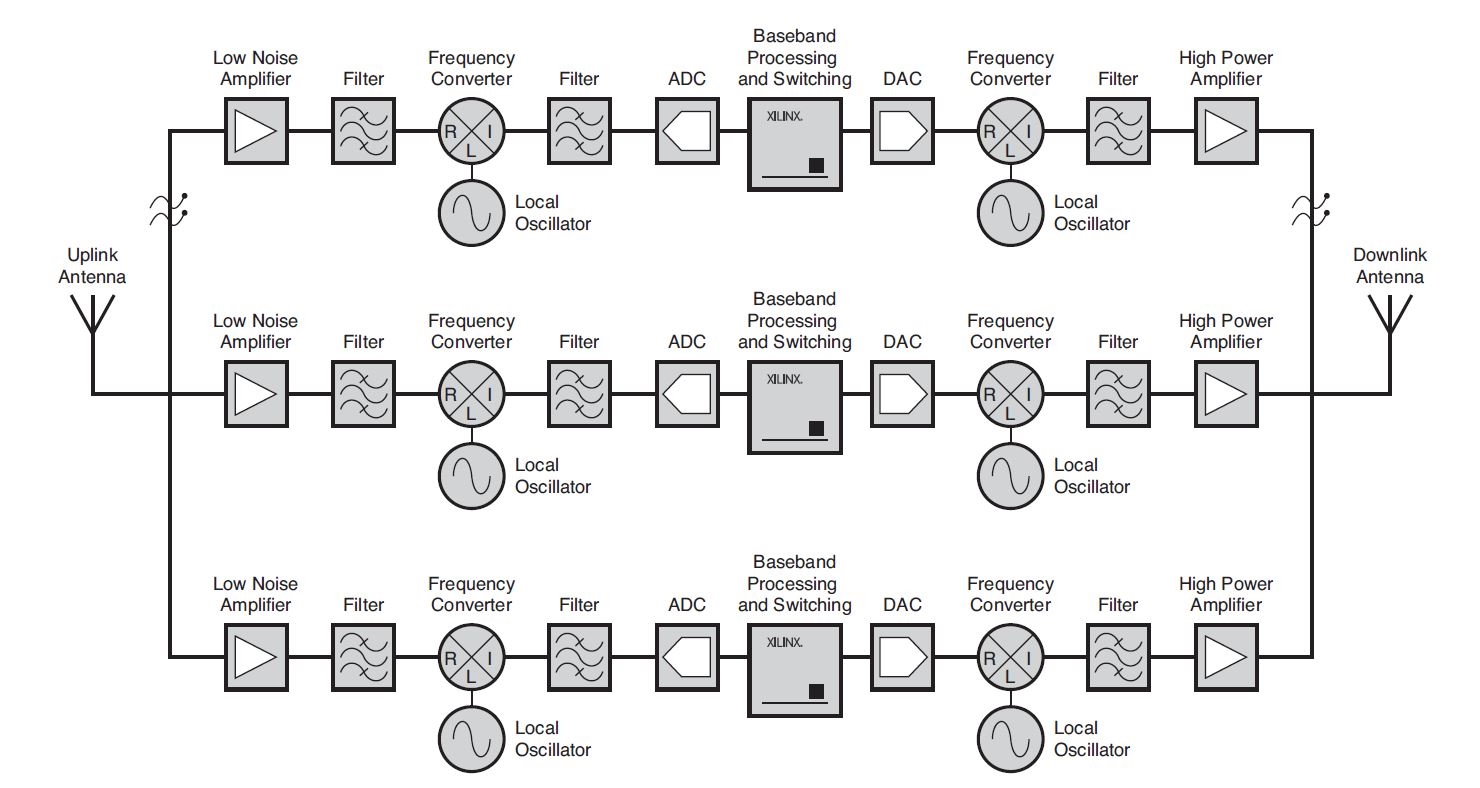

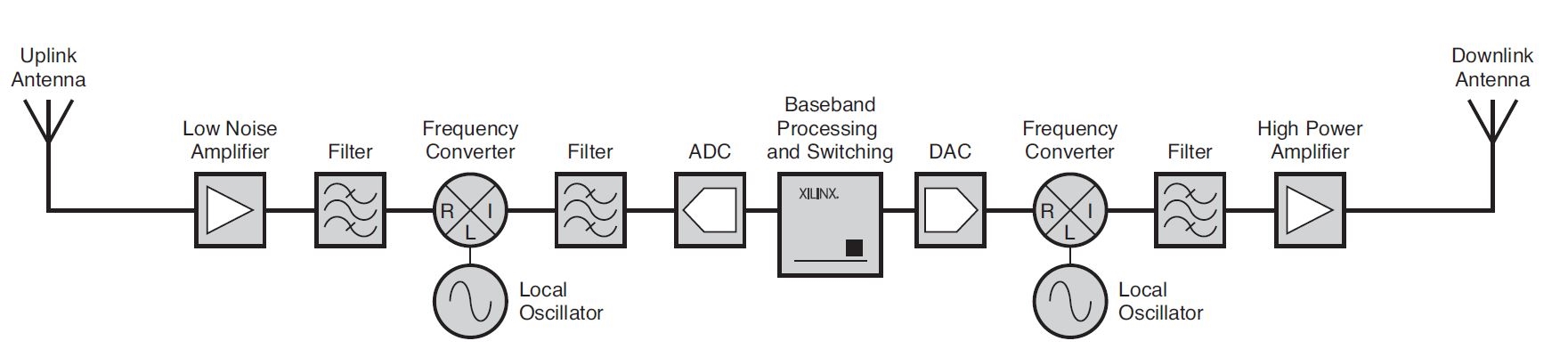

該款FPGA的板載處理能力便於衛星製造商為營運商提供具備數位波束成形功能的高彈性有效載荷。此外,由於FPGA具有可重組能力,再生DSP切片也能夠適配不同的載波標準和解調標準,因此充分發揮該款FPGA板載處理能力的多通道、高傳輸量電信有效載荷的原理(圖9)。

圖9 高傳輸量電信有效載荷原理圖

圖9 高傳輸量電信有效載荷原理圖

地球遙感觀測即時影片串流

為提供超越競爭對手的加值服務,地球觀測衛星的所有者希望能夠為他們的客戶提供4K和8K超高解析度的即時影片串流,進而實現新穎的遙感應用。傳統營運商和Space 2.0商業營運商將目標放在利潤豐厚的資料分析市場,他們需要為使用者提供下列主要服務:

・高解析度影片串流SAR和光學雷達(LiDAR)

・板載處理,即時監測和確認行動目標

・行動目標速度運算

・先進追蹤、情報、監控和偵察

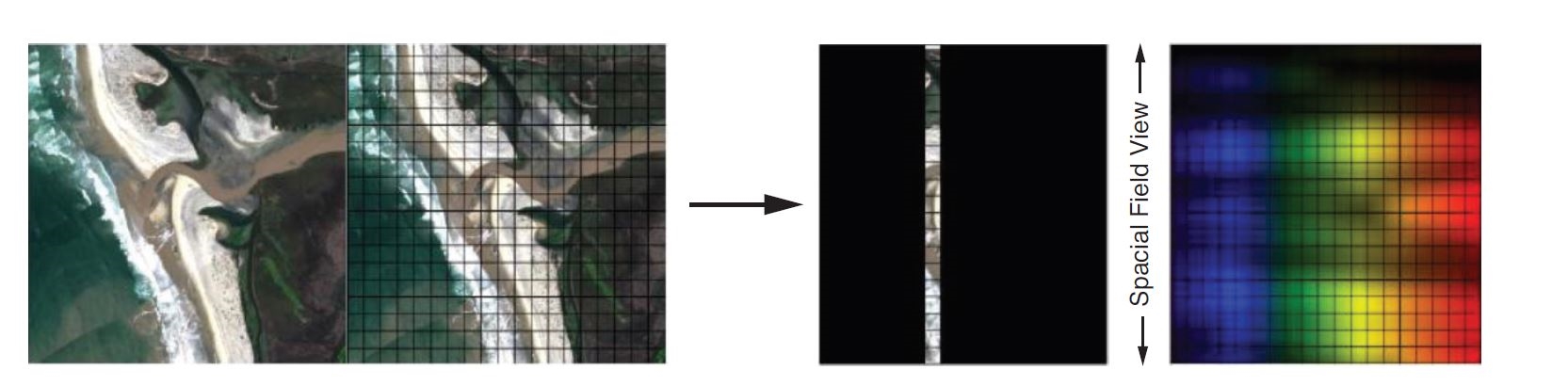

發展中國家希望借助可見光、近紅外線(Near-infrared, NIR)和短波紅外線(Short Wave InfraRed, SWIR)波段的超高空間解析度和頻譜解析度連續頻段(Contiguous-band)成像來解決社會需求。借助即時影片串流實現的高回訪率和高傳輸量光學效率是最大化SNR的需要,以便在陽光照度低的情況下開展環境監測和/或區分特定頻譜波長(如水面遙感)。如該款FPGA提供大I/O和記憶體頻寬,結合板載處理能力,實現未來的地球觀測應用(圖10)。至於運用該FPGA板載處理能力的高傳輸量地球觀測有效載荷的原理,則可參考圖11。

圖10 高光譜地球觀測成像

圖10 高光譜地球觀測成像

圖11 高傳輸量地球觀測有效載荷原理圖

圖11 高傳輸量地球觀測有效載荷原理圖

板載AI朝自主空間探索

營運機器人著陸器和漫遊車的機構希望交付新體驗,提升公眾參與度,並實現「親身體驗的科學」。未來的空間探索需要大幅提高板載處理能力,才能將超高解析度畫面傳回地球。

到其他行星的距離會導致嚴重的通訊延遲。因此,高效率的機器人系統運作需要高水準的自主化。著陸器和漫遊車必須管理本地環境條件,並且未來的機器人將使用AI進行探索、繪製和地形導航,以避開危險,拾取物體,採集和分析樣本。所有這些活動都將以直播形式傳回地球。

未來的機器人子系統必須大幅增強影像處理、自主導航、從感測器讀取遙測資料和控制致動器的能力。所有這些資訊必須進行即時處理,才能實現遠端空間探索。在未來,在校學生將能夠直接對漫遊車發出命令,實現「親身體驗的科學」。

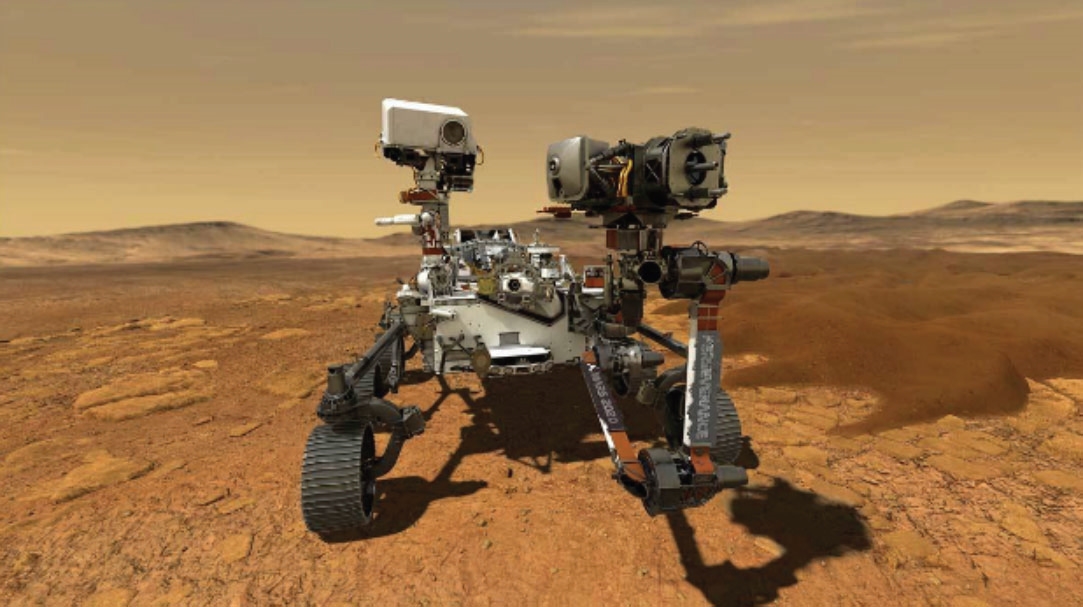

如賽靈思Virtex-4QV FPGA被美國航太總署勇氣號和機會號火星漫遊車用於探索火星地表;V5QV航太等級元件將用於MARS2020任務的離線處理(圖12);本文提及的FPGA則提供大I/O和記憶體頻寬及板載處理能力,賦能新一代遠端自主空間探索。

圖12 未來火星漫遊車

圖12 未來火星漫遊車

圖片來源:NASA

FPGA新設計拓展衛星應用

新UltraScale架構將FPGA功能延伸至空間應用,為I/O與記憶體頻寬、容量、性能和軌道可重組能力帶來飛躍發展。如本文提及的該款FPGA可為衛星產業提供數百Gbps的高傳輸量板載處理能力。透過根據使用者的即時需求優化和重新部署在軌有效載荷資源,有助於太空船營運商提供全新應用,如以超高解析度即時傳輸地球觀測遙感資料、天基網際網路、衛星機器間通訊、寬頻行動電信等。

前幾代FPGA以及許多廠商的航太等級FPGA受制於架構瓶頸,嚴重限制其在超高傳輸量板載處理方面的應用。而像RT Kintex UltraScale架構提供創新單晶片通訊、I/O與記憶體頻寬、DSP功能、時序、關鍵路徑和互聯,使用20nm技術為要求最嚴苛的衛星應用提供良好的ASIC等級系統性能。

至於輻射測試已證明該款FPGA適用於所有軌道應用和深空探測。-1M速度和溫度等等級的原型構建等級、QMLB等級和QMLY等級元件現已供貨,符合ECCN 9A515.e.1出口管制規定,可望為板載可重組處理帶來「大躍進」,實現新穎的超大頻寬衛星應用,開啟航太新時代。

(本文由賽靈思提供)