USB Type-C在為消費者帶來便利的同時,也為設計USB電纜及相容產品帶來挑戰。本文詳細說明USB 3.2合規性測試要求,並說明測試過程中的常見問題和解決方式。

USB 3.2電氣合規標準

低頻週期訊號參數

(承前文)如果測試系統已正確設置,連接的裝置將在開機後立即發送Polling.LFPS。借助現代測試自動化軟體,可以立即獲得測試結果,確定裝置是否達到合規性測試要求。

符合USB 3.2規範的裝置應符合以下USB 3.2低頻週期訊號參數:

- Vpp >=800mV <= 1.2V

- tPeriod >= 20ns <= 100ns

- tBurst >= 600ns <= 1.4 µs

- tRepeat >= 6µs <= 14 µs

- 上升/下降時間 <= 4ns

- 負載週期 >= 40% <= 60%

- AC共模電壓 <= 100mV

展頻時脈

展頻時脈(Spread Spectrum Clocking)是USB合規性之下的另一個強制性(Mandatory)量測項目。雖然製造商可以透過CP1獲得測量結果,但因部分供應商禁用了展頻時脈,預先選擇正確的供應商至關重要。

Gen 1眼圖與抖動量測

與其他測試模式相同,切換(Toggling)透過在Rx Pair上發送Ping.LFPS來完成。一旦到達眼圖和抖動測試模式,就可以使用CP0和CP1進行測量。需要注意的是,此測試通常在合規程序的尾聲進行。合規裝置的預期結果如下所述。

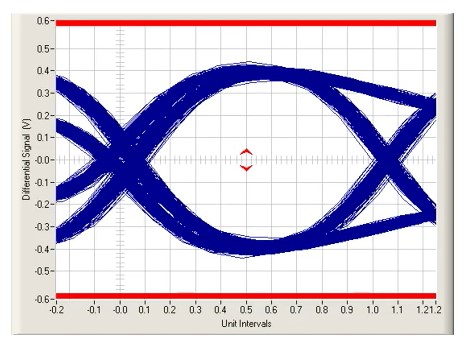

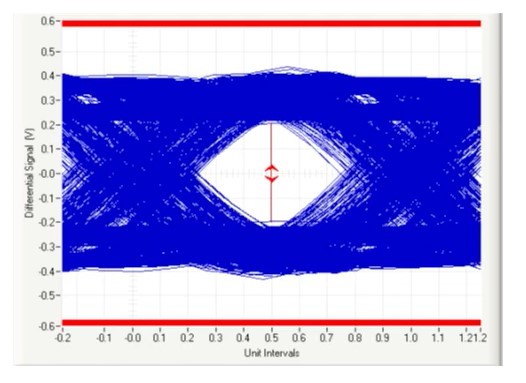

如果產生的眼圖,其頂層和底層不相碰,該裝置將被視為已通過合規性測試。與長通道(圖4)相比,短通道眼圖(圖5)通常具有更寬的眼圖。

圖4 (Gen 1)長通道傳眼(Long Channel Transmitted Eye):過渡眼

圖4 (Gen 1)長通道傳眼(Long Channel Transmitted Eye):過渡眼

圖5 (Gen 1)短通道傳輸眼(Short Channel Transmitted Eye):過渡眼

圖5 (Gen 1)短通道傳輸眼(Short Channel Transmitted Eye):過渡眼

Gen 1抖動和眼圖的合格要求如下:

- CTLE在製作眼圖時完成

- Tj at BER-12 <= 132ps with CP0 at TP1

- Dj <= 86ps with CP- at TP1

- Rj <= 3.27ps with CP1 at TP1(如今,Rj不再是合格要求,只是一個資訊指標)

對於長通道量測,USB-IF將透過RTP示波器提供適當的S參數。此外,長通道損耗也取決於USB連接器的類型以及所使用的上行或下行連接埠。

Gen 2眼圖與抖動量測

Gen 2的眼圖和抖動量測其實與Gen 1非常相似,只是部署了測試模式CP9和CP10。透過在Rx Pair上發送Ping.LFPS來完成測試模式之間的切換。

仔細觀察每次量測的邊緣,就能查出適當的眼睛寬度和高度(圖6、圖7)。

圖6 (Gen 2)長通道傳眼(Long Channel Transmitted Eye):過渡眼

圖6 (Gen 2)長通道傳眼(Long Channel Transmitted Eye):過渡眼

圖7 (Gen 2)短通道傳輸眼(Short Channel Transmitted Eye):過渡眼

圖7 (Gen 2)短通道傳輸眼(Short Channel Transmitted Eye):過渡眼

Gen 2抖動和眼圖的合格要求如下:

.與Gen 1不同,Gen 2需要在製作眼圖期間完成CTLE和DFE等化(Equalization)

.Tj at BER-12 <= 67.1ps with CP0 at TP1

.Dj <= 53ps with CP0 at TP1

.Rj <= 1ps with CP1 at TP1(與Gen 1相同,Rj不再是合格要求,只是一個資訊指標)

請注意,長通道量測與短通道端設置量測相同。唯一的區別是RTP示波器將USB-IF S參數嵌入至訊號中。除了具有固定(Captive)或繫留(Tethered)電纜的裝置外,Gen 1長通道始終使用相同的S參數。

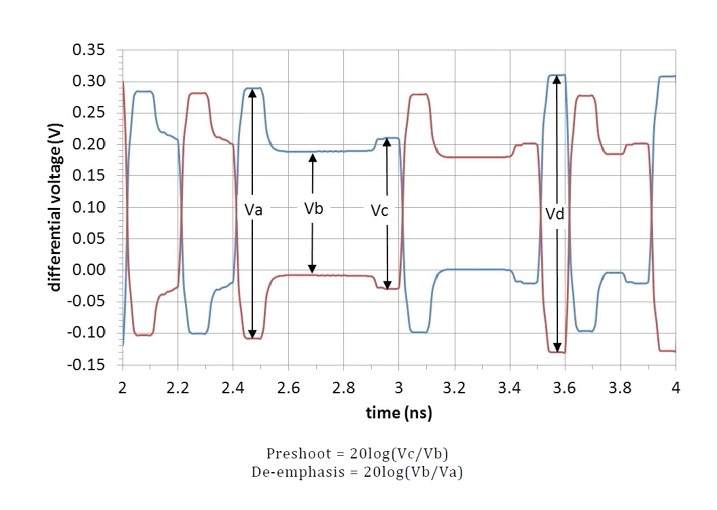

預拍攝(Pre-shoot)和預衰減(De-emphasis)(*僅限Gen 2)

USB Gen 2合規性在預加強(Pre-shoot)和預衰減(De-emphasis)方面還有一項額外的測試標準。此測試標準僅適用於Gen 2,並且需要測試模式CP13、CP14和CP15才能執行,由於不容易單靠觀察診斷測試結果,建議製造商在測試模式之間進行切換並觀察差分電壓如何變化。

圖8 USB Gen 2預加強和預衰減圖表

圖8 USB Gen 2預加強和預衰減圖表

USB 3.2 Tx/Rx強制性測試

USB 3.2發射器自動化解決方案具有一個RTP生成器,用於CPx之間的切換。RTP也將引導使用者完成設置和測試模式,最後產生報告。

對於Type C,在兩個方向上測試接收器非常重要,如果產品是DRD(Host & Device),則需要測試兩種模式。對於USB 3.2 Gen 1/2X2,必須測試所有資料通道(Data Lane)。此外,也需要記得使用正確的USB夾具、電纜和SMA電纜。

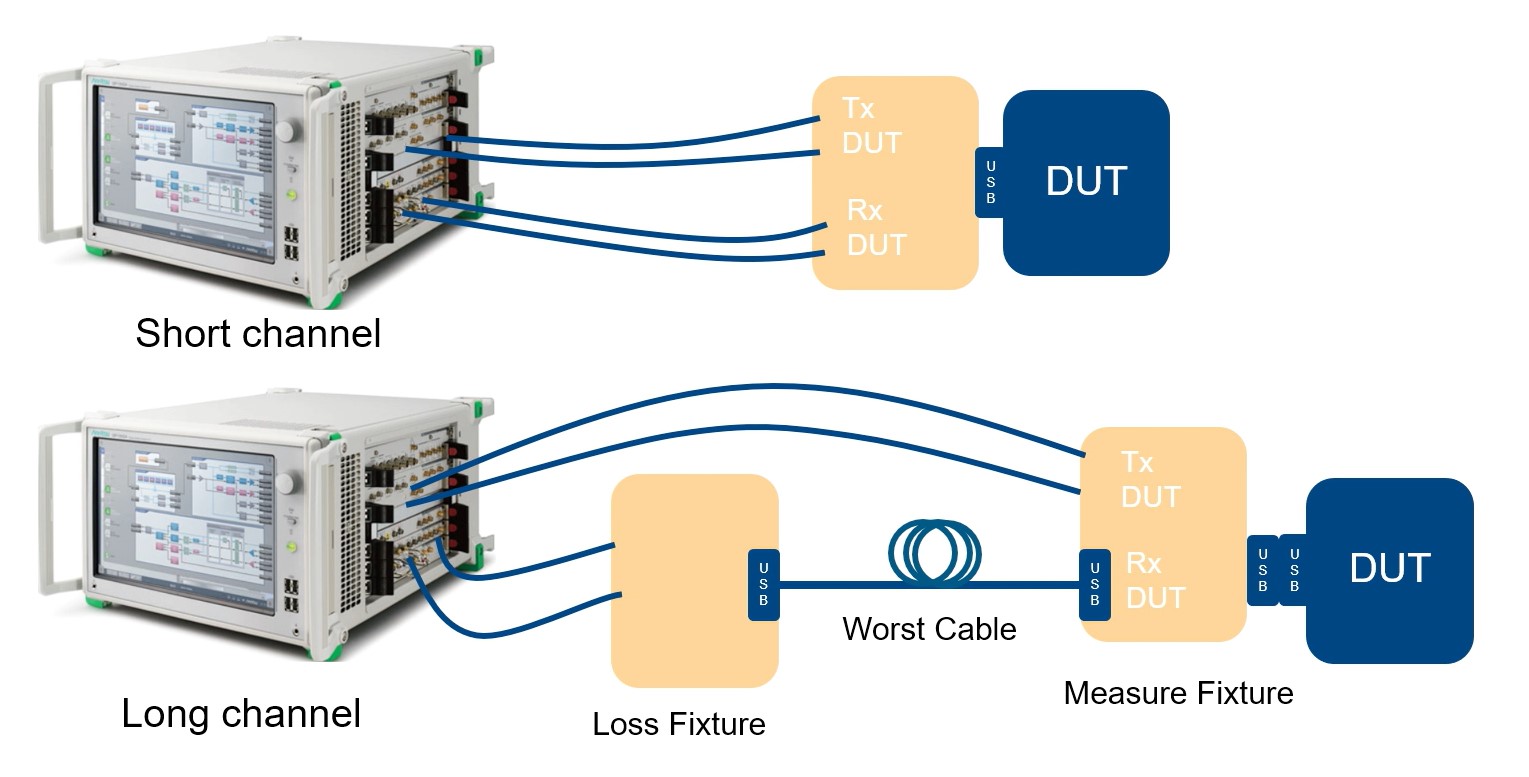

USB 3.2接收器測試可透過短通道和長通道進行。長通道取決於連接器的速度和類型,而模式生成器(PG)將向被測產品的Rx發送經過校準的合規性測試模式。這將包括:允許的最大抖動級別、Rj和Dj(Sj)、SSC(33KHz向下展頻5,000ppm)、最低電壓

首先,將被測產品置於迴環狀態(可由PG完成)。BERT將讀取被測產品在Tx端發回的錯誤訊息。根據USB 3.2規範,BERT應在10至12之間。如果DUT是Type-C,則應使用備用Rx路徑重複所有測試。

USB 3.2 Rx測試流程

校準

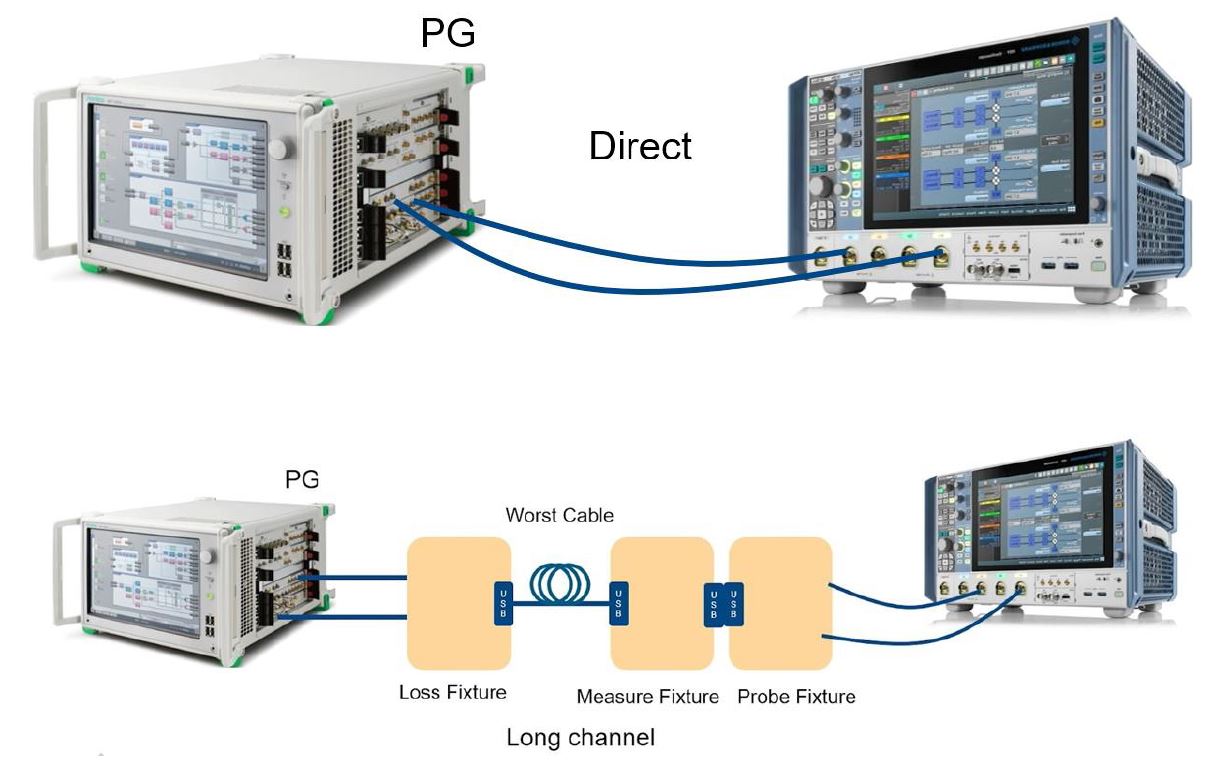

圖9 USB 3.2 Rx校準設置

圖9 USB 3.2 Rx校準設置

在進行USB 3.2接收器測試之前,必須校準傳送到DUT的模式(圖9)。長通道和短通道都需要校準,校準參數如下:

- 電壓擺動和預衰減(用於短通道和長通道)

- Rj、Sj和Tj

計算將透過SigTest在後台完成,此為漫長的過程,因此強烈建議採用自動化方案。即使是自動化校準,也需要四個小時的準備時間。手動校準將耗時數天,而且由於需要追蹤許多校準值,往往會導致大量錯誤。每次更換USB或SMA電纜時,都需要重新對設置進行校準,這點需要特別留意。

測試

圖10 USB 3.2 Rx測試設置

圖10 USB 3.2 Rx測試設置

校準完成後,將使用儲存在BERT中的值進行測試。合規性測試將在允許的最大Sj下進行。

與校準一樣,強烈建議將測試過程自動化。自動化解決方案會將被測產品置於所需的迴環模式,該過程對於手動操作來說極具挑戰性,需要長達數個工作日的時間,並且具有出錯風險。

雖然官方並未將其列入合規性要求之中,仍強烈建議測試人員進行接收器容忍度測試,以確定產品的振幅和抖動餘裕。校準大約需要四個小時,因此需要確保從一開始就使用正確的USB夾具、電纜和SMA電纜,以避免重做。

記得在產品處於DRD(主機和裝置)模式時測試兩種模式,並測試USB 3.2 Gen 1/2x2的所有資料通道。

USB3.2 Rx測試的常見問題及解方

迴環輸入失敗

每當產品無法進入迴環時,測試人員應先根據參考產品驗證設置是否準確。若確認設置正確,即可在迴環訓練期間藉由停用抖動或增加振幅,進行故障排除。選擇了不正確的通道而導致Type-C電纜無法進入迴環的情況並不少見,翻轉電纜或使用測試器夾具的跳線在CC線路上進行正確設定通常可以解決這個問題。

接收器容忍度測試失敗

當產品未能通過接收器容忍度測試時,PHY的等化器設定可在實作過程中,在重計時器(Re-timer)或中繼器(Re-driver)上進行調整。請注意,Tx上的高振幅可能導致Rx路徑上的串擾,進而導致Rx測試失敗。

不良的PCB設計

不良的PCB設計可能導致測試失敗,常見原因包括線路過長或不匹配。因此,建議製造商遵循PCB設計規則以避免類似情況發生。

測試實驗室協助節省測試成本

透過測試實驗室,業者可減少花費在USB 3.2合規性測試的時間與成本,例如GRL便提供全面的USB-IF 合規性服務,並配備所有必要的測試和除錯設備,可協助USB 3.2產品完成合規性測試。

(本文作者為GRL EMEA實驗室主管)

破解USB 3.2 Gen 1/2電氣合規挑戰(1)

破解USB 3.2 Gen 1/2電氣合規挑戰(2)