為了深入瞭解位元錯誤,得在時域和頻域仔細查看抖動和電源軌雜訊。比較TIE頻譜中的週期性抖動(PJ)頻率與電源漣波頻譜中的雜散,可快速又準確地找出由配電網路(PDN)引起的訊號完整性問題。

SI和PI對錯誤的影響

數位錯誤是由抖動和雜訊引起。雜訊是一個廣義的術語,泛指訊號振幅中的變化。抖動則是相對於資料速率時脈的位元轉換時序變化,即所謂的時間間隔錯誤。抖動是由相位雜訊和振幅雜訊到抖動的轉換所引起。雜訊到抖動的轉換導入了串擾、電磁干擾(EMI)和隨機雜訊等問題。

訊號完整性(SI)分析會著重於發射器、參考時脈、通道和接收器的效能,並以位元錯誤率(BER)來表示。電源完整性(PI)則著眼於PDN提供恆定電壓電源軌和低阻抗返回路徑的能力。SI和PI具有廣泛的相互依賴性。PDN會引起雜訊和抖動。電路設計和元件(晶片封裝、針腳、走線、過孔、連接器)會影響PDN的阻抗,進而影響電源供應的品質。

除錯SI問題始於眼圖

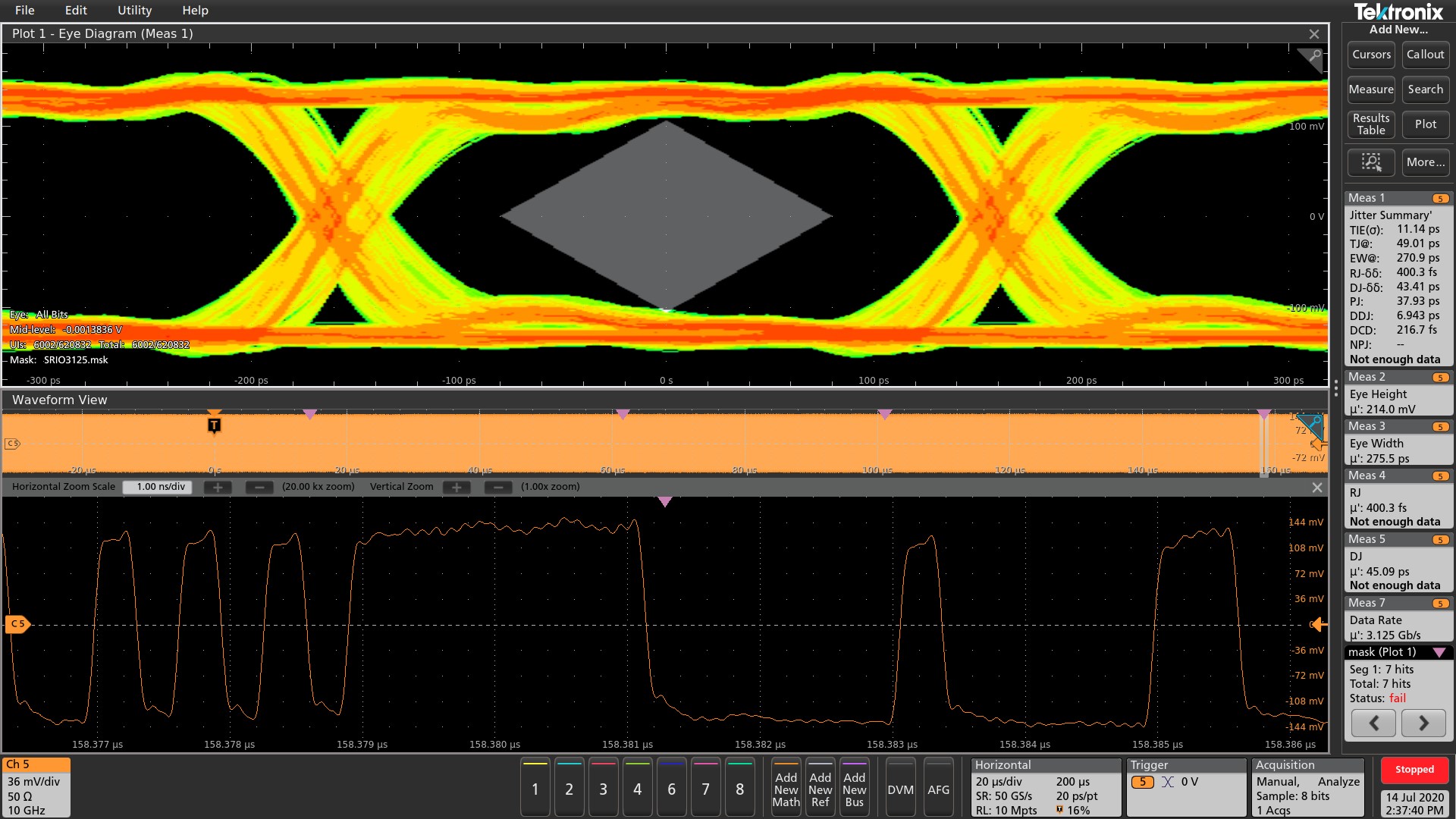

硬體除錯可以從眼圖分析開始。眼圖由相對於時脈的重疊波形組成,如圖1。交叉點的水平寬度表示抖動,而眼頂部和底部的垂直寬則表示雜訊。寬開口的眼應對應於低BER。若BER過高,則下一步是執行抖動分析。

圖1 眼圖含遮罩測試(上),以及對應的波形(下)。

圖1 眼圖含遮罩測試(上),以及對應的波形(下)。

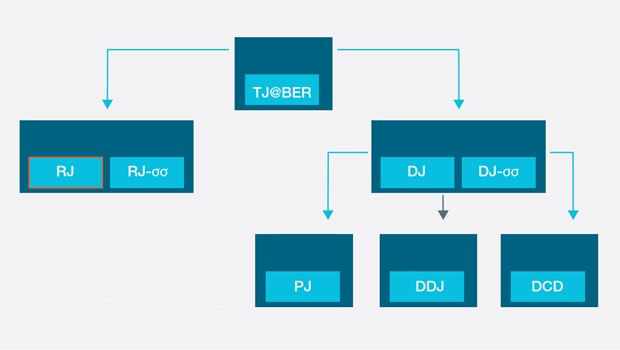

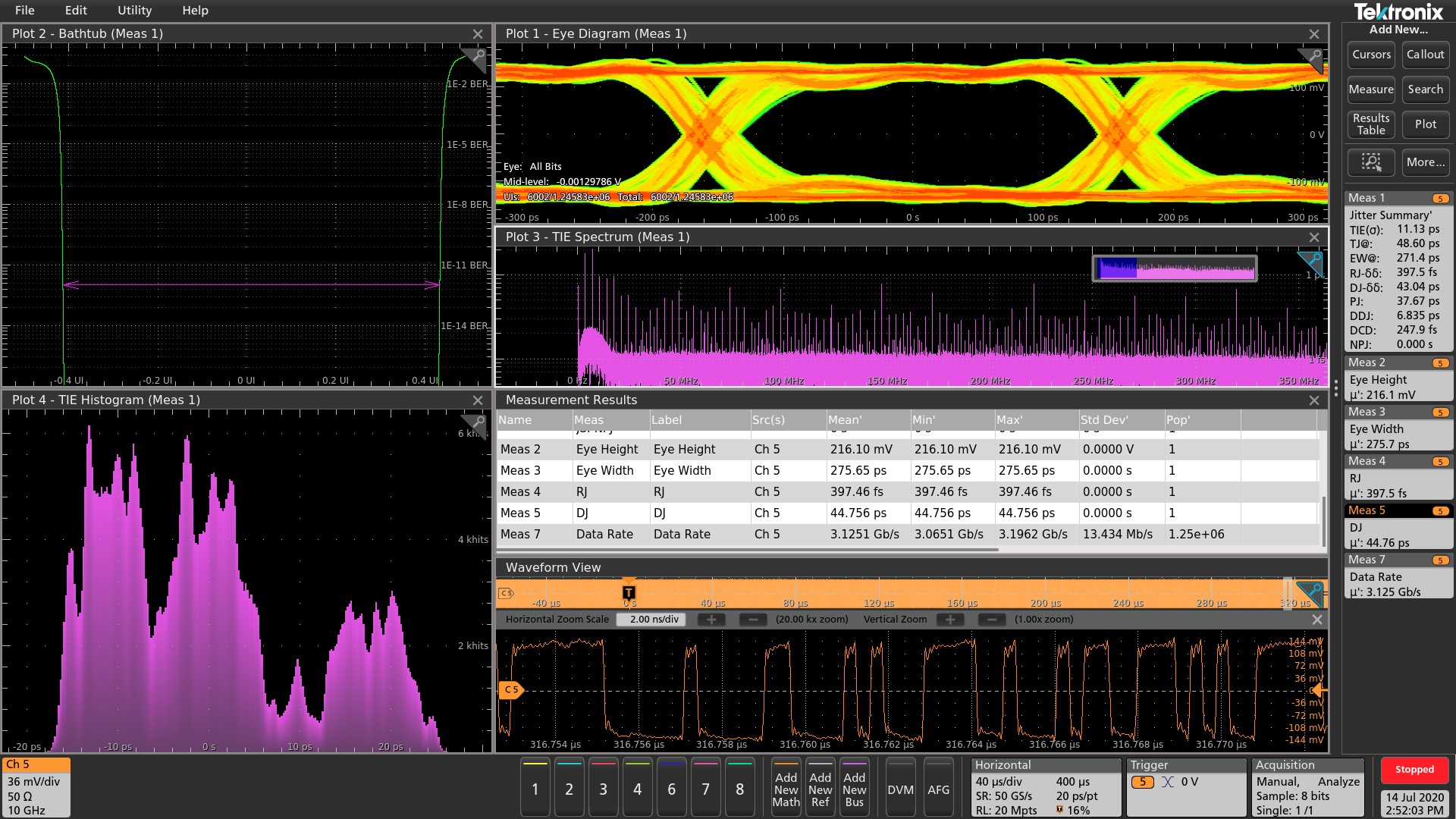

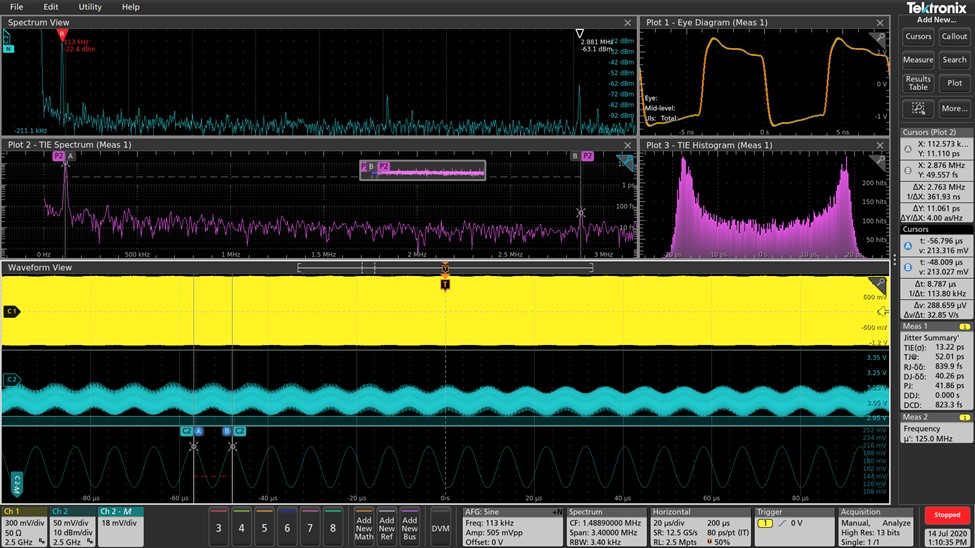

圖2將抖動的分解圖映射到其分量和子分量,圖3則顯示了「抖動摘要」量測值,包括浴缸曲線圖、眼圖、TIE頻譜和直方圖、抖動量測結果和波形。

圖2 抖動分解為其各個分量

圖2 抖動分解為其各個分量

圖3 抖動摘要螢幕截圖,從左上方順時針方向:浴缸曲線圖、眼圖、TIE頻譜、抖動分析結果、波形、TIE直方圖。

圖3 抖動摘要螢幕截圖,從左上方順時針方向:浴缸曲線圖、眼圖、TIE頻譜、抖動分析結果、波形、TIE直方圖。

抖動的分解始於將TIE分布分為其隨機和確定性分量隨機抖動(RJ)和確定性抖動(DJ)。DJ進一步分為與資料中位元序列相關的抖動DDJ(資料相關抖動),以及與之無關的抖動,例如PJ。

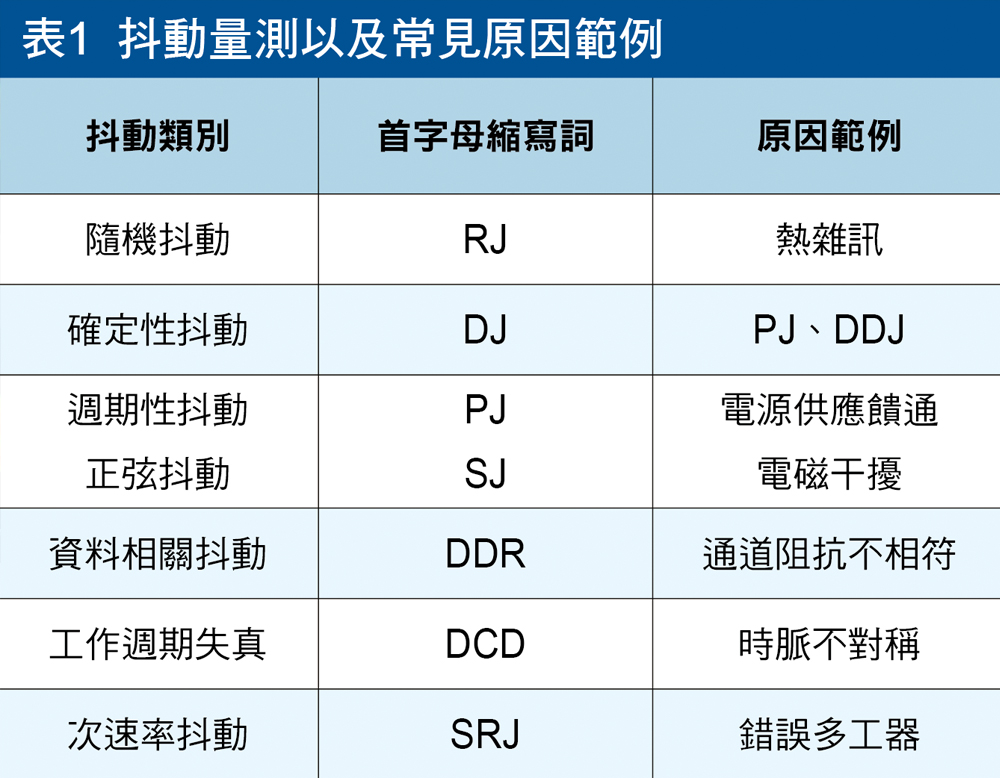

眼圖上的廣泛交叉表示RJ的存在。看起來由許多幾乎不同的線組成的眼睛表示存在DDJ,可能是由於訊號路徑中的阻抗不相符所致。此時需要更詳細的量測才能確定可以指示硬體錯誤的抖動類型:TIE、RJ、DJ、DDJ、PJ、總抖動(TJ)、眼高度(EH)、眼寬度(EW)、Eye High和Eye Low。表1列出了不同類型的抖動和一些原因。電源軌漣波是PJ有時甚至是RJ的常見原因。

抖動和配電網路

PDN的工作是維持恆定的電壓並為系統中的元件提供足夠的電流,PDN會影響每個元素的效能,不論是主動或被動。PDN包括整個系統,不僅包括直流/直流轉換器和內部晶片配電,還包括每個互連、走線、過孔、連接器、電容器、封裝、針腳和球柵。

漣波對隨機和週期性抖動的影響

電源軌雜訊通常稱為漣波,一般約為幾毫伏特。若要在GHz頻率下準確量測電源軌上的mV雜訊,就需要具有高直流阻抗的高頻寬探棒,該探棒可在高頻下充當50Ω傳輸線使用。電源導軌探棒是專為此目的而設計。

切換式電源供應器透過在低功耗導通和關斷狀態之間連續切換,來調節電源軌和返回路徑(也稱為「接地」)之間的電壓。不過,驅動切換元件的脈衝會引起「切換雜訊」並導致PJ。

切換會以固定頻率(應記錄在直流/直流轉換器的產品規格表)發生。若圖4左上方的漣波頻譜和緊挨其下的TIE頻譜在切換頻率或切換頻率的諧波處均有雜散,即可找出來源並解決設計問題。請注意,圖4中白色標記處出現大型的重合雜散。TIE頻譜右側的TIE直方圖在一個頻率上具有正弦抖動分布(馬蹄形)PJ。

圖4 Spectrum View左上方的電源軌漣波,以及其下方的TIE頻譜,以及訊號和電源軌波形及TIE直方圖。

圖4 Spectrum View左上方的電源軌漣波,以及其下方的TIE頻譜,以及訊號和電源軌波形及TIE直方圖。

電源供應器會導入隨機雜訊,進而導致RJ。電源軌隨機雜訊顯示為圖4左上方Spectrum View圖的基準雜訊。RJ由TIE頻譜的基準雜訊計算得出。在此範例中,由於電源漣波引起的隨機雜訊非常低,RJ很小,約為0.84ps。

PJ和接地反彈

在邏輯轉換期間,發射器和接收器從PDN輸出或輸入電流。當多個訊號同時在兩個位準之間切換時,可從電源導軌或接地平面上沉積或去除大量電荷。短期導入電荷密度會改變導體兩端共同接地的電壓。所產生的電壓變化稱為接地反彈或相當於同時切換雜訊(SSN)。

在繼續說明之前,應該釐清兩件事。首先,「接地」是指返回路徑的所需公共參考電壓,通常將其定義為0V。第二,「同時」是指元件在其上升或下降時間重疊在時間間隔內進行輸出或輸入電荷。

SSN在時域中看起來是隨機發生,但在頻域中卻不是。資料訊號由許多頻率分量組成(基頻或Nyquist頻率),可能多達兩個高次諧波,再加上來自連續相同位元的次諧波。這些頻率中的任何一個頻率都可能發生同時切換。因此,SSN是具有許多可能引起PJ的低振幅雜散的週期性雜訊。

為了確認PJ是由SSN引起,請將圖5左上方的電源軌頻譜與正下方的TIE頻譜進行比較。在兩個頻譜中以相同頻率出現的高振幅雜散指示SSN對PJ影響很大。

圖5 (a)電源軌漣波頻譜和(b)TIE/抖動頻譜

圖5 (a)電源軌漣波頻譜和(b)TIE/抖動頻譜

結合抖動/電源分析解決雜訊問題

訊號完整性和電源完整性是一個回饋迴路。網路中的每個元素,每條走線、過孔、連接器、針腳、封裝等都會影響PDN阻抗和每個通道的阻抗,且每個主動式元件都會改變電源軌和接地平面的電壓。

眼圖可以告訴讀者許多有關訊號完整性的資訊,但不太能識別出特定問題。對TIE分布的分析可將抖動分解為一些分量,這些分量將會提供問題所在的線索。高RJ通常意謂著時脈嘈雜,但也可能表示電源供應器產生了隨機雜訊。

PJ可能指示時脈錯誤、電源切換雜訊或接地反彈/SSN。將電源軌漣波頻譜與TIE頻譜進行比較,就能以兩個步驟找出問題。若TIE頻譜中的雜散在電源軌頻譜中沒有任何相應的雜散,即表示其為時脈;兩個頻譜中相同頻率的一個或兩個雜散表示其電源切換雜訊;而兩個頻譜共有的大量雜散則表示其SSN。在這些情況下,將抖動和電源分析結合起來將可隔離很難解決的問題。

訊號完整性和電源完整性通常被認為是不同的學科,但是本文發現,若想要找到與高抖動相關的問題,則需要同時瞭解兩者的來龍去脈。

(本文作者任職於Tektronix)