過去幾年,射頻(RF)技術快速進步,並因此帶動了大量的新型態無線應用。在這些應用領域中,如藍牙(Bluetooth)、無線區域網路(WLAN)802.11b以及無線電話等,大部分都是採用與微波爐相同,也就是2.4GHz免使用執照的超高頻(UHF)頻段。但由於2.4GHz頻段的流量相當龐大,加上與其相關聯的共存爭議,因而使得工業、科學、醫療(ISM)UHF頻段在採用頻率較低的868 MHz與433MHz的歐洲地區,以及在採用902 MHz與928MHz頻率的美國地區較受青睞。

UHF頻段需高效能低錯誤收發器

然而不同於2.4GHz頻段,較低的UHF頻段並沒有一個世界共通的標準,這也意味著生產廠商的系統必須要適應每個地區的標準。不過由於可在433 M到960MHz的ISM頻段彈性切換的收發器問世,使得這種負擔獲得相當的紓解。

然而,很不幸的,若只是簡單的切換至這些較低的UHF頻段,並不能將干擾(Interference)與共存(Co-existence)的問題完全解決。而可能正如所預期的,有許多傳統的系統早已經在這些頻段中運作了。在無線系統中,假如干擾與所需要的訊號相互碰撞,資料就會產生錯誤,進而造成接收器上的訊號雜訊比(SNR)不足。想要解決這個問題,傳統的方法是使用某些類型的誤差偵測(Error-detection)技術,例如循環冗餘核對(CRC),來偵測一定程度內的誤差,並且促使錯誤的封包再重新進行傳送,而這個程序通常被稱為自動重傳要求(ARQ)。但是對於即時性的應用而言,成本將會因為大量的延遲以及效能的降低而增加。

這個重傳錯誤封包的需求對於低產生率的系統而言,並不是特別繁重的工作。舉例來說,像是每隔幾分鐘就會傳送一連串資料的遠端感測器。但是對於一些像是無線音訊或是視訊傳送的應用領域而言,這點確實已經成為一個難題,因為這些應用領域具有較高的資料速率,而ARQ所造成的延遲很可能是無法被接受的。另外對於必須在具有雜訊的環境中維持產生率,同時又不需要很多重新傳送的工業製程控制以及遙測系統而言,這也對它們帶來了難題。而所導致的相對較長傳送時間,也會使系統的整體功率損耗相對增加。

面對這樣的困境,一個較為有效的解決方案就是使用前向錯誤校正(FEC)技術,利用此技術可以充分的對大量的位元進行偵測並校正錯誤,以便對部分的封包遺失予以補救並確保服務的品質。因此應用像是低成本卻有力的處理器,就可以用來執行需要每秒執行百萬指令(MIPS)的密集錯誤校正技術--例如採用位元雜湊(Bit-scrambling)以及插入法(Interleaving)來進行編碼的迴旋編碼(Convolutional Coding)等,藉此提供具有低於10–6傳送錯誤率,能夠達到100kbit/s以上的資料速率。

搭配ISM頻段收發器IC使用時,由於其具有數百公尺遠的可視典型範圍,因而為設計工程師提供了一個穩固的解決方案,使其能夠取代現有的有線解決方案,但又不用犧牲服務品質。前述的收發器具有400MIPS以及800MMACS(每秒百萬級乘法累加)的能力,所以它也能夠調整通訊協定,使其支援不同的無線設定與拓撲,其中包括了點對點(Point-to-point)、多點(Multi-point)以及廣播,還有複雜的加密與信號源編碼解碼演算法,如MotionJPEG(MJPEG)。

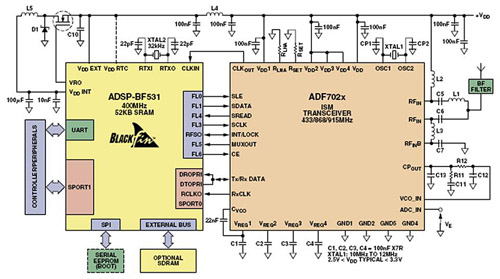

圖1所示為利用ISM頻段收發器以及與其搭配的控制器所製作的無線數位數據機詳細電路圖。兩個主要的晶片共用同樣的電源供應電壓(2.3V<V<3.6V),並且直接相互連接,使用數位I/O旗標來做為控制用途,又使用其中一個同步序列埠(SPORT0)來做為傳送/接收用途。

|

| 圖1 數據機的電路圖 |

一般來說,資料若不是透過通用非同步收發傳輸器(UART)以非同步方式傳送至數據機上或是由數據機上接收過來,不然就是利用其餘的SPORT以同步方式來傳送。

收發器功能多樣

以現今利用0.25微米CMOS技術所製作的完全獨立無線電收發器為例,能夠在433MHz以及868MHz的歐洲地區ISM頻段(ETSI EN 300 220-1標準),以及902M~928MHz的北美地區頻段(FCC Part 15規章)下運作。此元件只需要少數的外部元件,並且具有高度的彈性,這些特點讓使用者得以針對特定的應用領域來對該元件進行設定。舉例來說,可以在如FSK、GFSK、ASK及OOK等不同的調變結構中做選擇。使用者也可以在靈敏度與選擇性之間取得平衡,尤其對於線性度需求比較不高的系統,這是一個很有用的方法。目前問世產品的資料傳輸速率為200kbit/s,也有產品可達更高的384kbit/s資料速率。

大多數近期的ISM頻段收發器都採用了分數N型(Fractional-N)鎖相迴路(PLL)合成器,使其可以使用在433MHz上的通道,擁有優於1kHz的解析度,以及介於868MHz與928MHz之間的任意通道。由於具有如此的頻率靈活性,使得無線電收發器可以使用於跳頻(Frequency-hopping)系統,如同US FCC Part 15規章中所規範上,但是當輸出功率低於-1.5dBm時,也可能在北美地區頻段中以單一通道來運作。

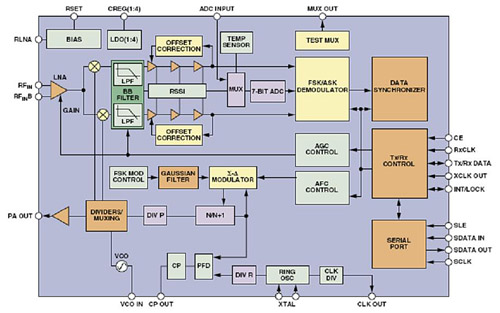

高解析度的分數N型合成器也是新穎的自動頻率控制(AFC)迴路組成元件中的一分子,可用來對進入頻率之誤差加以補償,並且允許使用具有較低容錯值、較便宜的晶體。圖2中所示為近期問世無線電收發器產品的方塊圖。要決定PLL迴路濾波器的元件,可以使用模擬軟體來作為協助,相關軟體可以在業者的網站上取得。

|

| 圖2 收發器的功能方塊圖 |

利用處理器執行前向錯誤校正

在數位行動電話系統中,使用高效能的處理器來與無線電搭配,對於想要符合低成本的數位化數據機而言,乍看之下雖然不恰當,但卻是常見的情況。然而要以每秒數百個千位元(kb)的速率來執行FEC的運作,就需要運算密集數位化訊號處理能力。舉例來說,當一組標準的8051或是以ARM為基礎的微控制器,可以適當的處理使用者介面、通訊協定堆疊、RF收發器的監控以及電源定序(Power Sequencing)等,也就不須要具備FEC結構中所要求的運算馬力(Horsepower)。除了執行控制功能外,處理器所具有的運算能力以及即時處理能力可以提升有效的通道資料速率、減少通訊延遲、對於訊號傳送之變動加以補償,以維持連結的品質並確保通訊的安全性。

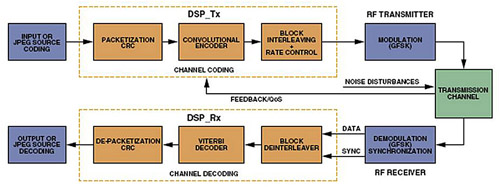

圖3所示為透過傳送通道來執行的各種不同功能,其中包括了控制傳送(Tx)與接收(Rx)運作的處理功能。當處理器被安置在發射器端,用以掌控資料速率的控制以及資料的分割時,資料將會以準恆定(Quasi-constant)的速率,採用封包形式傳送。資料封包會在它們調變為載波頻率之前被加以處理,以便用於FEC上。這點會藉由加入多餘的位元來達成,而這些多餘的位元乃是接收器進行偵測與校正錯誤之用。當然,這些被加入到送入封包中的位元,會對所需頻寬增加一定量的資訊位元速率。

|

| 圖3 訊號處理功能 |

在可應用於FEC的諸多不同方法中,迴旋編碼除了比較容易執行外,還能夠對於通道上的高斯雜訊(Gaussian Noise)干擾提供較佳的防護,並且有助於符合最低的漢明距離(Hamming-distance)準則。迴旋編碼器是一部有限狀態機(Finite State-machine),其中包含了L階位移暫存器(L-stage Shift Register)、N模數2加法器(N Modulo-2 Adders)以及多工器(Multiplexer),以便將輸出轉換為串聯位元串流。介於位移器輸出端與加法器輸入端之間的連結將會決定多項式碼(Polynomial Code)。處理器的核心只須使用兩組特別的可用指令,就能夠極有效率的執行所有工作。

在傳送通道的另一端,解碼器區塊將會執行Viterbi演算法(Hard-input/Hard-output),且為了要達到最大可能性的解碼,Viterbi解碼器會將所有可能的編碼序列與接收到的編碼向量相互比對。在所有編碼序列中,與所接收序列之間的漢明距離最短者為最佳。對於具有限制長度K=L+1of7,像是1/2,7,371,247的編碼,解碼器可以修正高達六組連串的錯誤位元。在這類型的無線應用領域中,依據系統的需要,從5到9的限制長度必須要能夠被處理器所支援。

然而,即使是具有限制長度9的迴旋編碼,也無法在較長的時間區段中避免突然出現的雜訊去撞擊到所要傳送的封包。因此採用以時間分集(Temporal Diversity)為基礎的互補保護技術是有必要的。時間分集就是將位元或標記分散於時間區段中,藉以在路徑多重、時強時弱(Fading)以及雜訊突現的情況下,改善編碼通訊系統的性能。也因此可以降低大量連續的位元遭到破壞的機率。利用雜湊與簡單的區塊插入功能就可以達到這個目的,而不須使用更為複雜的校正編碼,如Reed-Solomon。而相關處理器所具有的兩組特別向量指令將會很有幫助,一組用來計算Viterbi Trellis Butterflies,而另一組則用來對路徑搜尋、回溯運作時所需的資料進行重建。

接著,經過編碼的資料會被傳送至ISM頻段發射器區塊,在這裡會進行額外的濾波以及高斯頻移鍵控GFSK調變。GFSK調變具有可以降低占用光譜頻寬(Occupied Spectral Bandwidth)的優點,這在搜尋能夠符合歐洲地區的868MHz頻段中相鄰通道時,是很有用的功能。

在接收器端的部分,收發器內部的前文匹配(Preamble-matching)電路對於執行極重要的封包同步化作業是很有幫助的。這項硬體功能夠辨識12、16、20或24位元長度的可編程同步字串,或者是封包前文,而不需要處理器核心的介入。當有效的前文匹配出現時,該電路就會對收發器的INT/LOCK接腳進行宣告,以便將新封包開端的訊號送到序列埠(RFS0),並觸發Viterbi解碼器。

這個獨特的電路在某種程度上具有少許的錯誤容忍能力,它甚至可以容許高達三組錯誤位元的有效匹配。如此可以降低封包因為前文遺漏所造成之遺失的數量,因為前文不會被編碼,也因此而不會受到保護。想要更進一步的降低前文遺漏,可以在接收器上使用處理器的32位元計時器來作為看守裝置,假如INT/LOCK訊號在數個標記之後仍然沒有出現,該裝置就會在RFS0上產生出預期的脈衝。相較於完全使用軟體分析與追蹤來執行的情況而言,以硬體機構來回復封包同步標記的方式,可節省大量的處理器MIPS。

處理器攜手收發器提供穩固無線資料傳輸

如同前述,有效率的無線數位視訊傳送須要具備能承受通道失效的穩固性。對於使用以靈敏可靠的處理器為基礎的無線數據機應用而言,視訊編解碼器(Video Codecs)算是絕佳的候選對象。假設ISM無線通道頻寬有所限制,那麼為了要達到所需要的畫面速率(Frame Rate)以及特定影像尺寸的品質,同時又不能有太多的延遲,就必須要有相對較高的影像/視訊壓縮比率。不幸的是,Motion JPEG以及其他的視訊編解碼器,都需要極低的傳送錯誤率,通常都是10–6,這是因為訊號源編碼處理程序會將大部分的多餘資訊予以移除。對於某些有效率的一致性編碼器(Entropy Coders),例如Huffman而言,這點會特別重要,因為單一個錯誤位元就會使得原始資料不可能被解碼。在無線電上要具有低於10–6的位元錯誤率(BER),是很嚴苛的需求,但這可藉由使用如前所述的通道編碼結構來加以達成。

不過,極低的BER值並不能確保所有的資料封包都能正確的被一致性解碼(Entropy-decoded)。假如在封包中有太多重要的位元發生錯誤,若想要改善影像的品質,就必須要提供某些可以將影像的一部分加以隱蔽的機制。為達成這個目的,每一個封包都會被加以分割,並且分別予以一致性編碼。當錯誤的分割或是區塊被偵測到之後,其內容將會被丟棄掉。依據所遺失的資訊,在相對應的影像區塊之離散餘弦轉換(DCT)中,其dc以及最開頭的兩組ac係數,將會藉由鄰近區塊的係數來加以估算。原本是被設計來去除DCT區塊效應(Blocking Artifact)的最後低通(Low-pass)2D 3×3去區塊效應濾波器(De-blocking Filter)階段,會協助將最後所產生的變形平滑化。

若是處理器擁有強大的能力,就可以處理MJPEG編碼或解碼以及通道FEC的處理程序。此外,毋須外接記憶體就可以使畫面尺寸達到具有4:2:2視訊格式的QCIF(176×144)。若是願意負擔外接SDRAM的成本,就可擁有更大畫面,而SDRAM同時也可用來儲存壓縮過的視訊。目前已面市的低成本處理器尚可相容於其他低成本CMOS影像感測器或是TFT顯示器,經由其並聯周邊介面(Parallel Peripheral Interface)來直接連結。標準的低成本、低電源PCM音訊編解碼器可以連結至可用的序列埠SPORT1上,以便支援話語或是音訊的數位化傳送。或者處理器可以藉由執行類似於FR-GSM(13kbit/s)之類的軟體編解碼器,來提供具有適度延遲的話語編碼與解碼。

以200kbit/s的原始資料速率,有可能達到在ISM上以大約每秒四個QCIF(4:2:2)彩色畫面之速率來進行MJPEG傳送的基準線,同時還有20kbit/s留做語音之用。這對於簡單的低成本消費性裝置來說是可以接受的,像是嬰兒視訊監視器(Video Baby Monitors)、大門視訊對講機(Video Door Phones)或是無線式家庭安全攝影機(Wireless Home-security Cameras)等。這類應用領域的物料成本(BOM)大約會在七十五美元的範圍內;其中2.5吋LCD TFT顯示器更占成本最大宗。

總而言之,透過ISM頻段收發器與處理器相互結合而成的獨特組合,除了成本以外,同樣展現無線電連結性能,並且可以應用在不同的ISM數位無線傳輸系統上。隨著RF收發器家族的未來成員以及相容於TCP/IP的新數位訊號處理器(DSP)出現以後,加上伴隨而生額外的通道與訊號源編碼的軟體模組,可預期的是這個通訊模型將會有更進一步的改善。

(本文作者任職於ADI)