根據In-Stat的研究,數位電視直接廣播衛星(DBS)接收機的總數已在2006年達到七千五百萬台。儘管此市場在北美地區已進入成熟階段,但中國大陸首顆DBS衛星的發射,以及印度商用數位衛星電視服務的啟動,仍將引爆另一波成長熱潮,這是因為DBS提供開發中國家的電視廣播公司一種低成本的傳輸媒介。

DBS系統包含兩個主要的訊號處理次系統,分別是低雜訊(LNB)降頻器和DBS電視接收機。LNB降頻器位於衛星碟型天線基座,負責把衛星訊號頻譜從C、Ku或Ka等波段降頻為L波段0.9G~2.2GHz。DBS電視接收機則在機上盒內部,負責把訊號降為基頻和執行訊號處理功能,例如解調、MPEG解碼、顯示處理和類比音訊/視訊編碼NTSC/PAL。

DBS接收機共有四個功能方塊,分別為射頻調諧器、QPSK解調器/通道解碼器、主機處理器和LNB電源供應控制器。射頻調諧器把訊號從L波段降頻至基頻;QPSK解調器/通道解碼器把位元串流還原;主機處理器負責MPEG資料串流解碼,然後產生視訊和音訊輸出訊號給電視機;LNB電源供應控制器則會產生十三/十八伏特直流電源,並透過射頻同軸纜線提供給屋頂的LNB模組。接收機還會把一個交流控制訊號加到該直流電源,用來選擇所要的LNB極化方向。

過去十年來,DBS接收機的射頻調諧器已放棄原先的高中頻雙轉換架構,轉而採用直接轉換零中頻(ZIF)架構,市場最近也出現一款單石互補式金屬氧化物半導體(CMOS)低中頻接收機。DBS接收機有各種不同的射頻調諧器架構,它們之間存在許多重要差異,會對設計人員與最終系統造成影響。

高中頻雙轉換架構耗電且價昂

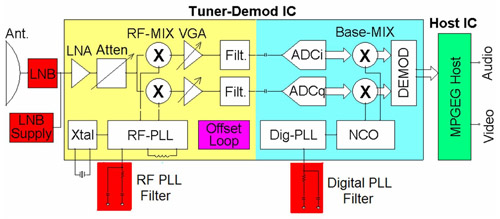

市場最早出現的衛星電視調諧器晶片是採用圖1所示的高中頻雙轉換架構,它擁有良好的鏡像拒斥效能。高中頻雙轉換架構使用外接式中頻表面聲波(IF SAW)濾波器做為電路級之間的濾波器,以便降低調諧器晶片所須達到的鏡像拒斥要求。然而這些超外差(Superheterodyne)調諧器卻需要複雜的兩級式混波程序:調諧器先把訊號從L波段降至高中頻例如480MHz,再透過第二級混波電路把訊號降至基頻。高中頻雙轉換架構還會消耗較多電力,因為外部電路必須使用很高的中頻頻率;另外,這些外部元件也會增加產品的用料成本。

|

| 圖1 高中頻DBS接收機架構 |

直接轉換易產生直流偏移

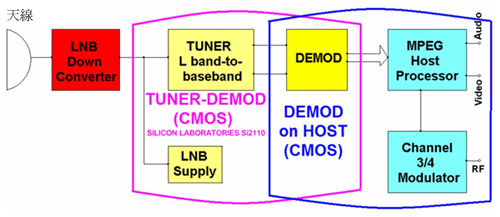

半導體製程和設計的進步促成直接轉換DBS調諧器誕生,它僅需一次混波就能將射頻訊號從L波段直接降至基頻(圖2)。直接轉換接收機並沒有鏡像拒斥的問題,因為鏡像頻率也是所要的目標訊號。它還能省下晶片外接表面聲波濾波器、第二組中頻混波器和高中頻增益級電路,這可簡化調諧器架構,進而縮小晶片面積、降低耗電、以及減少外部零件數目和總系統成本。

|

| 圖2 零中頻DBS接收機架構 |

直接轉換也有一些缺點,例如I和Q通道之間可能因為三種原因出現直流偏移,分別是元件不匹配、本地振盪器(LO)訊號洩漏至射頻輸入端、以及射頻訊號洩漏至混波器的本地振盪器輸入端。直流偏移可能導致訊號路徑的放大級電路飽和,故應加以避免。GSM之類的時域雙工(TDD)通訊系統可於通訊頻道關閉時測量和消除直流偏移,然而數位衛星電視卻須持續不斷傳輸訊號,所以只能利用迴路頻寬很小的直流偏移伺服迴路(DC Offset Servo Loop)減少直流偏移。窄頻寬確保偏移消除迴路只會略為影響訊號品質,而且還能透過解調器的前向錯誤更正(FEC)電路加以修復,但這種窄頻寬伺服迴路需要很大的交流耦合電容,這類電容通常無法整合至晶片。

直接轉換調諧器的另一缺點是訊號路徑元件的1/f雜訊可能造成調諧器的雜訊指數(Noise Figure)大幅下降,因為1/f雜訊會與零中頻位置的目標(複數)訊號頻譜重疊。由於雙極電晶體的1/f雜訊遠小於MOS電晶體,大多數的零中頻DBS調諧器目前都是採用雙極技術。廠商曾數次試圖利用CMOS製程設計直接轉換DBS調諧器,當時多半選擇使用被動混波器,因為它的訊號路徑不會用到任何主動電晶體,所以1/f雜訊會變得很小。然而被動混波器卻會出現轉換損耗(Conversion Loss),使得基頻電路雜訊對接收機的整體雜訊效能造成不利影響。

半導體製程選擇影響系統功能分割

調諧器的後面是解調器,它是一種含有大量數位電路的元件,包括將零中頻I和Q訊號數位化的類比數位轉換器前端,CMOS製程可以減少解調器的晶片面積和耗電。接收機的第三個功能方塊是MPEG主機處理器,這顆大型系統單晶片很適合採用130、90或65奈米等先進CMOS製程。

採用成熟雙極製程和0.6~0.2微米微影技術的獨立式調諧器不但極具成本競爭力,還提供很高的元件轉移頻率(fT=25G~50GHz),可以設計數個GHz的調諧器。然而廠商雖能利用先進BiCMOS製程開發單晶片調諧器與解調器,這類元件的成本卻很高,因為它需要昂貴的多光罩製程來處理數位電路密集的CMOS部分。

系統級封裝(System-in-package, SiP)是較可行的整合方法,它會把雙極調諧器、CMOS解調器和MPEG處理器整合至單一封裝。系統級封裝的主要優點是上市時程較快,因為現有的調諧器和解調器晶粒都可以重複使用。它的主要缺點是封裝成本較高、功耗散逸很複雜、還有打線接合(Bondwire)造成的寄生參數耦合問題。

另一種系統分割方式是利用雙極或BiCMOS製程設計獨立的射頻調諧器晶片,再把解調器和MPEG整合至另一顆CMOS元件,這種做法又稱為「主機與解調器整合法」(Demod-on-host)(圖3)。這種分割方式就系統觀點而言其實並不理想,因為來源解碼器晶片變成與傳輸媒介有關,於是有線電視、地面廣播和衛星接收器都需要不同的主機元件。這使原始設備製造商(OEM)無法開發一套通用硬體平台(圖4),不僅影響產品的經濟規模,還會增加廠商的認證和組裝成本。通用硬體平台只需一個可連接各種傳輸媒介的射頻前端,另外還有一個與數位電視播送方式如衛星、有線電視、地面廣播或IP網路等無關的主機處理器。從圖4即可看出,通用硬體平台顯然是較合理和較低成本的系統分割方式。

|

| 圖3 單通道DBS接收機的整合方式 |

|

| 圖4 有線電視、地面廣播電視和衛星電視機上盒的通用設計平台 |

直接轉換調諧器限制系統整合度

圖2為零中頻接收機架構,儘管固定增益放大器通常擁有較好的雜訊指數和線性特性,射頻低雜訊放大器(LNA)多半仍由一個高度線性的固定增益放大器和一個連續可變增益衰減器串聯而成。L波段射頻訊號經過放大後,就送到類比正交混波器降轉至基頻,然後由基頻可變增益放大器及其後連接的低通疊頻消除(Anti-aliasing)濾波器提供I和Q正交類比輸出至解調器晶片。為了減輕直流偏移的影響,電路需要很低的轉角頻率(Corner Frequency),這表示它必須使用晶片外接的較大耦合電容,此時若訊號路徑採用很大的增益步階例如離散步階的自動增益控制器,那麼電路調整增益後就需長達數毫秒的時間才能穩定,這個過程中將出現連續大量的錯誤資料,而且無法藉由FEC加以更正。因此,直接轉換調諧器必須使用電晶體在作用區(Active Region)工作的連續自動增益控制迴路,只不過其訊號路徑的雜訊和線性特性都不如僅需電阻和開關等被動元件的自動增益控制電路。

零中頻調諧器的優點是能將類比數位轉換器輸入端的目標通道頻寬減至最小,DBS系統的符碼率(Symbol Rate)變化範圍為1~45Mbaud,3dB訊號頻寬約是符碼率的1.35倍。因此在零中頻架構裡,I和Q通道的最高頻率大約等於30MHz,這表示類比數位轉換器的取樣速率必須達到80~90MSPS。另外,調諧器內含的可變頻寬低通濾波器還能大幅衰減相鄰通道訊號,唯有確保目標通道訊號才會出現在類比數位轉換器輸入端,這能降低類比數位轉換器所須提供的動態範圍和解析度,通常為六位元,降低解析度和取樣頻率都能減少類比數位轉換器的耗電。

確保鎖相迴路穩定度

射頻合成器由多個LC振盪器組成,這能將相位雜訊減至很小,最小通道隔離度則可低至1MHz左右。由於整數N鎖相迴路(PLL)的頻寬至少要比參考頻率小十倍,所以它需要頻寬很小的鎖相迴路,只不過這類鎖相迴路會增加通道切換時間(Zapping Time)和降低通道掃描速率。直接轉換DBS調諧器通常使用分數N(Fractional-N)鎖相迴路,這能加快鎖相迴路的穩定速度,並保留精密的頻率解析度以提供相鄰通道隔離能力。然而分數N合成器通常更複雜耗電,設計人員必須仔細分析高階Δ-Σ調變器迴路可能造成的分數混附訊號(Fractional Spur)和系統穩定等問題。

由於鎖相迴路的頻寬較小,故須使用晶片外接的迴路濾波器,這讓敏感的振盪器控制電路必須連接到電路板上的訊號線。一般說來,獨立調諧器可以透過適當的電路板設計來限制壓控振盪器(VCO)的耦合雜訊,至於電路板層級主要的混附訊號耦合來源則包括交換式電源穩壓器、石英振盪器輻射的參考單頻(Reference Tone)和其他數位元件產生的單頻訊號。

但在使用多晶粒SiP封裝元件時,工程師就必須仔細分析和設計所有的晶粒接線,以便將數位解調器、LNA輸入接線、頻率合成器參考時脈石英晶體接線、晶片外接鎖相迴路濾波器接線和晶片內建LC振盪器電感之間的磁耦合減至最少。由於零中頻調諧器會將射頻訊號直接降至基頻,所以不可能透過頻率管理來避免某些混附單頻訊號(Spurious Tone)。

廠商曾發展出低中頻DBS調諧器/解調器架構,它能避免1/f雜訊對調諧器雜訊指數的影響,並且消除訊號路徑的直流偏移。而新架構採用高於1/f雜訊轉角頻率的中頻頻率,避免訊號路徑的大部分閃爍雜訊(Flicker Noise);另外,調諧器輸出訊號也不再包含直流電壓。由於中頻頻率約為40MHz,耦合電容可以減少至數個pF,只要靠著晶片內建電容就能消除訊號路徑的任何直流偏移。

數位化提高濾波品質/縮減尺寸

在數位低中頻調諧器設計裡,類比混波器會把一群L波段射頻通道轉換至低中頻,接著進行濾波和類比數位轉換,最後才在數位域裡把訊號降至基頻;相較採用類比通道濾波的調諧器設計,這種方法可以提高濾波品質和減少使用面積,所得到的數位低中頻調諧器也很適合採用CMOS製程,這種調諧器還能把解調器整合到同一晶片。

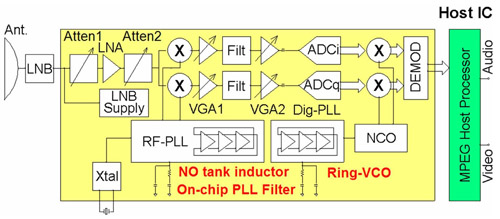

圖5是低中頻DBS衛星電視接收機的功能方塊圖,它會等到第二個數位混波器利用數值控制振盪器(NCO)把訊號降至基頻後,才在數位域執行最後的通道選擇。電路接著會將QPSK基頻訊號解調,再透過晶片輸出接腳提供所產生的MPEG傳輸串流(Transport Stream)。這是真正的L波段射頻至MPEG串流接收機單石晶片,可以根據DVB-S全球標準或DirecTV DSS DBS專屬標準接收衛星服務。

|

| 圖5 低中頻DBS接收機架構 |

低中頻架構具少雜訊/混附訊號效能

相較於零中頻架構,低中頻調諧器的直流偏移消除迴路會有較高的轉角頻率,故能在自動增益控制電路改變增益值後更快穩定下來,這使得應用設計可以採用離散步階的自動增益控制電路。離散步階設計只需要電阻和開關元件,這與連續式自動增益控制電路有很大不同。這種被動式自動增益控制電路的雜訊少於採用主動電晶體的衰減電路,線性特性也更優異--在最大增益值時IIP3=+25dBm,零中頻DBS調諧器通常只有+9dBm--這有助於提高接收機的IIP3效能。

第一個類比混合波器可由簡單的整數N頻率合成器利用較大的頻率步階例如20MHz,加以驅動,這個合成器可以採用環狀振盪器(Ring Oscillator),而不是LC振盪器。雖然環狀振盪器的相位雜訊較大,但由於參考時脈頻率高達20MHz,電路可以使用頻寬很大的鎖相迴路(頻寬1MHz),這不僅降低迴路頻寬內的相位雜訊,還能協助將迴路濾波器整合至晶片,避免雜訊與混附訊號耦合至敏感的壓控振盪器控制線路。

訊號降至低中頻後,就由一個可變增益放大器進行放大,這個可變增益放大器可與射頻前端衰減器搭配,提供衛星電視應用所需的寬廣增益範圍90dB。電路接著對訊號進行低通濾波和類比數位轉換,由於訊號中心頻率在40MHz附近,最大通道頻寬約為60MHz,類比數位轉換器必須提供高達200MSPS的取樣速率,這不僅超過零中頻調諧器的取樣速率,也使數位解調器的初級電路須在較高的時脈頻率下操作。除此之外,低中頻調諧器的耗電量也高於零中頻調諧器,這是因中頻訊號路徑需更大頻寬,類比數位轉換器和解調器核心也使用更高的時脈頻率。但在機上盒應用裡,耗電不是最重要的參數,反而調諧器的低雜訊和混附訊號效能(Spurious Performance)才是確保接收機在微弱射頻衛星訊號下,能提供最高接收靈敏度的關鍵。

數位解調器需要另一個鎖相迴路提供數位時脈,但設計人員必須謹慎規畫頻率,避免晶片內建的兩個鎖相迴路發生混附訊號耦合(Spur Injection)或是因為輸出負載變化而造成頻率變動(Pulling)等問題。第一個是環狀振盪器,它不需要任何電感,還能避免數位核心與射頻合成器之間的射頻訊號耦合。另外,只要把迴路濾波器整合到晶片,就能將敏感的壓控振盪器控制線路所耦合的混附訊號減至最少。在低中頻調諧器架構裡,只有數位核心與低雜訊放大器的輸入接線之間可能出現嚴重的射頻耦合,但設計人員可藉由正確地規畫頻率來避免這類耦合所造成的影響,例如在類比數位轉換之前略微移動中頻的中心位置,並為數位解調器的任何頻率移動提供適當補償。由於所有調諧器和解調器方塊都很容易導入CMOS製程,因此廠商不僅能開發出真正的單晶片調諧器與解調器,還可利用該矽智財(IP)繼續整合MPEG主機處理器。

低中頻調諧器截長補短

受到低轉角頻率直流偏移消除迴路的影響,零中頻調諧器的實作損耗(Implementation Loss)在符碼率較低時比較大,但是當符碼率很高時,它的實作損耗就變得較小;高中頻調諧器正好相反,它在符碼率很高時會出現比較大的實作損耗,這是因為晶片外接SAW濾波器的有限頻寬會造成群延遲失真(Group Delay Distortion)。另外,當資料速率較低時,過多的相位雜訊也會導致高中頻架構的實作損耗增加。相形之下,低中頻調諧器並沒有直流偏移消除迴路或晶片外接SAW濾波器,所以不僅實作損耗很小,還能在整個符碼率範圍內保持定值。

直接轉換架構的鏡像通道就是接收通道,故在阻隔要求較嚴、高鏡像拒斥比的通訊系統中占有優勢,但在衛星電視接收機裡,所有接收通道的功率分布模式(Power Profile)都很類似,因此鏡像拒斥比只要達到40~45dB就能符合要求。這表示就DBS應用而言,零中頻調諧器實際上並沒有贏過低中頻調諧器。除此之外,直接轉換調諧器與數位解調器之間還有許多的寄生參數耦合效應,因此很難把調諧器與解調器整合至單晶片。

相較之下,數位低中頻架構則能在數位I/Q校準後提供適當的鏡像拒斥比,並且設計出不含電感的射頻合成器。當本地射頻振盪器不含電感時,就算同一顆晶片還整合很大的數位解調器,它仍能將寄生參數耦合減至最小。環狀振盪器則能大幅減少晶片使用面積,這對降低成本和減少基材寄生耦合都有幫助;另外,它還提供更好的混附訊號效能,射頻頻率也比較不會因為負載或電壓變化而漂移(RF Pulling And Pushing)。在實際應用裡,雙轉換數位低中頻調諧器並不會增加接收機的複雜性,因為就算是零中頻調諧器也需要在解調器中增加另一級的數位混波電路,以便補償LNB振盪器頻率漂移。這兩種架構的主要區別在於,低中頻調諧器的數值控制振盪器提供更大調諧範圍,因為它必須補償LNB頻率漂移以及射頻混波器降頻轉換而造成一整群通道(Channel Cluster)的中頻中心點移動。

導入新製程減輕功耗

低中頻架構的一項小缺點是它需要頻寬較大的中頻電路,及時脈頻率較高的數位解調器和前端類比數位轉換器。這可能增加耗電,但此問題會隨著CMOS邁入90、65奈米及更精密的製程世代而逐漸減輕。表1列出零中頻與低中頻DBS接收機架構的效能比較。

| 表1 零中頻與低中頻DBS接收機架構效能比較 |

| 架構 |

直接轉換(零中頻) |

雙轉換(低中頻) |

| LNA |

‧衰減器在LNA後面==>線性較差 |

‧衰減器在LNA前面==>線性較好 |

| AGC迴路 |

‧連續式AGC迴路==>射頻前端的雜訊較大和線性較差 |

‧離散步階AGC迴路==>射頻前端的雜訊指數較低和線性較好 |

| 混波器/LNA |

‧IIP2要求嚴格、沒有鏡像拒斥的問題 |

‧IIP3要求嚴格、需要鏡像拒斥校準 |

| 合成器 |

‧頻寬小==>大電容==>晶片外接迴路濾波器

‧多組LC的VCO設計==>晶片面積和雜訊/混附訊號耦合較大

‧本地振盪器訊號洩漏至LNA==>直流偏移問題

‧LC-VCO==>很容易達到相位雜訊要求 |

‧頻寬大==>小電容==>晶片內建迴路濾波器

‧一組環狀VCO==>晶片面積和雜訊/混附訊號耦合較小

‧沒有本地振盪器訊號洩漏的問題

‧需要較先進的鎖相迴路架構(雜訊衰減器),以便達到嚴格的DBS相位雜訊要求 |

| ADC |

‧動態範圍中等(六位元)

‧取樣速率中等(100MSPS)

‧沒有鏡像拒斥的問題 |

‧動態範圍較大(八位元)

‧取樣速率較快(200MSPS)

‧I和Q級電路必須匹配良好 |

| 雙接收機 |

‧兩組雙極調諧器+兩組解調器和MPEG處理器

‧兩組LC-VCO之間會有耦合的問題 |

‧很容易將兩組調諧器整合至同一個晶片,這是因為頻率偏移很大時,環狀VCO因為輸出負載變化而造成的頻率改變可以忽略 |

| 面積 |

‧LC-VCO需要多個電感==>面積較大 |

‧沒有電感==>面積大幅縮小 |

| 整合 |

‧SiP封裝,包含雙極性調諧器前端與CMOS基頻後端。 |

‧CMOS系統單晶片,包含調諧器和解調器+(MPEG處理器)。 |

| 成本 |

‧BiCMOS調諧器與CMOS解調器的SiP封裝成本很高。 |

‧可將調諧器和解調器射頻前端整合為低成本的系統單晶片。透過這種系統功能分割方式,只要一個MPEG元件就能支援有線電視、衛星電視和地面廣播 電視等產品線。 |

要實現單晶片DBS接收機,一種低成本方法是採用CMOS製程的調諧器/解調器,低中頻調諧器則是達成這項目標的理想架構,只要把更多的訊號處理作業轉移到數位域執行,系統對射頻前端的要求就毋須如此嚴格。隨著現代深次微米CMOS製程讓數位電路的速度越來越快,這種利用數位訊號處理器(DSP)解決類比CMOS製程非理想特性的做法將會變得更有用。

(本文作者任職於Silicon Laboratories)