在一個晶片內部整合多個數位訊號處理(DSP)模組、寬頻數位類比轉換器(DAC)、以及寬頻類比數位轉換器(ADC),如今不僅能分擔許多高耗電FPGA資源的處理負載,造就出更小占用空間、更省電、以及增加通道數量的平台,而且取樣速度還能更超越以往。

這項新功能伴隨而來的是新開發的多晶片同步化(MCS)演算法,藉由這些積體電路(IC)內含的演算法讓使用者可為所有4個通道達到已知(定性)相位,並為系統供電,亦或藉由軟體來修改系統。這個定性階段因而能簡化廣泛系統層級校正演算法,藉以達到所有通道所需的同步化,包含輸出或輸入端連到前端網路,而這些網路則連到這些IC。本文將闡述各項實驗結果,展現MCS功能,以及運用16通道的接收器/發送器平台,此平台包含多個數位化IC、時脈源、以及數位介面。

高層級系統模組圖

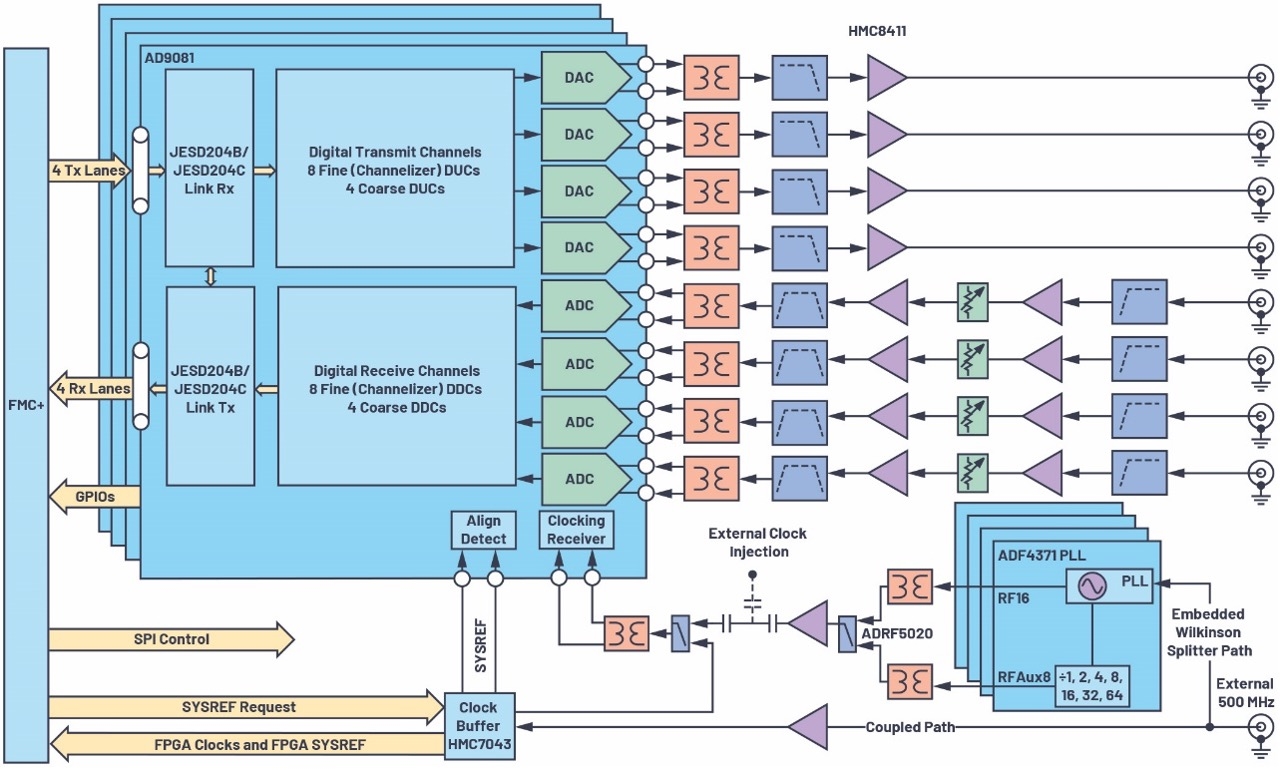

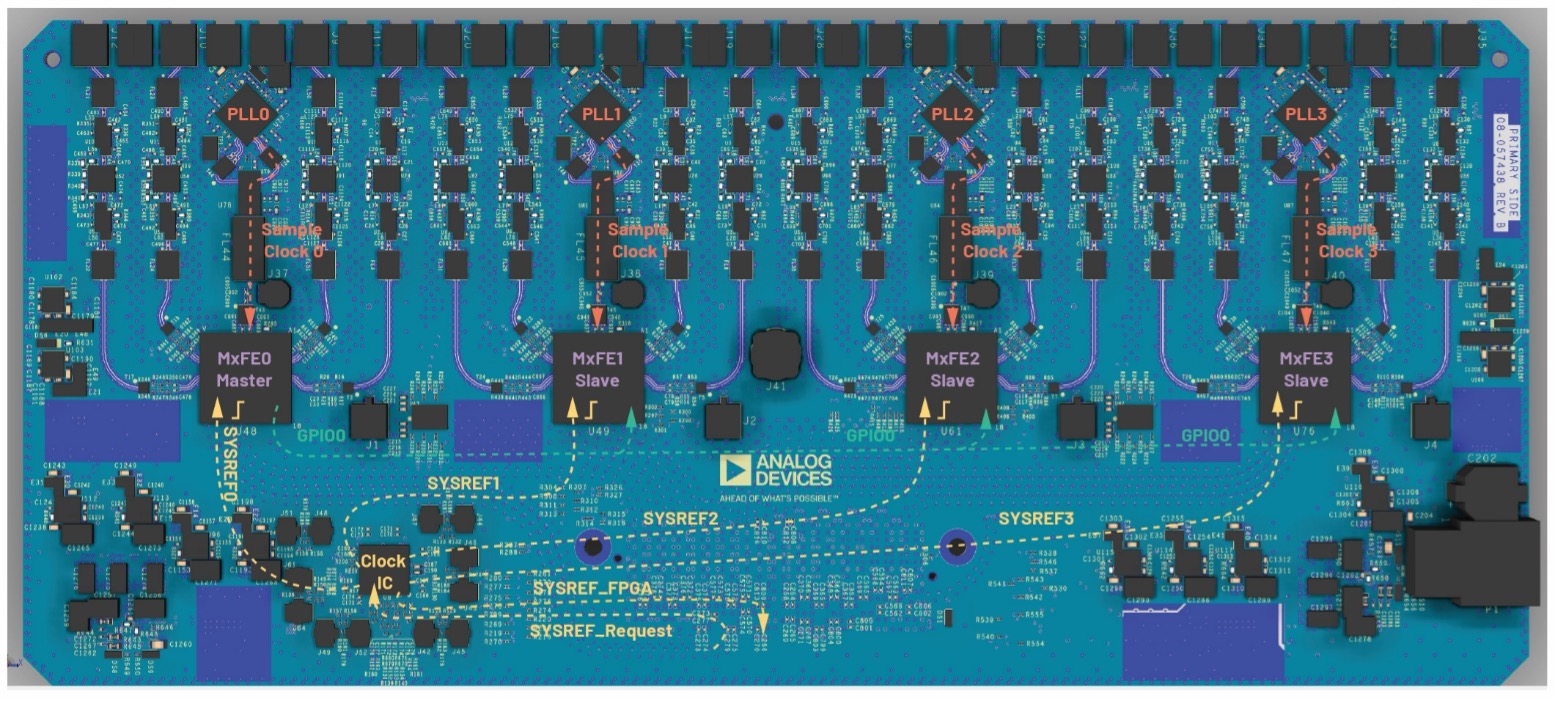

這個測試使用的模組圖如圖1所示,圖中包含4個整合式 DAC/ADC/DSP IC,每個IC各自含有4個12 GSPS DAC、4個4 GSPS ADC、以及12 個數位升頻轉換器(DUC)以及12個降頻轉換器(DDC)。DUC/DDC允許頻率轉換,與/或數位域(digital domain)的內插/抽選(decimation)。用一個500 MHz參考時脈注入到機板,我們即可利用參考鎖定時脈緩衝區來產生MCS需要的系統參考訊號,以及數位介面連至基頻處理器(BBP)所需的時脈。此外,系統還包含4個鎖相迴路(PLL)合成器,負責產生12 GHz源,從共同參考為每個數位IC提供所需的時脈。射頻前端元件連至每個數位器輸出/輸入,負責產生經過濾波與放大的訊號,往返連結邊緣發送的射頻連接器。這裡我們建置全電力分佈解決方案。系統所需的所有電壓都是從12伏電源產生。所有傳送訊號會傳遞到機板底部,而所有接收到的訊號會傳至機板的頂端,藉以達成最佳的通道對通道隔離。

圖1. 系統的高層次模塊圖用來展現MCS與多通道校正演算法

圖1. 系統的高層次模塊圖用來展現MCS與多通道校正演算法

子陣列時脈樹結構

如先前所述,子陣列時脈樹含有一個500 MHz的參考源(reference source),分配(split)後傳送到4個PLL合成器IC的參考輸入,如圖1所示。這個500 MHz訊號也經過10 dB耦合、放大、然後傳送到另一個時脈緩衝區IC,該IC負責產生數位介面所需的系統參考(SYSREFs)以及BBP時脈。這個時脈樹的目標有三方面,它將能夠:

選擇時脈樹IC用來展現各種機板佈線異常,可運用這些晶片內的數位與類比延遲模塊,在軟體與/或硬體中進行校正。最終的結果是時脈樹能在這些IC的相同取樣時脈週期內為所有需要的IC提供SYSREF脈衝。

連結數位介面的基頻處理器

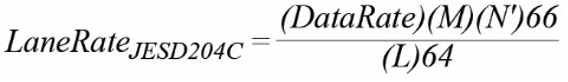

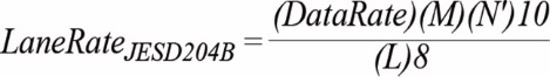

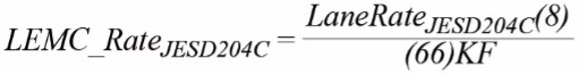

4個數位化IC各自搭配基頻處理器(BBP)建立JESD204B 或JESD204C數位鏈路介面1,2。這個介面負責透過實體線路(SERDES)傳送ADC與DAC資料碼,在基頻處理器之間往返傳輸。這個介面使用的差動式SERDES線路數量,標示為該鏈路的鏈路(L)數量。透過鏈路傳送時的轉換器位元解析度,標記為N'。通道化(channelized)資料管道的數量,亦即虛擬轉換器,則標記為M。本文顯示的結果,使用JESD204C鏈路,M = 16,N' = 16,L = 4配合DAC側鏈路,M = 8,N' = 16,L = 2 配合ADC側鏈路。

數位化IC與基頻處理器之間資料傳輸的速度,稱為鏈路速度。晶片內的DSP模塊(亦即DDC/DUC)讓使用者能以不同速度來對數化器(digitizer)取樣,不同於實體鏈路資料傳輸的速度。因此,鏈路速度取決於每個資料通道上數位抽選/內插資料速度。在這個案例中,使用250 MSPS I/Q資料率。對於JESD204C介面,鏈路速度定義為:

JESD204B介面的鏈路速度定義則是:

本文展示的結果是對ADC與DAC側的JESD204C鏈路採用16.5 Gbps的鏈路傳輸率。

每個JESD204B/JESD204C鏈路可分別建立在不同的子類(subclasses)。而區分子類的原則,可依據是否需要多晶片同步化或是確定延遲等特色。在這個案例中,資料的顯示是採用JESD204C Subclass 1模式,因此會用SYSREF訊號針對系統中多個鏈路傳送中數位資料進行校準。在這個JESD204C Subclass 1模式中,SYSREF訊號用來校準本地延伸多模塊計數器(LEMC),該計數器的傳輸速度為:

這裡的F是每個通道中每個JESD訊框的位元組(octet)數量,而K則是每個多重訊框(multiframe)中的訊框數量。在這個案例中,F = 8 而K = 32,因此使用LEMC rate為7.8125 MSPS。能掌握LEMC相當重要,因為任何成功的MCS必須展示射頻頻率不是LEMC速度的整數倍,而且能達到定性的電源啟動相位。

多晶片同步化方法

在這個系統中,寬頻整合式ADC/DAC IC提供MCS電路,讓所有傳送與接收射頻通道上都達到電源啟動定性相位,甚至是在使用IC中的DUC/DDC DSP模塊。在工廠執行校正時,這個MCS功能讓使用者叫出查表(LUT),將操作停頓時間縮至最短。任何成功的MCS必須在系統中所有通道上提供定性相位,包括每一種射頻頻率、溫度梯度、以及系統電力循環。

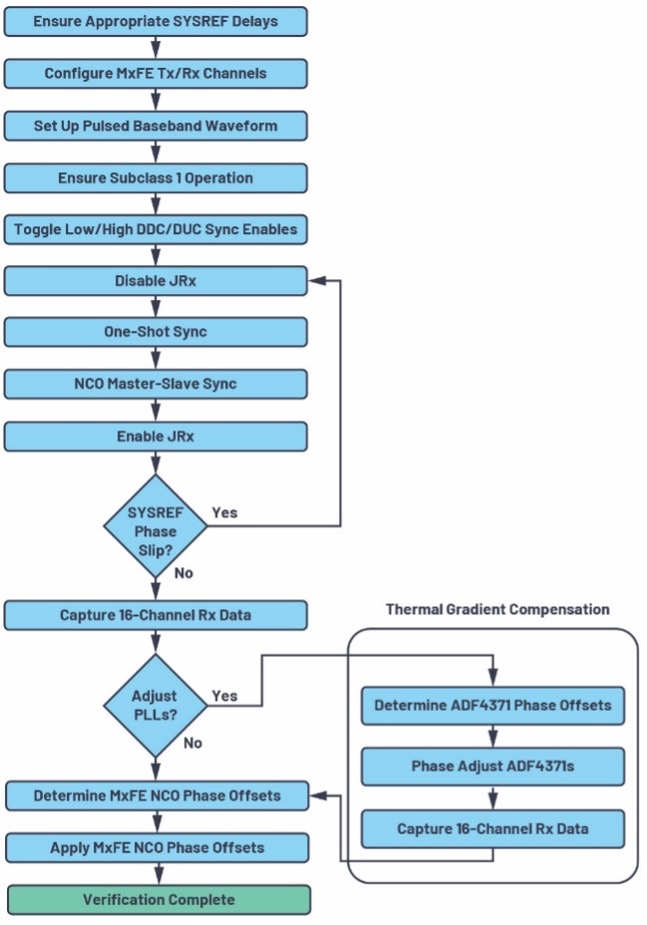

整合式ADC/DAC IC內含12個DUC 模塊以及12 個DDC 模塊,如圖1所示。每個模塊含有一個內插(DUC)與抽選(DDC)子模塊,用來變更DAC數位輸入訊號或ADC數位化輸出訊號的資料傳輸率。此外,每個DUC/DDC還含有一個複雜數值控振盪器(NCO),用來在數位域轉換頻率。這些NCO能執行複雜的即時相位調整,讓DAC/ADC與BBP之間的數位訊號能進行調整,藉以補償各種SERDES線路長度失配。這些ADC/DAC IC的MCS功能負責在數化IC資料通道的每個區段達成相位確定性。達成MCS的工作流程如圖2所示。

圖2. MCS工作流程涉及多個功能,用來校準資料通道的各個部分

圖2. MCS工作流程涉及多個功能,用來校準資料通道的各個部分

MCS演算法可分成兩個不同功能:

執行一次性同步功能時,使用者必須先定義JESD鏈路參數(像是M、N'、L等),然後為SYSREF平均化設定同步邏輯(如果是使用連續SYSREF脈衝)。此外,預期的LEMC延遲可用來強制在SYSREF訊號邊緣後經過一定延遲再產生LEMC。這個步驟完成後,使用者可啟動每個數位化IC內的一次性同步位元,然後要求SYSREF脈衝在相同時脈週期內傳送到每個IC,如圖3所示。在這個系統中,類比細密延遲(fine delay)出現在時脈緩衝區IC,讓同步SYSREF傳送到所有數位化IC。後續的檢查可檢驗一次性同步流程是否執行成功,查詢每個IC內的暫存器,即可掌握SYSREF訊號與每個IC鏈路LEMC邊緣之間的相位關係。在量測到穩定相位後(SYSREF-LEMC 相位暫存器讀出0),使用者就知道所有數位化IC的LEMCs完成校準,使用者就能繼續執行NCO的主控-從屬端同步程序。對於這項作業而言,一次性同步的子任務被侷限在晶片製造商提供的應用編程介面(API)。

圖3. MCS演算法用SYSREF訊號執行一次性同步,並用GPIO訊號執行NCO主控-從屬端同步,藉以達成確定性相位

圖3. MCS演算法用SYSREF訊號執行一次性同步,並用GPIO訊號執行NCO主控-從屬端同步,藉以達成確定性相位

NCO主控-從屬端同步功能首先會指派子陣列內的一個數位化IC作為主控晶片,如圖3所示。所有其他數位化晶片會被視為從屬端IC。主控IC會把元件的GPIO0接腳設為輸出端,並連到三個從屬端數位化IC的GPIO0 nets。從屬端的GPIO0 nets則會設成輸入端。之後使用者可選擇觸發SYSREF脈衝、LEMC升緣、或LEMC降緣。對於本文所述的資料,LEMC升緣用來作為NCO主控-從屬端同步觸發訊號源,接著GPIO nets會透過基頻處理器外連而不是連到本地端的子陣列。接著再將DDC同步位元切至低位(toggled low),之後再切至高位以執行ADC側的NCO同步演算法。類似的程序,微處理器校準位元先切換至低位,然後再切換至高位以執行DAC側的NCO同步演算法。

在發出這個觸發訊號要求時,主控端數位化IC在下一個LEMC升緣就會向GPIO0 net發送master out訊號。這個訊號會傳到每個從屬端裝置的GPIO0輸入端。在下個LEMC波型緣,所有數位化IC都會經歷NCO重置演算法。在此之後,任何LEMC脈衝都會被NCO主控-從屬端同步演算法忽略。對於一次性同步而言,這些NCO主控-從屬端同步子任務會侷限在API函式讓使用者方便使用。

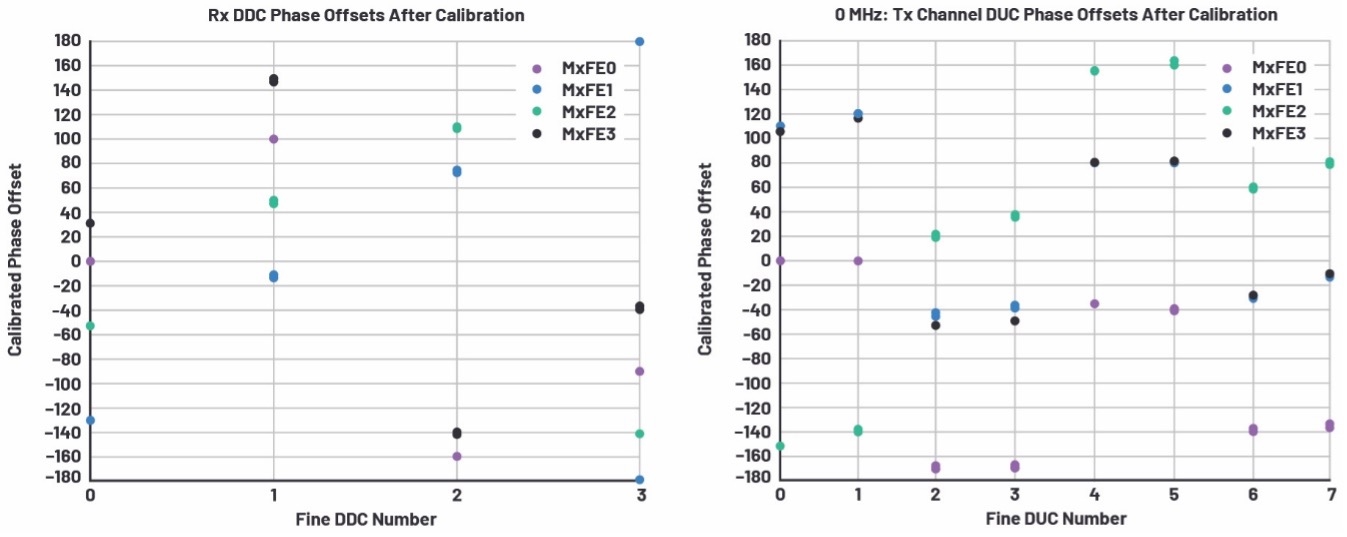

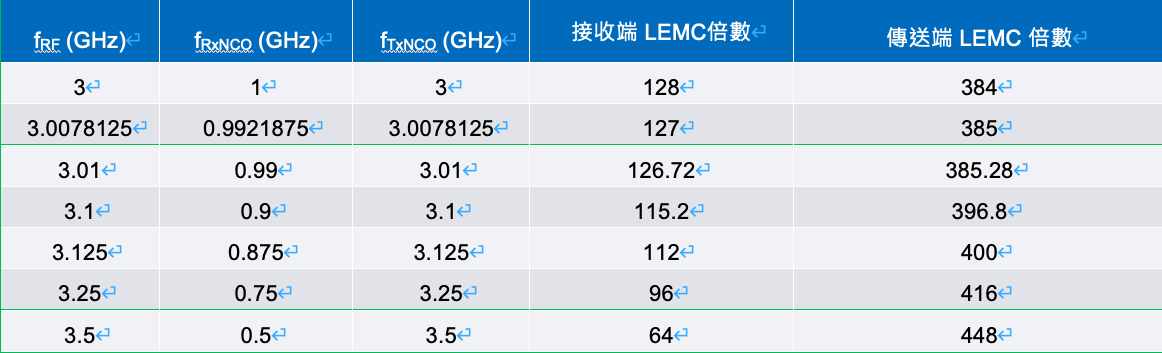

運用一次性同步與NCO主控-從屬端同步功能可校準輸入端與每個DDC/DUC,如此一來每個接收與傳送通道的輸出相位偏移在經過多個電源週期後就會重複,如圖4所示。圖4的資料顯示經過100個電源週期後經校正的相位偏移(以實心點標示),反映的是接收與傳送通道分離器(channelizer),每次重開機時系統會在靜態熱梯度下工作。

圖4. 在執行MCS演算法時,接收端細密DDCs (左)與傳送端細密DUCs (右)進行妥善校準

圖4. 在執行MCS演算法時,接收端細密DDCs (左)與傳送端細密DUCs (右)進行妥善校準

圖中顯示多個點,每個顏色的點代表一個DDC/DUC,在每個電源週期之後緊密叢聚在相同位置,反映出特定通道的確定性相位。在這項測試的資料中,所有8個通道分離器(channelizer)DUC都是用在傳輸側,因此8個通道分離器DUC只會用到其中的4個。不過當同時使用MCS演算法時,現已證實使用所有8個通道分離器DDC的確能提供確定相位。

如果PLL合成器取樣時脈與時脈IC SYSREF在啟動時維持同相(same phase)關係,在啟動時執行這個演算法,即可為每個通道建立確定性相位。然而,任何系統在經歷溫度梯度後,可能導致PLL時脈漂移,如果沒有補償還可能導致出現不同的電源啟動相位。為補償系統中的溫度梯度漂移,這個平台採用PLL合成器相位調整的方法。

PLL合成器相位調整

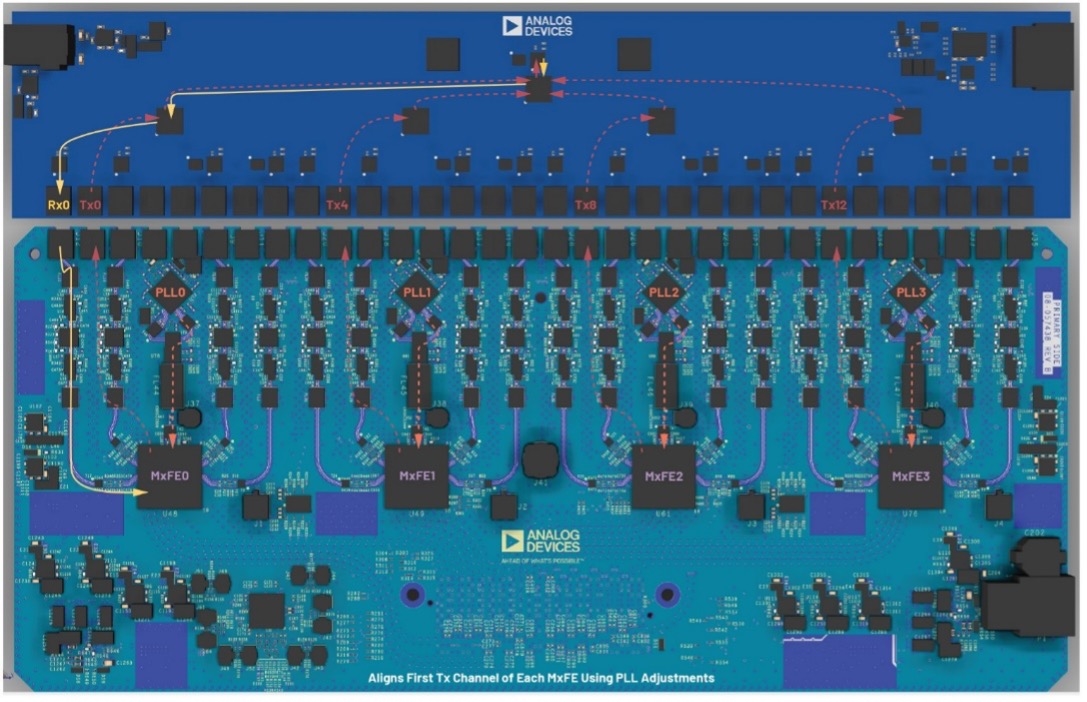

選擇PLL合成器IC目的是讓相對取樣時脈調整結果能導入到每個數位化IC。熱漂移以及每個IC中取樣時脈與SYSREF之間的PLL相位漂移,補償的方法是建立一個回饋機制,確保每個數位化IC的第一個傳輸通道其相位都和第一個數位化IC的第一個傳輸通道進行校準。為建立這種回饋迴路,每個IC第一個通道所輸出的訊號都會和其他傳輸通道有所差別,如圖5所示。這4個訊號合起來傳送到一個共同接收器,在這個系統中標記為Rx0。

圖5. PLL同步器的相位調整功能讓次陣列中每個數化器IC的第一個傳送通道進行校準

圖5. PLL同步器的相位調整功能讓次陣列中每個數化器IC的第一個傳送通道進行校準

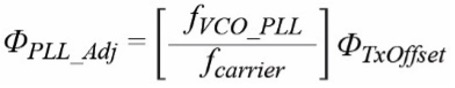

所有接收通道會同時收到資料,這讓使用者能套用交叉校正技巧,以及判斷4個傳輸通道之間的複雜相位偏移 ΦTxOffset。PLL合成器IC內含一個壓控振盪器(VCO),其工作頻率為ƒVCO_PLL。量測到的相位偏移ΦTxOffset,它和所需的PLL相位調整ΦPLL_Adj以及射頻頻率ƒcarrier的關係如下:

利用這個公式,我們可運用一個新的已知量來調整PLL合成器相位,針對所有電源週期在所有數位化IC之間建立一個共同傳輸基準(baseline),如圖6所示。每個通道的開圓(open circles)對應到第一個電源週期,所有其他實心點則對應到後續的電源週期。從這個圖可看出,所有數位化IC的第一個(與第二個)通道分離器在校正後的傳輸相位偏移都完成相位校準(aligned)。在這個案例中,每個數位化IC的第二個通道分離器也完成校準,這是因為系統中每個DAC使用兩個通道分離器。

圖6.藉由調整PLL相位,使用者即可校準所有數位化IC的第一個傳送通道

圖6.藉由調整PLL相位,使用者即可校準所有數位化IC的第一個傳送通道

在前一節討論的MCS程序之前加入PLL合成器相位調整步驟,能強制使用進入取樣時脈-SYSREF相位關係,從而在所有溫度梯度上建立定性相位,這樣的相位關係顯示在所有數位化IC的傳輸校準基線。圖7顯示透過每個PLL合成器晶片上的溫度量測單元(TMU)偵測到的引致溫度梯度。圖7底部可看到藍線,相較於對系統施予不同散熱風扇氣流的系統,在平台上各處的溫度有相當大的差異。對每個IC套用PLL相位調整,結果呈現不論對機板施予多少散熱氣流,當我們強制每個數位化IC的第一個傳送通道分離器相互校準時,每個接收與傳送通道上校正後的NCO相位偏移都會是定性的。這點反映在圖7中上方兩個圖中相同顏色的點呈現緊密聚集,儘管在不同電源週期中對機板套用不同的溫度梯度。

圖7. MCS功能配合PLL相位調整功能,展現所有接收與傳送通道在電源啟動相位的確定性,不受平台引致溫度梯度所影響

圖7. MCS功能配合PLL相位調整功能,展現所有接收與傳送通道在電源啟動相位的確定性,不受平台引致溫度梯度所影響

如圖7底部右邊顯示接受輪詢的數位化IC暫存器,圖中顯示在施予PLL合成器相位偏移後,量測到的SYSREF-LEMC相位關係。請注意從底部左邊的橘線開始,PLL合成器相位調整就完全補償任何量測到的非零SYSREF相位,這些相位來自於不同引致的溫度梯度。

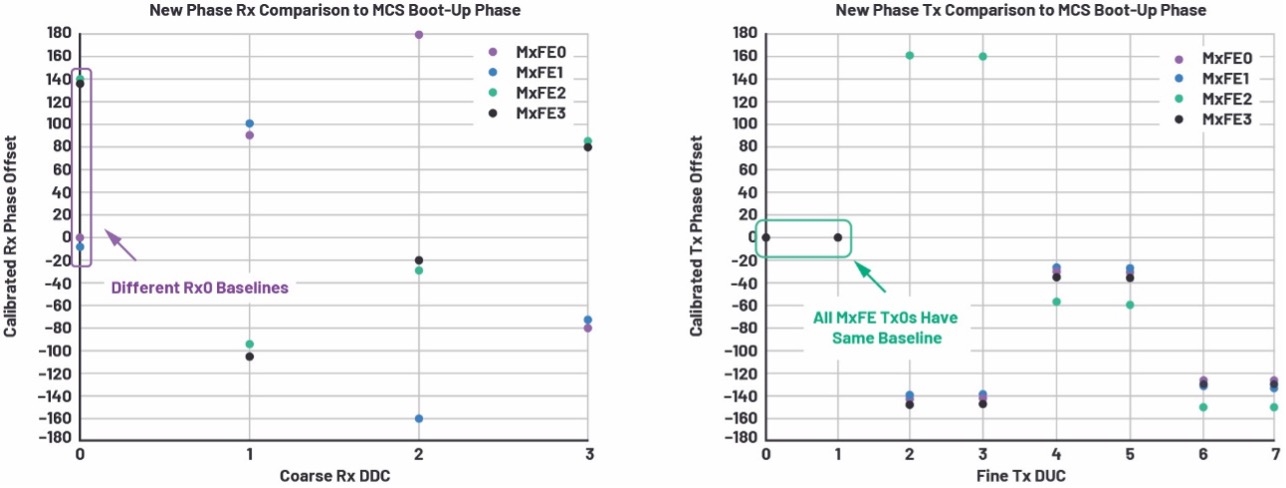

這裡我們量測到許多頻率,而所有頻率都展現接收與傳送相位的確定性。圖8顯示本文選用的特定頻率,選擇這些頻率目的是在使用非整數的參考時脈或LEMC時,能在許多引致溫度梯度上展現出MCS。

圖8. 本文選擇使用的RF頻率,目的是展現在各種時脈來源下MCS的功能,包括非整數倍的參考時脈與LEMC

圖8. 本文選擇使用的RF頻率,目的是展現在各種時脈來源下MCS的功能,包括非整數倍的參考時脈與LEMC

擴充至多重次陣列的能力

本文顯示的資料主要專注於次陣列層級MCS效能,但仍有必要在多個次陣列之間更大陣列層級上確保這些同步功能可以實現。為達成更高層級的同步化,需要陣列層級的時脈樹來確保如圖1所示向每個次陣列發出的SYSREF要求會同時抵達每個次陣列的時脈緩衝區IC。根據這項標準,每個次陣列都能發送先前所述的SYSREF與BBP時脈,在更大陣列的範圍中,這些訊號都能在相同取樣時脈週期抵達次陣列數位化IC。這個陣列層級的時脈樹要求時脈分佈至每個次陣列,藉以讓延遲調整區塊能同步執行SYSREF要求傳遞,一起送到每個下游的次陣列時脈晶片IC。藉由這種方式,連至多個次陣列的各個基頻處理器最終都能達到同步化。

系統層級校正演算法

雖然前面提及的MCS演算法的確能為每個接收與傳送通道在電源啟動時提供定性相位,但由於各個通道射頻前端線路長度一旦有任何差異,在射頻域(RF domain)上所有通道的這些相位就不一定對準。因此,雖然MCS演算法的確能簡化陣列校正流程,但仍需要執行系統層級的校正程序,校準系統中每個射頻通道的相位。

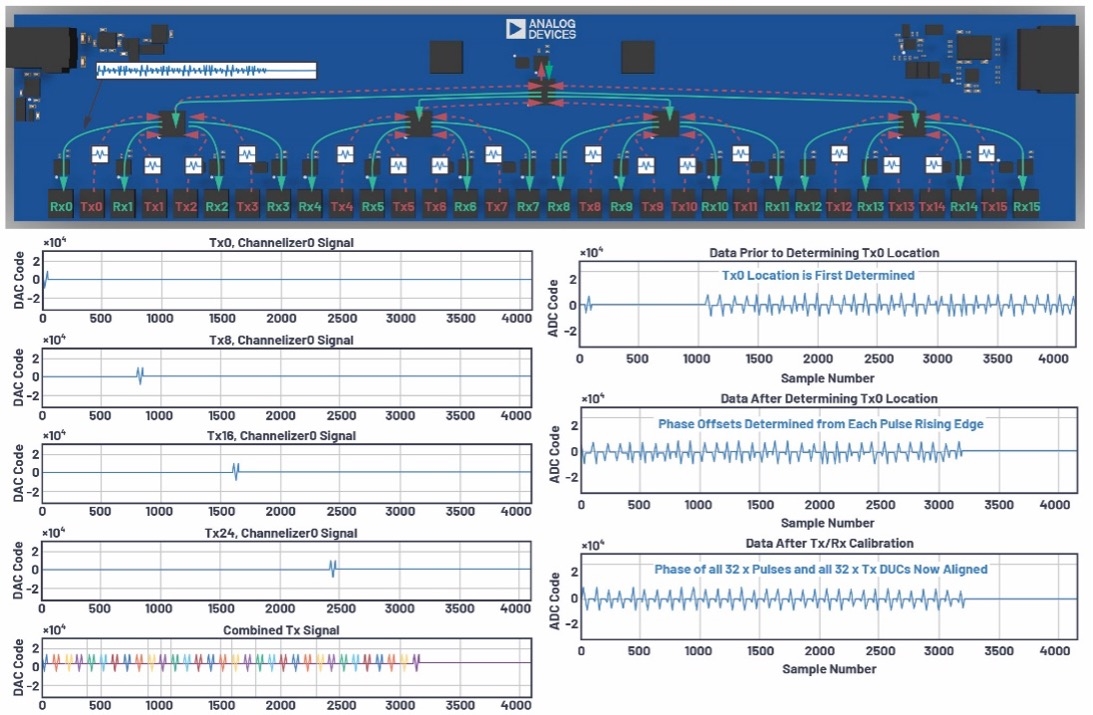

因此除了執行MCS演算法外,還需要開發高效率的系統層級校正演算法。本文介紹的系統層級校正方法採用特定基頻波形,而且完全自足(self-contained),不需要任何外部設備。本文介紹的系統能將各個基頻波形注入平台上每個通道分離器。利用這項功能,含有每個傳送通道分離器一個週期脈衝的基頻波形會注入次陣列,如圖9底部左邊所示。因此每個通道分離器只會輸出一個脈衝,所有傳送通道分離器的波形會交錯,整個系統在一個時間點上只會輸出一個單一週期的脈衝。所有傳送通道分離器的輸出會在射頻域匯集,之後經過分割然後傳回到所有接收通道,如圖9上方所示。最後,會對所有接收通道執行同步接收資料的擷取,資料會存成4096x16格式的矩陣,所有16個接收通道以4096的取樣大小進行收集。

圖9. 系統層級校正演算法搭配MCS,快速校準系統中所有接收與傳送通道

圖9. 系統層級校正演算法搭配MCS,快速校準系統中所有接收與傳送通道

資料延著第一行(對應Rx0)進行垂直分析,藉以找到Tx0通道分離器的脈衝,如圖9底部右邊子圖上方所示。找到Tx0脈衝就能判斷所有其他脈衝的位置,每個脈衝上升緣的複雜脈衝就能推算出來並儲存成1x16的向量,該向量對應到量測相位偏移,而這些偏移可能出現在系統所有傳送通道。憑藉這項知識,再運用Tx0當作基準參考,所有傳送通道的複雜相位就可根據量測到的偏移進行修改。

類似的原理,由於相同的組合訊號傳送到所有接收通道,因此資料會與矩陣一同進行水平分析(分析所有接收通道)。所有接收通道的複雜相位會參照Rx0進行量測,結果存入到一個1x16向量,該向量對應到系統中量測到的接收相位偏移。接收NCO複雜相位之後對進行調整,包含整個次陣列,讓所有通道的相位與Rx0進行校準,如圖10所示所有16個接收通道的同相(I) 與正交相位 (Q) ADC codes。注意到雖然圖10中所有通道的相位都對準,但所有通道的振幅卻不一定對齊。不過,利用這些數位化IC現在內建的有限脈衝響應(FIR)濾波器,我們也可以讓所有通道的振幅與相位全部對齊,不需配置極耗電的FPGA就能達到相同的結果。

圖10.透過MCS與自足式系統層級校正演算法完成16通道接收I與Q相位校準

圖10.透過MCS與自足式系統層級校正演算法完成16通道接收I與Q相位校準

這個系統層級校正演算法目前是用MATLAB軟體大約費時3秒執行完成。然而,倘若是用硬體描述語言(HDL)建置,不僅校正時間會進一步縮短,還能維持完全自足的演算法型態。此外,藉由依賴MCS演算法,倘若在啟動時就知道系統頻率與振幅,使用者可從查表載入相位偏移值,不需執行系統層級校正方法所描述的量測過程。在這個案例中,系統層級校正方法可用來叫出原廠校正時存在查表中的相位偏移。

MCS流程力助系統校正

上述介紹的成功MCS流程,採用4顆Analog Devices的AD9081 MxFETM IC作為次陣列的骨幹。平台的溫度梯度則透過4個ADF4371 PLL合成器內部相位調整模組的協助下進行補償。HMC7043 時脈IC用來傳遞JESD204C介面所需的SYSREF與BBP時脈。AD9081內的MCS演算法協助執行簡化的系統層級校正,並針對系統中的多種頻率與溫度梯度提供電源啟動的定性相位。高效率的系統層級校正演算法用來叫出原廠校正時用的LUT查表資料,因此能大幅縮短系統開機時間。

(本文作者皆任職於ADI)

參考電路

1 Del Jones. “JESD204C Primer: What’s New and in It for You—Part 1.” Analog Dialogue, Vol. 53, No. 2, June 2019.

2 Del Jones. “JESD204C Primer: What’s New and in It for You—Part 2.” Analog Dialogue, Vol. 53, No. 3, July 2019.