通訊系統介面整合時,初次接觸串列/解串列(SerDes)元件,筆者使用賽靈思(Xilinx)所提供的串列解串列元件ISERDES與OSERDES建構傳輸介面,初期使用排插加上雙絞線做傳輸,後來以串列式先進附加(SATA)插槽透過SATA線將數位IQ訊號傳給後端團隊進行進階的數位訊號處理。

|

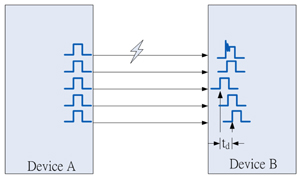

| 圖1 並列傳輸容易發生電磁干擾以及傳輸延遲差異,使傳輸速度受限。 |

串列/解串列器能將並列資料轉換成串列資料,減少及克服並列傳輸時因資料速率提高而突顯的影響傳輸品質的因素,如電磁干擾、資料傳輸線延遲差異(SKEW)等問題(圖1)。然而,要使資料流(Data Streaming)保持在正常工作條件下,勢必要提高時脈做取樣,才能完整傳輸並列資料。

例如,Device A是一次4位元(bit)處理資料,操作頻率為125MHz、週期8奈秒(ns),若要進行單條的串列傳輸給Device B則必須採500Mbit/s以上的速度傳送。

然而,串列傳輸在傳輸時通常會對資料做編/解碼動作(如8B/10B編解碼),除了可提高線路訊號完整度(Signal Integrality)外,並且可以提供串列傳輸時必要之資料同步、時鐘還原、資料保護和損壞修復等機制。

慎選高速介面

隨著系統開發的複雜度日益增加,模組的開發經常是不同背景的團隊一起合作,因此高速介面的選擇要格外謹慎。常見的高速介面有SATA、乙太網路(Ethernet)、PCI-E、AIF等等。介面的選擇除了因產品規格不可改變外,盡量選擇一些常見並且線材取得容易的介面如SATA線、網路線,方便實際使用時能快速採購和汰換。

一開始,筆者使用雙絞線加排插做傳輸,發現經常因碰觸而造成傳輸資料遺失或錯誤等情形。後來改採市售的SATA線,但又遇到同樣標榜著SATA2且相同長度的線材,因廠牌不同,而無法混合使用,因為廠商設備不同,即使同樣標示55公分(cm),買回來比較發現還是有些許差異。

最後,即使採用同一廠牌同樣長度的線材,也因為良率關係,造成傳輸速率無法提升,這時候線材取得的容易度就很重要,買個好幾條備用,先找出範本(Golden Sample),再用範本做交叉比較。

若單就模組開發而言,避免使用不易製造的規格如PCI-E(若產品特性則另當別論)或AIF等腳位密度高且容易與插槽偏移的介面,也能降低出錯的風險,更間接縮短開發時程。

找出較佳系統方案

串列/解串列器的功能是可以由兩顆晶片負責處理,如Maxim的MAX9205或MAX9207做串列器,搭配MAX9206或MAX9208則扮演解串列器,讓系統整合有彈性做調整。

然而,隨著製程技術的進步,晶片廠商也將串列/解串列收發器整合至單一晶片中,同時也能提升傳輸速度(因為訊號拉出晶片後,影響傳輸速度的因素變多,如PCB材質、繞線長度等等),如邁威爾(Marvell)與富士通(Fujitsu)合作推出的88i6536便是個SATA II系統單晶片(SoC)用於硬碟控制上,減少材料數量及成本。不同的架構符合不同的市場需求,仍要逐一分析後,方能找出較佳的系統方案。

低成本產品更要積極尋找免費資源

開發初期若選擇邏輯閘數目較多且含有特殊特性的型號,如賽靈思XC6SLX75T(其中T表示含有GTP元件),搭配廠商所提供的免費傳輸矽智財(Intelligent Property)如Aurora 8B/10B,不但能縮短開發時程,也能透過性能較好的平台催生更優異的產品功能。

然而,現實是材料成本會明顯提高,尤其消費性產品對成本控管更是嚴格,不得不慎選關鍵元件(Key Components),這都考驗著架構規畫者的判斷與取捨。

本次專案的架構選擇兩顆現場可編程閘陣列(FPGA)晶片,分別是成本負擔較低且不含GTP的Spartan-6以及高階的Virtex-6,前者執行簡易的訊號處理,如訊號品質調整、升/降頻等功能,後者則實現複雜演算法。其中筆者參與Spartan-6的傳輸介面,使用串列/解串列器元件ISERDES和OSERDES,其規格最高可達1,080MHz(表1),再搭配賽靈思提供的應用筆記(Application Note)做修改,讓一組時脈訊號,可帶四組16位元資料訊號做傳送。

如此一來,整體的傳輸速度最高能達到4,320Mbit/s以上,無須使用賽靈思GTP的特性,減少成本,未來還能移植架構概念至其他系列上,如Kintex-7。

設定Spartan-6內串列器/解串列器元件

若是有經驗的現場可編程閘陣列設計開發人員,都清楚現場可編程閘陣列廠商會提供一些硬巨集(Hard Macro)給使用者,也熟悉善用硬巨集確實能減輕及縮短開發負擔,例如內建數位訊號處理器(DSP)元件,就可透過操作精靈(Wizard)實現乘加器功能。

然而,賽靈思的FPGA內建串列/解串列器元件在輸入/輸出區塊(IOB)中,ISERDES/OSERDES讓使用者建構其訂定的串列規格,但是初次接觸這兩個元件的時候,讓筆者吃了不少的苦頭,原因是功能太多,為減少理解的負擔,以下簡化進行說明。

ISERDES負責接收

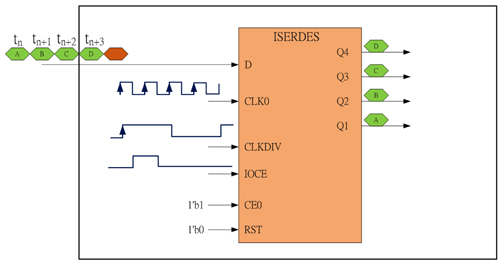

圖2為ISERDES簡易的示意圖,負責接收(解串列器),不包含其他功能如位元調整(BITSLIP)、相位偵測(Phase Detect)、串接(Cascade)。可透過屬性(Attribute)設定,針對ISERDES的BITSLIP_ENABLE設置FALSE;DATA_RATE設定SDR;DATA_WIDTH設定4,表示一次解四個串列位元;SERDES_MODE寫入NONE,表示不串接;INTERFACE_TYPE設成RETIME。

|

| 圖2 簡易的ISERDES使用方式(接收) |

D腳位接收序列訊號,先接收到最低位元(LSB),如圖2的位元A再依序接收到最高位元(MSB)之位元D。接收的資料會在腳位Q4-Q1出現,其中最高位元會在Q4出現。腳位CLK_DIV為接收資料後處理的FPGA並列時脈,若規格訂定125MHz操作,則輸入125MHz。腳位CLK0則為串列輸入時脈,若系統時脈為125MHz並且串列4位元,則CLK0須輸入125MHz×4=500MHz做取樣頻率。腳位IOCE是週期性脈波,讓ISERDES擷取正確的4位元。

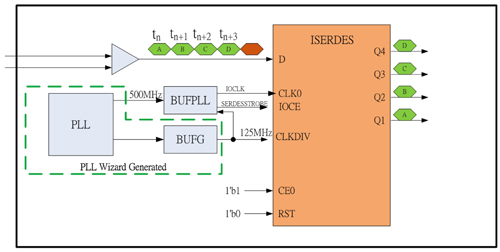

然而,這只是一個簡化元件的說明,還須要搭配其他元件才能正確動作。如圖3所示,透過鎖相迴路(PLL)產生兩組時脈,分別是高速時脈和系統時脈,如範例設定,分別是500MHz和125MHz,若由時脈精靈(Clock Wizard)產生,則無須在系統時脈加入BUFG,因為可由時脈精靈自動產生。手動加入亦可,但須在精靈介面操作時選擇。

|

| 圖3 資料解串列器簡易區塊圖 |

高速時脈則需要BUFPLL接收125MHz產生SERDESSTROBE給ISERDES做擷取觸發,這就是一組資料的解串列器,最後加上IBUFDS接收差動訊號,使用差動訊號能夠消除雜訊。然而,鎖相迴路的輸入並沒有標示,的確,要建構一個完整的解串列器,還需要一組輸入時脈(來自發射端),所以還要一組時脈的解串列器專門給時脈使用,如此一來,資料和時脈才不會有亞穩態發生,但這部分需要另一個元件IODELAY來配合,超出本文主題,詳細設置請參考賽靈思參考文件,編號XAPP1064。

OSERDES結構較簡單

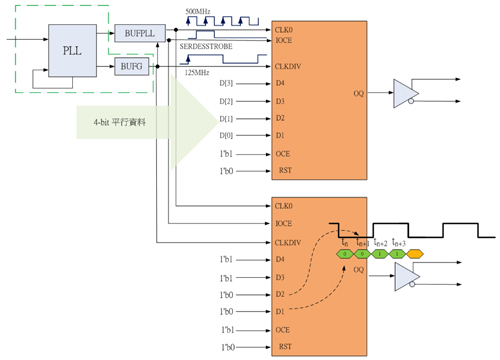

圖4為完整的資料和時脈串列器,共含兩組OSERDES,也就是一組時脈帶一組資料,相較於解串列器而言,串列器的結構較為簡單。

|

| 圖4 資料及時脈串列器區塊圖 |

針對屬性部分設定為配合解串列器設定,Data_RATE_OQ為SDR,DATA_WIDTH為4,OUTPUT_MODE為SINGLE_ENDED。接著,任選一組OSERDES作為時脈傳輸用,輸入的4位元須為一個常數,如4'b1100,透過串列器不斷地發送(低位元先傳輸),在接收端收到訊號所見,就如同時脈一般。

若以範例500MHz而言,完成一組常數資料(4'b1100)所需時間為8奈秒,其頻率為125MHz,接收端將此125MHz經由鎖相迴路倍頻至500MHz,這樣一來資料和時脈為同步狀態,來自同一個時脈源,可避免亞穩態發生。

逐步建構專屬模組

較複雜的模組透過操作精靈比較方便且快速,但若能了解元件的特性,方能有效縮短除錯時間,並建構屬於自己的模組,特別是新的FPGA架構中設計有可移植性,能將一組設計在不同系列中互相移植尋找最低成本的晶片且無須重新設計。然而,若要建構關鍵技術,更不可不知元件特性。

本文僅以專案所接觸、使用的方式做介紹,讀者可在官方網站上找到許多免費的參考設計,都是官方驗證過,相信在未來專案評估或運作時,是很好的資料來源,而平時,可用以參考他人設計風格、思考方式,也是個不錯的學習管道。

(本文作者任職於資策會智通所)