隨著數位運算元件核心電壓降低,為確保正常運行,電源供應的精準度變得至關重要。高精度視窗電壓監控器能夠最大化電源輸出,確保元件在有效的工作電壓範圍內運行。惟設計電源時需特別關注核心電壓和電源容差,以避免因電壓漂移導致的元件故障。

技術發展日新月異,為因應功耗和散熱挑戰,提升應用性能,FPGA、處理器、DSP和ASIC等數位運算元件的核心電壓逐漸降低。同時這也導致核心電源容差變得更小,工作電壓範圍變窄。大多數開關穩壓器並非完美無缺,但核心電壓降低的趨勢要求電源供應必須非常精準,以確保電路正常運行[1]。視窗電壓監控器有助於確保元件在適當的核心電壓水準下運行,但臨界值精度是使可用電源視窗最大化的重要因素[2]。

本文討論如何利用高精度視窗電壓監控器來使電源輸出最大化。透過改善元件核心電壓的可用電源視窗,確保元件在有效的工作電源範圍內運行。

隨著人們對電池供電的可攜式小工具和元件的需求量大增,數位電路的能耗成為一個重要的關注點。運算和處理變得越來越複雜,需要速度更快的元件,例如現場可編程閘極陣列(FPGA)和其他處理晶片。複雜的處理需要更高的功率,這反過來又會導致高速運行的晶片發熱。如圖1所示,元件尺寸的製程技術正微縮至奈米級別,為了優化元件的處理速度並延長使用壽命,必須相應地降低其工作電壓[3]。

圖1 隨著技術製程的進步,積體電路的電源電壓越來越低[3]

圖1 隨著技術製程的進步,積體電路的電源電壓越來越低[3]

技術製程優化趨勢使得市場對高精度電源的需求變得越來越迫切。如果忽視電源的實際性能,就可能為系統性能帶來風險。大多數穩壓器都不夠精準,如果核心電壓低於工作要求電壓,處理元件如FPGA可能會因錯誤而發生故障。在連續操作情況下,如果核心電壓漂移到最大工作要求電壓以上,FPGA可能會被損壞,邏輯中可能產生保持時間故障。這些風險可能與負載條件、工作溫度和裝置老化有關[1]。雖然本文中的大多數示例提到了FPGA,但同樣的原理也適用於其他運算和處理元件。

因應容差

設計和監控運算與處理晶片所用的電源時,需要特別關注容差問題,因為從不同角度來看的話,容差的處理方式可能有所不同。在本文的討論中,我們在以下章節定義每種容差。

核心電壓容差

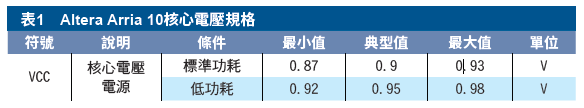

核心電壓容差是運算元件核心電源規格。表1以Altera Arria 10 FPGA為例,顯示了其核心電壓規格。最小值和最大值範圍相對於標稱值有±3.3%的容差。以低於標準最小值或高於最大值的電壓操作此元件將會導致性能問題。為了實現最佳性能和低功耗運行,須遵循更嚴格的容差規定。

表1 Altera Arria 10核心電壓規格

表1 Altera Arria 10核心電壓規格

電源容差

電源容差是電源的輸出偏差或輸出穩壓性能。要獲得嚴格的電源容差,需要由專家精心設計。然而,電源容差可能會受到元件老化等外部因素的影響,隨時間發生變化。在應用中,此電源容差應在核心電壓容差範圍內。電源輸出的任何操作都可能為處理和運算元件(如FPGA)帶來問題。具有一定標稱容差的穩壓器,其實際輸出電壓未必恰好是穩壓規格的中間值,而是在穩壓範圍以內。原因可能包括:回饋迴路中使用的電阻標準值本身存在一定的容差,進而帶來了直流誤差;基準電壓的穩健性;以及回饋迴路補償的優化。假設一個FPGA的核心電壓由開關穩壓器供應。該開關轉換器的標稱容差為±2%,運行時可能處於4%視窗內的任何位置。例如可能低於標稱值,但仍在-2%以內,進而導致FPGA存在時序風險。或者可能接近+2%的上限,這仍然可以滿足FPGA要求,但不是最佳運行條件,會浪費大量電力[1]。如果不進行監控,元件最終可能會在建議的電壓水準之外運行,這可能導致更嚴重的問題,必須避免此種情況的發生。

視窗電源監控器容差

視窗電源監控器容差或稱容差視窗以相對於標稱值的百分比設定欠壓(UV)和過壓(OV)臨界值。對於標稱電壓值為1V、容差視窗為±3%的視窗電壓監控器,UV臨界值設定為1V×0.97,OV臨界值設定為1V×1.03。然而,這些臨界值(UV和OV)本身也具有容差,稱為臨界值精度。

使用視窗電壓監控器

視窗電壓監控器透過設定UV和OV臨界值來確保元件在其額定電壓範圍內運行。如果電源電壓超出這些設定的限值,其會發出重定輸出訊號,有助於防止系統出錯,保護電子元件免受損壞。圖2中的時序圖顯示了當監測到的電壓低於UV臨界值或超過OV臨界值時如何提供復位輸出。視窗電壓監控器具有多種架構方案可以用來設定UV和OV臨界值,並根據實際需要選擇工作容差,進而達到最佳運行狀態[2]。

圖2 時序圖,顯示了UV和OV情況下的重定輸出

圖2 時序圖,顯示了UV和OV情況下的重定輸出

然而,選擇視窗監控器並採用最佳使用方式並不容易。適當的容差視窗需要從眾多可用方案中仔細挑選。此外,UV和OV的復位臨界值本身也有精度規格。臨界值精度通常以百分比表示實際臨界值與運算臨界值或目標重定臨界值的一致程度,其由積體電路(IC)設計中的電阻分壓器和帶隙電路決定[4]。基準電壓和電阻越穩健,所能達到的精度就越高。圖3為視窗電壓監控器的容差視窗和臨界值精度。UV和OV的實際臨界值分別為UV_TH和OV_TH,其可以在最小值和最大值的精度規格範圍內變化。

圖3 欠壓和過壓臨界值變化及其精度規格

圖3 欠壓和過壓臨界值變化及其精度規格

電源性能預算通常在系統設計期間確定。對於容差或工作規格為±3%的FPGA核心電壓,可以將±1%分配給電源直流穩壓誤差,±1%分配給輸出漣波電壓,另外±1%分配給瞬態響應。如果使用精度較差的電源,其穩壓誤差有±2%,那麼留給瞬變響應的餘量就會更少。當直接供電時,瞬變響應餘量不足可能導致瞬態電壓超出核心電壓規格視窗,進而提高元件發生故障的風險。當發生此種情況時,可以利用視窗電壓監控器將FPGA安全地置於重定模式,進而避免出錯。

選擇合適的容差視窗

使用視窗電壓監控器的常見困難是如何設定和選擇適當的容差視窗。使用者傾向於選擇容差與核心電壓要求相同的視窗電壓監控器。例如,對於容差為±3%的核心電壓要求,可使用容差視窗為±3%的視窗電壓監控器。受臨界值精度影響,選擇與FPGA核心電壓工作要求相同的容差時,在最大過壓臨界值OV_TH(最大值)和最小欠壓臨界值UV_TH(最小值)附近的任何電壓值都可能會觸發重設輸出,進而導致系統出現故障。在圖4a中,若不考慮臨界值精度,受監控的電源可能會超出核心電壓容差範圍,且在其可能的實際工作臨界值下,電源監控器可能無法檢測到異常情況。這個超出±3%的電源將供電給微處理器的核心,因此需要選擇更合適的容差視窗。為了避免此類情況的風險,OV_TH(最大值)和UV_TH(最小值)應設定在核心電壓的±3%容差要求範圍內。然而,由於需要保證精度,可用電源視窗的一部分會被占用,導致電源工作視窗變小,如圖4b所示。

圖4 視窗電壓監控器容差設定:(a)與核心電壓容差相同;(b)在核心電壓容差範圍內

圖4 視窗電壓監控器容差設定:(a)與核心電壓容差相同;(b)在核心電壓容差範圍內

臨界值精度的影響

考慮使用兩個臨界值精度不同的視窗電壓監控器來監控同一核心電壓電源。精度較高的監控器的實際UV和OV臨界值相對於預期UV和OV臨界值的偏差,比精度較低的監控器要小。從圖5a可以看出,較低的臨界值精度會導致電源視窗變窄,因為當核心電源電壓處於UV和OV監控範圍內的任何位置時,重定輸出訊號都會被觸發。在電源精度低、穩壓效果差的應用中,這可能導致系統變得更加敏感,容易發生振盪。相反的,高臨界值精度會拓寬可用電源視窗來確保電源穩定工作,進而提升系統性能,如圖5b所示。

圖5 允許的電源視窗和重定回應:(a)低臨界值精度;(b)高臨界值精度

圖5 允許的電源視窗和重定回應:(a)低臨界值精度;(b)高臨界值精度

圖6顯示了一個例子,使用兩個臨界值精度不同的視窗電壓監控器監控±5%容差規格的2.5V核心電壓。本例中使用的容差視窗並非實際產品提供的選項,而是為了考量臨界值精度而選定的。對於圖6a和6b,所用的視窗電壓監控器的臨界值精度分別為±1.5%和±0.3%。使用±1.5%的臨界值精度時,避免在圖6a所示的故障區域內運行的最佳容差視窗為±3.5%,因此電源工作視窗為100mV。使用±0.3%的臨界值精度時,令電源輸出最大化的最佳容差視窗為±4.7%,且不存在任何故障風險。設定這些值將提供220mV的電源工作視窗。精度上的此種差異使工作電源視窗擴大了一倍以上,進而有效提升電源性能。

圖6 有效工作電源視窗:(a)±1.5%臨界值精度;(b)±0.3%臨界值精度

圖6 有效工作電源視窗:(a)±1.5%臨界值精度;(b)±0.3%臨界值精度

上述運算是透過視窗電壓監控器完成的,該工具有助於輕鬆理解和視覺化視窗電壓監控器中的不同參數。使用者還可以檢查元件規格是否符合設計要求。

為因應越來越低的核心電壓要求,視窗電壓監控器的架構和性能不斷改善,目前的臨界值精度達±1.5%至±0.3%。為了提升精度,可以使用經工廠微調的標稱監控電壓和容差視窗的視窗電壓監控器[2,5]。MAX16193為一款精度為±0.3%的雙通道監控電路。截至2024年時,該元件是在不同溫度下臨界值精度最高的視窗電壓監控器。可提供各種經工廠微調的容差視窗(±2%到±5%),以適應工業和汽車應用的不同電源電壓和容差要求。在圖7所示的典型應用電路中,輸入通道1(IN1)以±0.3%的精度監控0.6V至0.9V臨界值範圍內的低核心電壓軌,而輸入通道2(IN2)則以±0.3%的精度監控0.9V至3.3V臨界值範圍內的較高系統電源軌。

圖7 視窗電源監控器MAX16193的典型應用電路,該元件在整個溫度範圍內都具有非常高的臨界值精度,能夠監控MCU的核心和輸入/輸出電源電壓

圖7 視窗電源監控器MAX16193的典型應用電路,該元件在整個溫度範圍內都具有非常高的臨界值精度,能夠監控MCU的核心和輸入/輸出電源電壓

MAX16193的臨界值精度在整個工作溫度範圍(-40~125℃)內均保持穩定。圖8a和圖8b表明,對於IN1和IN2兩個輸入,該元件的高臨界值精度在不同溫度下均表現卓越。與其他電壓監控器僅在特定範圍內表現出最優性能不同,該元件在工作溫度範圍內都能保證高精度。

圖8 (a)IN1和(b)IN2的UV和OV臨界值精度隨溫度的變化曲線

圖8 (a)IN1和(b)IN2的UV和OV臨界值精度隨溫度的變化曲線

為了跟上速度、功耗優化的需求以及製程技術發展的步伐,元件的核心電壓必須越來越低,容差也越來越嚴格。視窗電壓監控器有助於防止這些元件出現嚴重問題。然而,臨界值精度有助確保元件在規格視窗內正常運行。視窗電壓監控器的高臨界值精度有助於改善工作電源視窗,進而有效提升電源性能,防止不必要的頻繁重設和系統振盪。

(本文作者皆任職於ADI,Noel Tenorio為產品應用經理;Camille Bianca Gomez為產品應用工程師)

參考文獻

1. Nathan Enger。“Care and Feeding of FPGA Power Supplies:A How and Why Guide to Success”。《類比對話》,第52卷第11期,2018年11月。

2. Camille Bianca Gomez 和Noel Tenorio。“Optimize Your System Design with the Right Window Voltage Supervisor”。《類比對話》,第58卷第3期,2024年9月。

3. Mohammed Mahaboob Basha、Kota Venkata Ramanaiah和Palakolanu Ramana Reddy。“Design of Near Threshold 10T-Full Subtractor Circuit for Energy Efficient Signal Processing Applications”。International Journal of Image, Graphics and Signal Processing,2017年12月。

4. Noel Tenorio。“How Voltage Supervisors Address Power Supply Noise and Glitches”。《類比對話》,第57卷第4期,2023年11月。

5. 「電壓監控器和電源監控器產品聚焦」。ADI。

6. 「讓產品正常運行——微處理器電源監控器以小封裝提供強大保障」。ADI,2001年11月。

7. Pinkesh Sachdev。「FPGA電源系統管理設計筆記」。ADI,2020年3月。

8. Caroline Hayes。“Designing Supply Voltage Supervision for Multirail Boards”。Electronic Specifier,2015年10月。