先進的16位元高速類比數位轉換器(Analog-to-Digital Converters, ADC)能提供極高的動態範圍與低失真的功能,以符合現今嚴格的無線通訊標準需求。當通訊接收器的發展趨勢傾向更靈活多元化的標準和多元化的載波,無線電波就需要較大的頻寬來進行數位化。同時,因為獨立頻道功率的降低以及同頻帶阻斷訊號的可能性增加,因此也需要更高的敏感度。基於這個原因,類比數位轉換器的雜訊與失真將是關鍵性的考量。

本文探討將類比數位轉換器整合於基地台(Basestation)應用時所面臨的效能限制挑戰,並會將討論的重點關注在轉換器的驅動和時脈(Clock)要求。針對這些挑戰,在此提出的解決方案是全新的中頻(Intermediate Frequency; IF)子系統設計,這個新的中頻子系統結合了美國國家半導體(NS)最新研發的ADC16DV160雙通道16位元160MSPS ADC、LMH6517 DVGA以及LMK04031B精準時脈調節器等元件所共同組成。

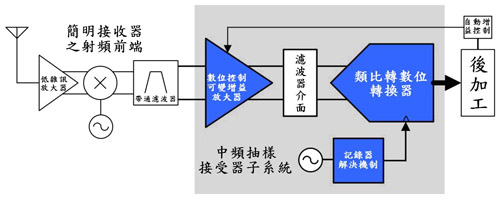

如圖1所示,針對基地台應用的高敏感度中頻取樣子系統,通常都包含高速類比數位轉換器、一個精準時脈解決方案,以及由數位控制可變動增益放大器(Digitally-controlled Variable Gain Amplifier, DVGA)這幾個元件。數位控制可變動增益放大器的增益,係經由自動增益控制(Automatic Gain-Control, AGC)迴路控制。在這個中頻取樣子系統中,數位控制可變動增益放大器,扮演類比數位轉換器的緩衝器和驅動器介面。

|

| 圖1 通訊接收器內中頻取樣子系統之示意圖。 |

除此之外,當輸入訊號很小時,數位控制可變動增益放大器可以阻擋增益,以減少類比數位轉換器雜訊的影響。而其中的時脈解決方案可為將資料轉換至數位格式提供一個低雜訊取樣時脈。

數位控制可變動增益放大器/ADC串聯挑戰大

當串聯數位控制可變動增益放大器與類比數位轉換器時,會面臨許多必須設法解決的挑戰,進而達到效能的最佳化。這些挑戰包括:因採用數位控制可變動增益放大器而產生的失真問題必須最小化,將數位控制可變動增益放大器至類比數位轉換器介面間訊號完整度最大化,讓管線式類比數位轉換器輸入端的切換雜訊最小化,讓數位控制可變動增益放大器的雜訊最小化,讓類比數位轉換器的輸入的動態範圍能夠充分應用。

前三個挑戰是與子系統的失真現象相關,以及訊號路徑的無雜訊動態範圍(Spurious-Free Dynamic Range, SFDR)限制的問題。數位控制可變動增益放大器的調和失真,以及來自於類比數位轉換器輸入切換產生的訊號相關電荷突波回授、介面阻抗的不匹配與訊號的反射,都可能會造成頻譜中出現錯誤資訊。

第四與第五個挑戰主要在於子系統的訊噪比(SNR)效能。來自數位控制可變動增益放大器過多的雜訊,除了會降低雜訊外,也將無法使用轉換器的完整輸入範圍,讓訊號雜訊比直接減少,這也可以被視為是一種電力的浪費。而上述的五種挑戰因為彼此間都有連帶關係,所以會互相影響。

針對上述這些問題,大部分的解決方案都是選用一個高效能的數位控制可變動增益放大器,然後在數位控制可變動增益放大器與類比數位轉換器之間插入一個阻抗匹配的差動高階帶通濾波器,來補償數位控制可變動增益放大器的非理想問題。其中的濾波器減少了數位控制可變動增益放大器的調和失真、限制數位控制可變動增益放大器的雜訊頻寬,以及讓類比數位轉換器介面中與阻抗相關訊號完整性問題趨於最小化。

高階濾波器的目的為阻抗匹配,但在實際的應用上會造成介質損耗,且對於元件不匹配與電路板的寄生效應非常敏感。由於濾波器的高低階與損耗間的關係,造成數位控制可變動增益放大器與類比數位轉換器之間的介面必須採取折衷的設計。可以利用增加數位控制可變動增益放大器的輸出訊號擺幅,來補償帶通濾波器的損耗。當訊號接近數位控制可變動增益放大器的功率軌道時,會降低數位控制可變動增益放大器的調和失真以及第三階輸出截止點(Output Intercept Point, OIP3)。

同時實現高品質雜訊/失真特性

另外,帶通濾波器的共振特性無法有效降低來自於典型的管線類比數位轉換器在輸入切換充電時其訊號相關電荷突破回授,而其現象對於大型振幅訊號更是明顯。經由選擇適當的濾波器架構以及平衡之前的那些折衷問題後,高品質雜訊與失真的特性將可以同時達成。

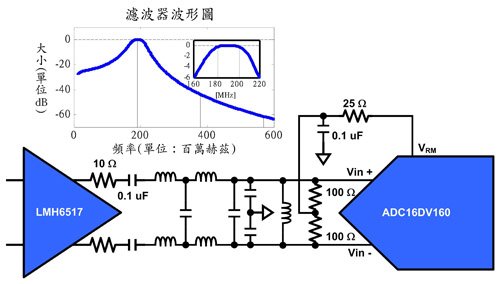

新的SP16160CH1RB子系統中的非對稱T-match帶通濾波器(Bandpass Filter)設計,就是如上述的濾波器介面解決方案。如圖2所示,這種濾波器可以為一般中頻頻帶提供第四階高頻衰減變為40dB,並且讓第二次諧波(H2)在衰減小於0.5dB帶通漣波的情況下,使LC T-match可以提供一個阻抗轉換。這個阻抗轉換可以維持數位控制可變動增益放大器的輸入源電阻(用來維持數位控制可變動增益放大器的穩定性)與負載電阻(對類比數位轉換器提供低阻抗輸入的一般狀態參考)間阻抗匹配時,僅造成很小的帶通衰減(Passband Attenuation)。

|

| 圖2 數位控制可變動增益放大器與類比數位轉換器間的帶通濾波器介面。 |

這個架構對於印刷電路板(PCB)寄生效應並不敏感,而且實際上是可行的。這是因為只需要分路電容元件與大多數串聯的電感就可以達成。類比數位轉換器的電荷突波回授問題,可藉由經驗法則選擇濾波器中分布於差動與一般模式導向的LC儲能電路電容來達到緩和效果。在這個架構設計中,帶通衰減現象可藉由降低來源電阻值,讓衰減從5dB改善到0dB左右。

雖然衰減現象的改善必須犧牲完美的阻抗匹配,但是讓數位控制可變動增益放大器在較小的輸出振幅下達到類比數位轉換器的完整規模參考狀態;而結果可以改善第三階互調失真效能,雖然無法與阻抗匹配,但仍然是相當值得的。

輸入時脈品質不易達成

對於大型輸入訊號來說,類比數位轉換器的輸入時脈品質對於限制該系統可達成訊噪比扮演著樞紐的角色。時脈邊緣的時基誤差會讓類比數位轉換器週期性的穩定採樣受到干擾,並且增加了訊號本身的雜訊。

下列的方程式代表著類比數位轉換器因為時基誤差影響而能夠達成的最大訊噪比,其中fin代表的是輸入訊號頻率,σJ 代表均方根時基誤差值,a代表以dB為單位的輸入訊號振幅(相對於完整規格dBFS),而其數值越小代表有越大的負數值。

|

| 方程式1 |

從方程式1中可以看出三個重點:首先,在越高頻的狀態下,時基誤差會降低更多的訊噪比;其次,對於越大的訊號,時基誤差的訊噪比限制效應會更加嚴重;另一則是訊噪比可藉由降低總時基誤差來得到改善。

這些觀察所得的結果,對於基地台接收器的應用來說非常重要,因為這是來自於頻率約在100M~250MHz間使用於中頻採樣接受器的高中頻系統。儘管在該頻率頻道中的功率能夠很小,但在接收路徑中的類比數位轉換器必須同時對大型訊號進行數位化,因此需要非常高的敏感度(高SNR與SFDR)。從以上的方程式中可以看出,高輸入頻率與大型訊號讓時脈時基誤差的現象更加惡化。舉例來說,對於一個在頻率190MHz的-1dBFS單音輸入訊號要達到72dBFS的訊噪比,須要用均方根時基誤差來維持在236FS之下。時脈效能要達到如此的品質並不容易。

為了降低時脈整體的時基誤差,必須先了解到要降低的是時脈雜訊的光譜(Spectral)內容以及相位雜訊(Phase Noise)的特定光譜範圍。訊號源太靠近而產生的相位雜訊,是一種從時脈基音延伸頻率至20MHz的裙狀雜訊,而且深受產生時脈的時脈電路迴路特性也被稱為相位鎖定迴路(PLL)所影響。「寬頻」相位雜訊擁有一個平坦的光譜特徵,此光譜頻寬會無窮延伸,且通常會被時脈緩衝器雜訊(Clock Buffer Noise)所影響。

SP16160CH1RB子系統板使這兩種相位雜訊被分開來。藉由使用LMK04031B精準時脈調節器與一組Crystek參考石英晶體振盪器及電壓控制石英晶體振盪器間的結合,使得低靠近相位雜訊(Low Close-in Phase Noise)能夠達成。LMK04031B中的串聯相位鎖定迴路提供兩個步驟來消除目標的時基誤差。

第一個步驟是藉由使用很低的相位鎖定迴路頻寬來降低參考的時脈雜訊,而第二個步驟是藉由使用一組內部低雜訊壓控振盪器與高速相位/頻率偵測器進一步降低靠近相位雜訊的上頻帶。LMK04031B時脈的解決方案同時也可以將61.44MHz的參考時脈頻率倍數化,以便為類比數位轉換器產生頻率153.6MHz的時脈。互補式金屬氧化物半導體(CMOS)時脈的靠近均方根時基誤差小於從載波結合頻率20MHz的200FS。

時脈的寬頻雜訊因為具有寬頻的特性而更顯得麻煩。對於類比數位轉換器而言,為了提供一個非常尖銳的取樣邊際時脈,時脈訊號的頻寬必須很大,以便產生一個很大的雜訊頻寬,此雜訊將結合到訊號中且折衷返回第一奈奎斯特區(Nyquist Zone),藉此降低系統的訊噪比。

藉由降低時脈輸入的頻寬或是時脈訊號本身來降低雜訊頻寬的方式有一個很嚴重的缺點,它會讓振幅調變(AM)與相位調變(PM)間的雜訊轉換過程的電路變得更加敏感。這是由於降低取樣邊際(Sampling Edge)的斜率(Slope),這將會導致產生更糟的雜訊。

SAW濾波器/CMOS緩衝器有效減少寬頻雜訊

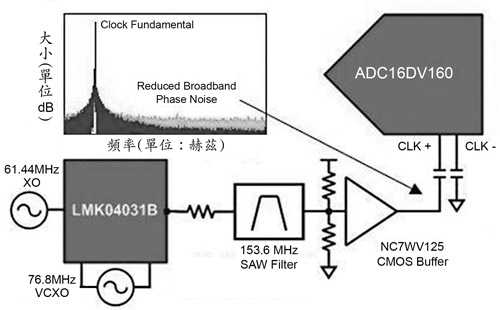

如圖3所示,SP16160CH1RB使用了表面聲波(Surface Acoustic Wave, SAW)濾波器及CMOS緩衝器,這是一個能夠有效減少寬頻雜訊的解決方案。LMK04031B中的時脈可以藉由一組Vectron表面聲波儀來進行濾波,使得時脈的光譜內容淨化並且降低寬頻雜訊。而快捷(Fairchild)NC7WV125 CMOS緩衝器在沒有外加大量雜訊的狀態下能夠提升邊際率(Edge Rate)銳化。經由對LMK04031B時脈進行濾波以及再次緩衝的方式,可以用CMOS緩衝器來取代LMK04031B的寬頻雜訊,同時將寬頻雜訊密度從-162dBc/Hz降至-168dBc/Hz。相對於無濾波與無緩衝的方法,SP16160CH1RB子系統板中的解決方案可以獲得2.5dB的訊噪比改善。

|

| 圖3 低時基誤差時脈的解決方案 |

SP16160CH1RB子系統在設計上使用了一組在中頻192MHz為中心頻率達20MHz的輸入頻寬與一組153.6MSPS的取樣頻率。在面對基地台應用中高速數據轉換的挑戰時,子系統的設計使訊噪比優於73.5dBFS、讓小於-10dBFS的單音無雜訊動態範圍(SFDR)優於93dBFS以及一個擁有70.7dBFS的訊噪比以及使-1dBFS音的無雜訊動態範圍優於80dBFS。

在雙音測試時,同頻帶訊號傳輸的第三階調變產品,在頻率1MHz的混合訊號並結合-1dBFS峰值對峰值振幅(Peak-to-peak Amplitude)時,能小於-85dBFS。

在無線基地台應用裝置中,驅動並時脈化16位元類比數位轉換器是非常關鍵的功能,因為它能產生或破壞效能規格。對於實現這些功能的數位控制可變動增益放大器與時脈電路的選擇必須格外留意,就如同選擇適當的介面,才能讓系統動態範圍達成最大化的目標。

SP16160CH1RB子系統的設計,展現高度線性與低雜訊數位控制可變動增益放大器驅動器的解決方案,以及多載波中頻取樣子系統中16位元類比數位轉換器低時基誤差時脈解決方案。

(本文作者任職於美國國家半導體)