IEEE 802.3在1983年將乙太網路標準化後,已成為世界上電腦通訊的實際標準。從3Mbit/s的銅纜系統發展成可靠性更高、成本更低的100Mbit/s非遮罩雙絞線(Cat5 UTP)系統;而1Gbit/s、10Gbit/s的乙太網路系統也都陸續出爐,加入服務行列。

乙太網路的應用範圍、實用性和易用性,及工廠系統和公司網路的整合,促使工業開發人員採用乙太網路架構的工業聯網解決方案,與相容工業現場匯流排通訊方案,甚至能夠替代它。目前乙太網路架構的工業通訊協定中,每種通訊協定都有其優缺點,且部分通訊協定都已標準化並呈現「開放」架構,讓任何開發人員都可實施這些通訊協定,因此開放的通訊協定將廣泛被業界採用,從表1可了解乙太網路的重要發展。

| 表1 乙太網路標準的發展 |

| 年分 |

標準 |

總結 |

| 1983 |

IEEE 802.3 |

基本乙太網路標準 |

| 1985 |

IEEE 802.3a |

10Base2乙太網路標準 |

| 1990 |

IEEE 802.3i |

10Base-T 10-Mbit/s乙太網路標準 |

| 1995 |

IEEE 802.3u |

100Base-TX/T4/FX 100Mbit/s快速乙太網路 |

| 1997 |

IEEE 802.3x |

全雙工乙太網路標準 |

| 1998 |

IEEE 802.3y |

UTP上的100Base-T2快速乙太網路標準 |

| 1999 |

IEEE 802.3ab |

1000Base-T 1 Gbit/s |

| 2003 |

IEEE 802.3af |

乙太網路供電 |

| 2006 |

IEEE 802.3an |

10GBase-T 10 Gbit/s |

許多解決方案僅簡單的在標準乙太網路資料封包中,封裝現場匯流排或應用資料,因此,僅須透過乙太網路標準即可達成;不過,很多工業乙太網路的通訊協定需額外的專業軟體,且大部分高性能通訊協定還須訂製硬體,因此開發並維護支援多種通訊協定的解決方案成為阻礙。

工業設備生產廠商須找到有效的途徑,盡可能支援多種的工業乙太網路通訊協定以提高競爭力,才能迅速適應通訊協定的變化,支援新的通訊協定;因此面對數量多且持續發展的通訊協定中,可藉由技術改進基本乙太網路標準。

滿足市場需求 通用方案浮上檯面

開發一種新解決方案支援多種通訊協定其實很簡單,只須將每塊電路板針對一種通訊協定建立一系列外插式電路板。但是隨著市場上標準的增加及新標準不斷發展,新解決方案如何達到最佳效果,並迅速支援新功能和其他通訊協定,以及採用乙太網路標準的硬體,須開發的通訊協定軟體,在所選用的處理器中運行須花費的時間,CPU有足夠的能力執行應用程式和通訊協定,都是討論的重點。

當工業乙太網路欲使用新的ASIC/ASSP元件時,就必須開發電路板,這將帶來成本及運作時間的問題。當乙太網路通訊協定進行更新時,就須要開發新的ASIC /ASSP元件,甚至多次開發電路板,以同時支援原本和新的通訊協定。隨著通訊協定的迅速發展,元件將出現過時問題,因此依靠ASIC/ASSSP元件會產生供應問題,而這類解決方案價格昂貴,且難以提供支援新的功能。

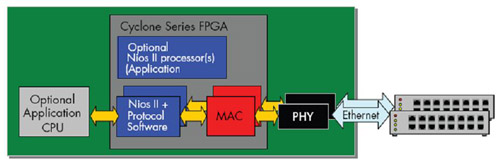

不過所有問題都可透過FPGA元件,實現工業乙太網路介面進行解決(圖1)。FPGA的關鍵優勢在於容易重新配置,就開發一塊電路板而言,任何時候都可針對工業乙太網路對硬體進行編程,不論是產品上市前或成品誕生後都可執行,若需要不同的通訊協定,或客戶修改了訂單,都只須對FPGA進行重新編程,利用FPGA配置檔在短短幾秒內就可完成。這類多重標準解決方案大大降低了開發成本,減少了庫存和供應鏈問題。為FPGA建立新的配置檔可能須要開發新的軟體或硬體,不過利用相關開發工具及現成的IP,在幾個星期內就可輕鬆完成。

|

| 圖1 採用FPGA架構的二通道普通工業乙太網路系統 |

結合乙太網路的收發器或稱實體(PHY)層後,FPGA能夠實現乙太網路介面所需的所有功能。PHY和電路板電路處理實體介面,FPGA中的配置邏輯管理媒介控制(MAC)層硬體功能;透過軟體實現更高層的功能,然後配置到FPGA邏輯處理器內部核心中執行這些軟體,將很容易實現現有應用程式處理器和FPGA之間的通訊通道,這是因為FPGA邏輯具有可編程能力,I/O接腳支援多種標準及大量的現成介面IP。一般情況下,處理器中的現有介面,如I

2C、SPI與某些其他的區域平行匯流排等,或者系統如PCI、PCI Express、CANopen等,都可以用於和FPGA進行通訊。這種方法有許多優點,它縮短了運算時間,且對於現有處理器上執行的應用軟體更動很小,這不但將系統軟體狀態保持不變,且提供了更多的處理資源,實現高性能工業乙太網路的堆疊處理。

FPGA硬體為可編程,因此可建立含兩個以上軟式核心微處理器的系統,於FPGA中整合應用軟體處理功能。這類系統整合的優點在於元件減少數量,降低了成本和功耗,此外,FPGA有較長的元件生命週期,能夠輕鬆過渡到新一代元件,且採用IP架構的設計完全不會出現過時的問題。運算量較大的功能可以在FPGA硬體中實現,而不必採用軟體,因此,FPGA還能加速系統性能,具有性能更好、時鐘速率更低、功率消耗更低的優點。對於工業乙太網路,FPGA硬體設計還提供集線器或類似的硬體,以加速乙太網路通訊。

FPGA不但能夠卸載處理器應用任務,於FPGA邏輯中實現硬體,而且還能充分實現新系統介面,包括簡單通訊介面如UARTS、平行I/O等,並支援新的記憶體標準如DDR2/3等複雜特性,及最新的通訊技術如藍牙(Bluetooth)、超高速乙太網路(GbE)、PCI Express等。

FPGA架構的硬體設計

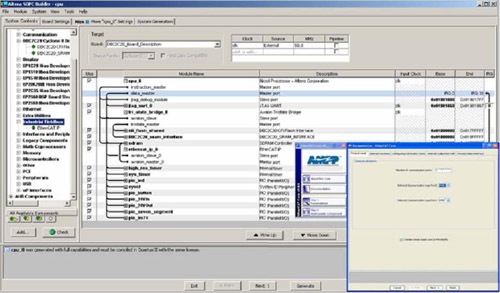

進行處理器和乙太網路MAC硬體設計,表面上看起來相當困難,但是由於有可編程單晶片系統(SOPC) Builder工具及預先建構的處理器和乙太網路MAC IP元件,實際上是相對簡單的任務。SOPC Builder目前已整合於Quartus II開發環境中,經過專門設計可輕鬆採用IP架構的SOPC進行設計。開發人員利用圖形使用者介面(GUI)而不是HDL編碼來設計系統;SOPC Builder自動加速實現IP系統的配置、整合和產生。在工具GUI(圖2)的螢幕畫面顯示中,左側視窗中列出了可用的IP,若須要在當前系統中加入IP元件,設計人員只須進行雙次點選IP模組即可。

|

| 圖2 SOPC Builder工具的螢幕畫面顯示 |

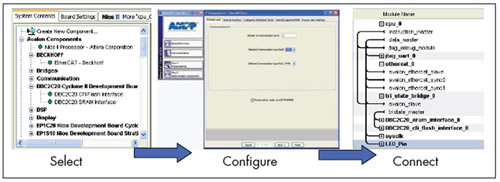

一旦選擇了某一IP模組,配置精靈可協助選擇合適的選項,完成後右側視窗面板顯示當前系統設計中已經配置的IP元件,就可以修改元件基本位址或者中斷層級,利用GUI改變IP元件之間的連接,更改系統互聯架構,上述過程能夠迅速實現模組化系統和最佳系統的設計(圖3),而視窗底部也會顯示設計錯誤的訊息,設計人員將很容易發現並改正問題,如位址衝突或者不正確的元件連接等。

|

| 圖3 利用SOPC Builder選擇、配置並整合硬體IP,建立工業乙太網路系統。 |

一旦完成了系統設計,設計人員點選Generate按鈕後,工具就會產生建構工作系統所需的所有HDL。由於IP經過預先建構,並由供應商進行測試,系統互聯會自動產生,透過很少的IP就可以實現正確性的結構設計。系統一旦產生,將在Quartus II原理圖編輯器中顯示為一個設計模組,對於大部分SOPC Builder產生的系統,硬體合成只是一個簡單的按鈕操作,將建立可以下載到FPGA元件中的配置檔。

以後若需要新的設計,或者對設計進行更改,設計人員只須打開SOPC Builder工具透過GUI修改設計,重新產生系統,在Quartus II軟體中重新合成,建立另一配置檔。這表示購買所需的硬體IP,將其放到現有的系統設計中並重新產生,就能建立新的工業乙太網路通訊協定硬體設計,最後點選重新進行合成,很快就能將硬體建立完成。

Nios II處理器執行軟體通訊協定

在支援乙太網路的嵌入式系統中,處理器提供高層功能如TCP、UDP等,可藉由免授權32位元RISC Nios II處理器進行,處理器有三種2進位相容型號,每一型號都針對不同的體積和性能比進行最佳化設計(表2),如Nios II/f針對高性能,Nios II/e的體積最小,Nios II/s在體積和性能上已達到均衡。由於Nios II處理器以SOPC Builder IP元件進行實現,因此很容易建立採用處理器架構的系統,包含了乙太網路MAC IP、大量的其他周邊組件,甚至多個Nios II處理器。利用SOPC Builder GUI,可迅速並輕鬆建構Nios II處理器系統,滿足設計人員的需求,甚至針對不同的應用建立不同版本的系統。

| 表2 Nios II處理器的時鐘速率、性能和邏輯資源占用 |

| 處理器 |

Cyclone III元件 |

Stratix III元件 |

| 時鐘速率 |

DMIPS |

LE |

時鐘速率(MHz) |

DMIPS |

LE |

| Nios II/f |

165 |

165 |

1,800 |

265 |

300 |

1,100 |

| Nios II/s |

135 |

70 |

1,150 |

200 |

130 |

770 |

| Nios II/e |

190 |

17 |

580 |

320 |

50 |

530 |

SOPC Builder可以直接使用Nios II處理器,並與Quartus II軟體提供的免費IP相容。這些IP包括標準處理器周邊功能模組,如UART、PIO、記憶體控制器等及大量IP元件,如乙太網路MAC、CAN、USB、PCI、PCI Express、FFT、FIRDSP、視訊處理等。在功能強大的Nios II軟體發展環境中,由自動整合到軟體建構系統中的Nios II驅動器實現這些元件,此環境採用開發人員熟悉的Eclipse和GNU架構,支援C語言和組合語言開發。

利用軟體IP啟動靈活設計

如表3所示,目前已有七種不同工業乙太網路通訊協定可以使用的商用IP套件,硬體IP一般封裝為SOPC Builder元件,它包括MAC及其他需要的邏輯;軟體IP則用於以C語言針對Nios II處理器編寫的函式庫或軟體API進行實現,有的供應商提供預先建構的FPGA配置,使設計人員使用FPGA元件與使用現成的ASIC/ASSP元件同樣方便。

表3 工業乙太網路通訊協定FPGA IP供應商 |

| 通訊協定 |

供應商 |

大概週期時間 |

| Modbus IDA |

IXXT |

200ms~10ms+ |

| EtherNet/IP |

IXXT |

200ms~10ms+ |

| PROFINET RT |

IXXT |

10ms~1ms+ |

| ETHERNET Powerlink |

IXXT |

<1ms |

| B&R |

| IEEE 1588 |

IXXT |

─ |

| SERCOS III |

SERCOS International |

<1ms |

| Automata GmbH |

| VARAN |

Sigmatek GmbH |

<1ms |

| EtherCAT |

Beckhoff |

<1ms |

| IXXAT |

低成本Cyclone III FPGA針對成本敏感的大批量、低功耗應用而設計,是工業乙太網路應用的最佳元件選擇,能提供工業級型號。這一系列含有八個型號、八種不同的元件,封裝含有從5K到120K的LE,用戶I/O接腳數分布在八十二~五百三十五個之間。Cyclone III元件提供4Mbit/s的嵌入式記憶體、二百八十八個嵌入式18×18位元乘法器、專用外部記憶體介面電路、鎖相迴路(PLL),以及高速差分I/O。擁有5,136個LE,即使最小的Cyclone III元件也能夠輕鬆實現Nios II處理器和其他的IP元件,支援工業乙太網路連接。

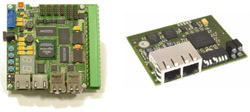

對於大部分工程,啟動工程最簡單的方法是購買針對應用的開發套件,將非常適合實現與通訊協定無關的工業乙太網路系統。電路板有兩個RJ-45乙太網路插頭,由每一個和FPGA連接的乙太網路PHY進行驅動,利用此一電路板,設計人員實現工業乙太網路標準時須要處理的只有上層軟體、二層硬體MAC IP與Nios II處理器。很多工業乙太網路通訊協定參考設計在電路板上已經過驗證,電路板還包括支援高速通訊及驅動LCD顯示器CAN、USB、UART、LVDS介面的收發器。

|

| 圖4 DBC2C20電路板和IXXAT工業乙太網路模組 |

在歐洲,IXXAT GmbH公司提供採用Cyclone架構的I/O模組(圖4),它的兩個RJ-45連接器可用於開發採用FPGA架構的工業乙太網路解決方案,包括Ethernet/IP、PROFINET、Modbus TCP、EtherCAT和Ethernet Powerlink。Beckhoff提供採用Cyclone III FPGA架構的評估套件,利用EtherCAT IP的內部核心進行設計開發。

新工業乙太網路架構登場

工業市場的乙太網路技術有很多優點,預計該技術於5年內會有大幅成長。目前有很多工業乙太網路的通訊協定,每一通訊協定都有自己的獨到之處,因此乙太網路技術會不斷發展,推動了現有和新工業乙太網路解決方案的進展。1Gbit/s和10Gbit/s乙太網路技術及802.3標準的不斷改進,將實現更好的性能並提高可靠性。相對的,保密和安全通訊協定等其他工業領域也同時推動工業乙太網路標準的進展,這對工業設備生產廠商而言是進一步的挑戰。.

低成本FPGA和軟式核心微處理器IP的出現,為工業乙太網路提供了高性能價格的可編程解決方案。在相同的基本硬體上,FPGA能支援採用乙太網路架構的工業通訊協定,具有可編程元件的系統整合、靈活性及不會過時等優點。可編程硬體、SOPC Builder和Nios II處理器相結合,使開發人員能輕鬆修改上層和底層乙太網路通訊協定,而不必改動實際硬體。隨著現有通訊協定的發展及新通訊協定的出現,擁有價格優勢比工業乙太網路通訊協定解決方案更顯重要,利用FPGA實現工業乙太網路,已成為所有工業設備生產廠商可採用的方法之一。

(本文作者任職於Altera)