雖在各界的支持下,3D IC之未來發展頗受重視,更被視為摩爾定律告終時之救世主,但就時程而言,3D IC要在22奈米製程走到盡頭時才會真正崛起,加上半導體測試設備、設計工具與其他周邊環境並未到位,現在談3D IC的發展恐怕言之過早。

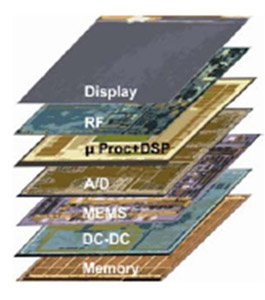

高度整合一向是晶片設計與製造業者的重頭戲,近期包括系統級封裝(SiP)、系統單晶片(SoC)等話題皆相當熱門。然在三維晶片(3D IC)(圖1)問世後,更因可大幅縮減內部連接路徑、提升晶片間傳輸速度、縮小尺寸,而顛覆了傳統的晶片整合技術。由於3D IC極具發展潛力,也吸引諸多業者先後投入,預計在2010年將可商品化。再加上工研院與美商應用材料(Applied Materials)攜手成立的3D IC實驗室即將於2010年中問世,更加推升市場熱度。

|

資料來源:工研院

圖1 3D IC之出現,可能顛覆現有晶片設計理念。 |

從立體封裝著手 3D IC話題升溫

簡單來說,3D IC是一種利用立體堆疊技術改善晶片體積、效能與成本之技術。其透過立體堆疊技術,可望打破既存數十年之摩爾定律(Moore's Law),並將晶片設計從二維平面走向三維空間。

摩爾定律受挑戰

眾所周知,摩爾定律指出,「晶片上可容納的電晶體數目,約每隔18個月便會增加一倍,性能也將提升一倍。」此定律蘊含的意義在於,若業者在相同面積的晶圓下生產同樣規格的晶片,隨著製程技術的進步,每隔18個月,IC產出量就可增加一倍。若進一步換算為成本,即每隔18個月可降低五成成本,平均每年成本可降低三成多。因此摩爾定律延伸之定義為「晶片技術每隔1年半推進一個世代。」且其更重要的意義在於,其將製程技術視為直線的方式向前推展,也就是說,只要製程演進,晶片產品便能持續降低成本、提升性能。

然而,摩爾定律在近年隨著製程技術一路演進,也受到更多挑戰。陸續有研究指出,隨著製程邁入22奈米或更先進的階段,由於建造先進製程之相關廠房、實驗室等成本與回報將無法獲得平衡,真正有財力與興趣投資的業者將大幅減少,因此摩爾定律也將不復存在。

而3D IC由於並非從製程本身出發,而是透過立體封裝技術打破平面設計之界線,因此在近期備受矚目,成為顛覆晶片設計之關鍵要素。

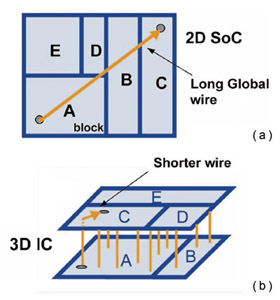

從圖2a可以看出,在二維的SoC時代,為了完成不同晶片間的介接,將需要較長的打線(Wire)。但若進入立體封裝時代(圖2b),不但可以縮減空間,更可節省打線,同時帶來更高的晶片運作效能。

|

圖2a 2D SoC之打線設計

圖2b 3D IC 之打線設計 |

事實上,若從1950年最早的單一電晶體開始算起,歷經60年的發展,今日晶片上之電晶體數目已經逼近十億大關,演進速度不可謂不快。然而,正因為電晶體數量的驚人成長,不但對晶片設計人員是沈重考驗,如何將其效能發揮到最大,也是所有半導體業界重視的話題。

市調單位/業者普遍看好

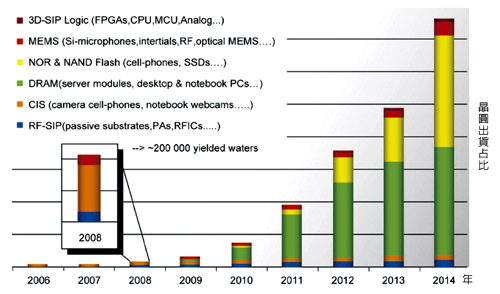

正因3D IC具備的多項優勢,近期不少市調單位均對相關市場之發展頗具信心(表1),如Yole便指出,3D IC出貨比重將自2014年大幅成長,其他業者也對3D IC之發展頗具信心,並吸引多家廠商陸續布局(表2)。

| 表1 各單位對3D IC 市場之預估 製表者:侯俊宇 |

| 單位 |

預估內容 |

| Aviza |

2012~2017年將有逾半晶片乃透過TSV 所製造 |

| 恩智浦 |

3D IC將在2012 年正式問世,並在2014年達到四百萬片出貨量 |

| 工研院 |

應用在3D IC上之SSD可望在2010~2012年大幅成長 |

| Yole |

2015年時逾25%之記憶體晶片將由3D-TSV所設計

2015年時近6% 的非記憶體晶片將由3D-TSV 所設計 |

| Prismark |

2010 年十可見到十四億顆3D封裝形式的IC |

| iSuppli |

2010 年3D IC市場市場總值約為33億美元

2014 年3D IC市場總值約有173億美元 |

資料來源:各單位,工研院整理

| 表2 近期各3D IC業者布局概況 製表者:侯俊宇 |

| 廠商型態 |

廠商名稱 |

主要應用產品及進度 |

| IDM |

爾必達 |

工業及消費性DRAM |

| 海力士 |

工業及消費性Flash 及DRAM |

| 飛思卡爾 |

工業射頻、消費性MEMS |

| IBM |

射頻、CMOS Image Sensor |

| 英特爾 |

邏輯IC |

| 瑞薩 |

邏輯IC |

| 索尼 |

邏輯IC |

| 美光 |

Flash、DRAM、車用CMOS Image Sensor |

| 恩益禧 |

DRAM |

| 恩智浦 |

射頻、消費性MEMS |

| 三星 |

通訊CMOS Image Sensor、Flash、DRAM |

| 夏普 |

CMOS Image Sensor、邏輯IC |

| 意法半導體 |

射頻、CMOS Image Sensor、MEMS |

| 晶圓廠 |

特許半導體 |

DRAM、邏輯IC |

| 台積電 |

CMOS Image Sensor、MEMS |

| 封裝 |

Amkor |

Flash、DRAM |

| 日月光 |

射頻、Flash、DRAM |

| Xintec |

CMOS Image Sensor |

資料來源:各單位,工研院整理

而國內驗證業者宜特科技也在2010年2月宣布通過經濟部業界科專計畫申請,將斥資逾新台幣億元打造驗證與分析技術研發中心,專為高科技產業提供在設計開發新產品過程中所需的分析驗證技術,其中亦包括微機電系統(MEMS)及先進封裝如3D IC、晶圓級晶片尺寸封裝(WLCSP)與SiP等。該研發中心預計將在3月1日正式營運。

而由工研院主導之全球首座3D IC實驗室,也預計將在2010年中登場,主要將以整合3D IC的主流技術矽穿孔(TSV)製程流程、縮短積體電路及晶片開發時間為主要任務,協助半導體廠商迅速將先進晶片設計導入市場,進而大幅降低初期投資。

簡單來說,TSV是3D IC的未來重點技術,其乃透過垂直導通方式來整合晶圓堆疊,並達到晶片間的電氣互連,讓未來晶片如高樓般堆疊,進而節省空間。TSV技術主要是用來製造更小巧、節能、效能更高的晶片。

工研院院長李鍾熙(圖3右二)表示,國內一向是半導體產業的大本營,而此次隨著3D IC之演進,國內業者若能快速掌握最新與關鍵技術,勢必有助在此領域站穩腳步、搶得先機。

|

| 圖3 工研院院長李鍾熙(右二)認為,由於3DIC是半導體產業未來10年之重要發展動力,因此該院將與美商應用材料公司攜手合作,共同開發3D IC核心製程。 |

工研院電光所副所長洪勝富透露,工研院早在6年前便率先投入3D IC研發,取得發展優勢,而稍早成立的先進堆疊系統與應用研發聯盟(Ad-STAC),更是跨產業整合的立體堆疊晶片研發平台。因此,他認為,隨著陸續吸引國際設備大廠如美商應用材料、SUSS MicroTec及Semitool等的加入,將有助共同發展3D整合技術,提供國際化的開放合作平台。洪勝富強調,與美商應用材料之合作,將有助TSV技術之精進,並可望降低成本,帶動國內外3D IC相關產業加入,加速國內業者自主製程技術開發,進而提升國內半導體產業競爭優勢。

據悉,該實驗室將建構包括蝕刻、物理氣相沉積、化學機械研磨及電漿強化化學氣相沉積等四大設備,以協助製造與TSV技術相關的晶片。同時工研院也將與美商應用材料針對先鑽孔(Via First)、後鑽孔(Via Last)及其他製程流程進行技術整合。

應用範圍無遠弗屆

而隨著3D IC的市場發展,其相關應用之潛力也更加具有吸引力。目前3D IC的應用領域,包括影像感測器(CMOS Image Sensor)、記憶體如SRAM、DRAM或NAND Flash、處理器、感測器與數位訊號處理器(DSP)、現場可編程邏輯陣列(FPGA)與微機電系統(MEMS)等,其應用市場成長預測概況如圖4。

|

資料來源:工研院晶片中心

圖4 2006~2014年3D IC應用預測 |

事實上,隨著TSV技術不斷演進,不少廠商已經瞄準記憶體為主要應用,包括爾必達(Elipda)與三星電子(Samsung Electronics)均已陸續推出TSV 3D IC之動態隨機存取記憶體(DRAM),另外如東芝(Toshiba)也針對此技術之發展進行討論。

不少業者認為,隨著3D IC之相關技術進一步突破,不但記憶體將是首要市場,其他包括射頻、電源甚至顯示技術都有發揮空間。

3D IC非萬能 諸多瓶頸待突破

儘管3D IC被視為未來極具發展潛力之關鍵技術,仍有不少業界人士認為,以現行步伐來看,3D IC距離真正實現與大規模應用仍頗遙遠。

掌握核心技術才是王道

|

| 圖5 瓷微科技無線模組事業部總經理特助兼資深專案經理楊照盛表示,晶片設計廠商與競爭對手的差異應該在設計本身,而非封裝技術。 |

隨著各式封裝技術的演進,近期不少半導體業者均將3D IC視為未來必經之路,甚至將其視為扭轉乾坤、轉虧為盈之法寶。但瓷微科技無線模組事業部總經理特助兼資深專案經理楊照盛(圖5)指出,封裝技術向來只是工具,晶片設計廠商如何從核心技術上提供更多加值空間,才是真正企業得以存活的關鍵。他強調,儘管透過TSV等其他先進技術,可協助晶圓或晶片進行堆疊,進而達到縮減晶片空間、節省打線長度及其他優勢。但晶片設計業者不該迷失了方向,甚至隨著封裝技術起舞。

瓷微科技乃針對無線感測網路(WSN)如ZigBee等技術進行開發之廠商,目前則以SiP為主要封裝方式。楊照盛指出,該公司能與其他競爭對手造成區隔之主要關鍵,仍在於如何開發出更具競爭力的產品,例如針對不同應用而提供彈性設計。但最後究竟採用SiP、SoC或是更進階的3D IC技術來打造晶片,其實純屬枝微末節。

楊照盛強調,隨著封裝技術逐日演進,晶片原本就會朝向更小、更具效能與更具競爭力的方向邁進。但若相關廠商被封裝技術迷失了方向,一味強求立體封裝而忽略自有核心技術與區隔性,無異捨本逐末。

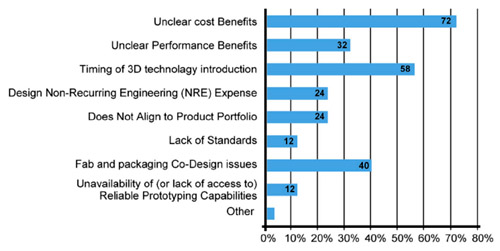

事實上,稍早在一份針對3D IC所進行的調查(圖6)中指出,有高達七成以上的受訪者不確定3D IC能帶來的真正好處為何,而近六成的業者則認為3D IC的問世時程將是一大問號,顯見3D IC在談蘊含的商機前,仍須要從更實際的面向開始談起。

|

資料來源:工研院晶片中心

圖6 3D IC商業化挑戰 |

|

| 圖7 科統科技行銷業務部行銷業務處資深處長黃建義認為,若無法找到微縮化、立體化現有產品能為客戶帶來的核心價值,一頭栽進3D IC恐非益事。 |

科統科技行銷業務部行銷業務處資深處長黃建義(圖7)也抱持類似看法。他說,今日的消費性電子生命週期短、汰換速度快,若供應商並未找到產品本身之核心價值,而是一味的追求先進技術,恐遭邯鄲學步之譏。

黃建義表示,真正具有專業知識之供應商仍應視市場與客戶需求提供標準化或是客製化之解決方案。先進技術雖具一定優勢與特性,但要將之落實仍需諸多條件配合。在此之前,發揮自身核心優勢並提升盈餘與市占,將更為關鍵。

如科統科技乃以應用於手機之多晶片封裝(MCP)記憶體為產品主力,透過整合NOR、PSRAM與NAND、Mobile DRAM等各式記憶體,提供最佳解決方案。

黃建義認為,相較於無止盡地微縮化、立體化,不如認真思考自身產品能為客戶帶來多少加值,將更具意義。

技術挑戰接踵而至

|

| 圖8 Tessera台灣區總經理暨東亞區總監魏煒圻分析,3D IC技術尚未成熟,包括設計、散熱管理、組裝、效能與可靠度等都是挑戰。 |

要落實3D IC技術,尚有諸多挑戰須要優先解決。封裝解決方案供應商Tessera台灣區總經理暨東亞區總監魏煒圻(圖8)即透露,3D IC設計人員所面臨的挑戰包括設計、散熱管理、組裝、效能與可靠度等。他進一步解釋,在設計端,目前的電路設計工具支援堆疊了一個、或是更多晶片的單一基板。但由於3D封裝必須在多個基板與多種互連環境中進行整合設計,在現行缺乏3D架構的模擬功能下,將是一大挑戰。

在散熱管理部分,由於立體封裝技術將多個高耗電晶片高度靠近,再加上使用高熱阻材料之基板、外殼及晶粒連結元件,因此封裝表面外層的傳導效率不甚理想。據悉,目前的技術乃利用大量的內連線(Interconnect)、含銅量較高的印刷電路板或系統外殼來作為散熱管道。

目前在處理3D IC的組裝過程中,維持低翹曲的基板、封裝等結構、確保3D結構內各種材料的相容性,並開發相關設備功能來支援各種非標準零件的困難度極高。且由於損失多晶片系統的代價很大,因此可靠度與良率更加重要。

魏煒圻分析,因採用較短的電路,3D IC通常擁有許多電氣效能優勢,但也因此而面臨低雜訊電源供應與配線壅塞等問題。對於採用多種包括射頻、高速數位、類比等技術的系統而言,效能模擬的作業尤其重要。

另一項至為關鍵的議題則是可靠度。與單晶片封裝相較,3D IC由於使用薄型晶片、較小的內連線,與較多的材料與處理流程,所以可靠度通常較低。尤對各種行動系統而言,勢必須要加以重視。

目前已知可透過機械與結構模擬及材料測試等方式來克服可靠度問題。但現今的模擬軟體為針對量產材料所設計,並不適用於具備精細結構的多層超薄材料。軟體工具仍須能支援薄型材料、進行黏性分析與失效分析,以及預測生命週期,才能改善設計並最佳化組裝結果,進而加快產品上市時程。

半導體測試廠商態度保守

|

| 圖9 惠瑞捷台灣分公司總經理陳瑞銘透露,3D IC發展須循序漸進,且離真正實現仍有一段距離,因此該公司暫時不會對此領域大舉投資。 |

此外,若從半導體測試的角度來看,也對3D IC頗為保守。半導體測試設備業者惠瑞捷(Verigy)台灣分公司總經理陳瑞銘(圖9)便明白指出,該公司至今並未針對3D IC進行大規模研究,短期內也難以見到相關測試設備問世。

一般認為,3D IC對測試設備之挑戰多半來自晶圓層級更多、厚度更薄、異構核心(Heterogenous Cores)與更多打線等。其他再加上不同晶片間的整合、靜電放電(ESD)、非接觸性測試或晶片雙面探測等,也都是潛在難題。

陳瑞銘不諱言,相較於3D IC及其測試需求,該公司現階段更重視的是今日之半導體測試應用。而更進階的技術發展,就留待時機成熟再加以著墨。

3D IC終有成 追尋核心競爭力才是真諦

雖然各界認為3D IC的實現並非一蹴可幾,但由於過去50年來,半導體產業一直是技術演進的先鋒,因此業者們也均認為3D IC的普及仍指日可待。不過正如楊照盛與黃建義等人所述,立體堆疊技術僅是協助晶片成形的工具,晶片真正的核心競爭力為何,仍需業者戮力打造,才能帶來差異化,同時拉大與競爭者的差距。但無論如何,3D IC的發展,同樣引人期待。