為了滿足資料中心光網路和光纖網路對頻寬的巨大需求,利用先進多工技術與機器學習提升矽光子晶片的傳輸速率與效能將會是大趨勢。

本文簡要說明這些技術的發展狀況,以及如何利用先進的分模態多工技術和機器學習演算法,提升矽光子晶片的傳輸速率超越Tbit/s。

矽光子概念介紹

通訊技術的發展帶動著影視電玩與雲端串流服務等迅速崛起,頻寬的需求亦是日益劇增,第五代行動通訊技術(5G)與人工智慧(AI)的普及更是將網路需求推向高點,種種進展使得無線通訊系統、光纖接取網路以及資料中心網路的傳輸速度成為近年來研究的重要議題之一,其中矽光子(Silicon Photonic)被視為一種具有突破潛能的新穎技術,日漸廣泛研究及應用於學界和業界。

矽(Silicon, Si)作為矽光子技術的基礎材料具有不少的優勢,首先矽是全球地殼含量最多的元素之一,對於原料的取得成本較小,此外憑藉其半導體材料的特性,能夠與現今積體電路採用的互補式金屬氧化物半導體(Complementary-metal-oxide-semiconductor, CMOS)製程技術具有極好的相容性,對於技術的製程成本較低。

而在光通訊常用之紅外波段,即C波段(波長範圍約為1,530~1,565nm),對於矽元素為穿透波段得以傳遞光訊號,若是與特定材料進行摻雜,例如鍺(Germanium, Ge),進而由穿透轉為吸收作為接收器使用,拓展其材料特性的使用靈活度。再者,由矽與二氧化矽(Silicon Dioxide, SiO2)組成的矽晶體在絕緣體之上(Silicon-on-insulator, SOI)結構設計,由於高折射率差異的關係,增強了光場傳播的局限性進而降低傳播損耗並有效提升整體的傳播效率,有助發展微小尺寸而又結構複雜的光路系統。

綜合以上特性,讓矽光子技術在光積體電路(Photonic Integrated Circuit, PIC)的研發具有低成本、低能耗與高密度積體化的優點,且透過光路而非電路傳輸,更能有效避免傳統積體電路傳輸速度受限電磁波以及熱能效應之影響,大幅提升資料傳輸數據量而被廣泛應用於資料中心網路。

資料傳輸量的提升,除了仰賴矽光子技術將硬體設備以高密度積體化建構通訊系統架構之外,更有賴於如何更有效率地善用有限的頻寬,因而尚需導入多工技術(Multiplexing)、高階傳輸格式如四階脈衝振幅調變(4-level Pulse Amplitude Modulation, PAM4)以及正交分頻多工(Orthogonal Frequency Division Multiplexing, OFDM)訊號等,並結合現今蓬勃發展的機器學習(Machine Learning, ML)技術,修補訊號因傳輸過程導致的失真或損耗,彌補硬體設備和系統架構上的不足,由軟體層面提升整體數據傳輸容量。

分模態多工之寬頻高速傳輸系統

多工技術的問世對於飛快成長的數據傳輸量有著不小的貢獻,多工技術即是透過不同的物理維度或傳輸路徑,來達到整體高速傳輸的效果,常見的多工技術包含分時多工(Time Division Multiplexing, TDM)、分波多工(Wavelength Division Multiplexing, WDM)、分極化多工(Polarization Division Multiplexing, PolM)以及分空多工(Spatial Division Multiplexing, SDM)等。

其中,SDM能將不同的訊號傳輸於分立的光纖或波導路徑之中,例如多核光纖(Multi-core Fiber, MCF)的使用,而筆者團隊近年則致力於使用彼此正交的固有模態(Eigen-mode)傳輸訊號的分模態多工(Mode Division Multiplexing, MDM)技術之研究,將分模態多工器(Multiplexer, MUX)以及解多工器(De-multiplexer, DEMUX)應用於矽光子晶片進行高速訊號傳輸,其相關研究成果也刊登於國際學術期刊以及國際研討會。

團隊對於矽光子晶片之研究,包含使用Lumerical模擬軟體進行矽晶元件之研發設計與優化,以及使用PhoeniX,OptoDesigner和KLayout等軟體進行積體光路之布局整合,並下線進行矽晶片製程,最後進行元件之分析量測,根據實驗數據進行下一階段的優化設計。

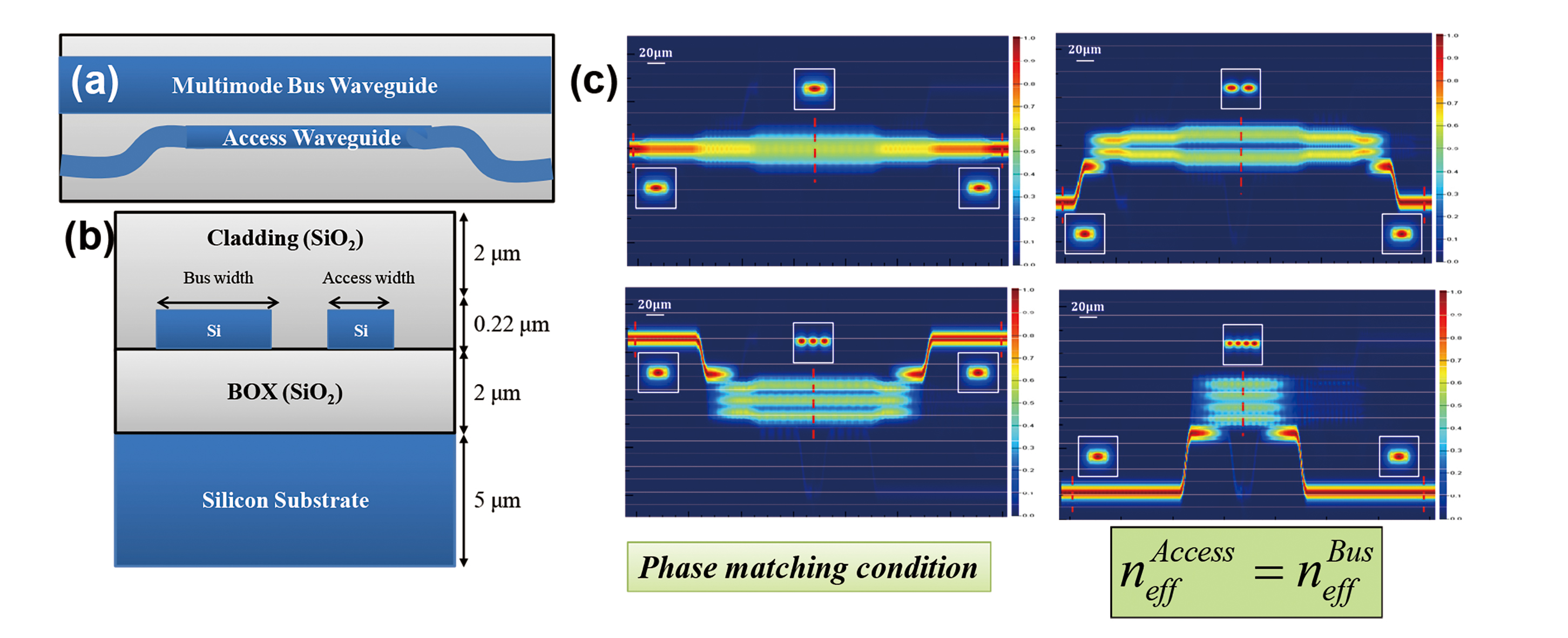

分模態(解)多工器之研究便是在此完整的設計研發流程逐步完善的矽晶元件,其原理乃是依據相位匹配條件(Phase Matching Condition)來實現,在符合下線製程之固定波導高度的條件之下,不同模態之有效折射率(Effective Index)會隨著所處波導寬度的不同而有所改變,如圖1所示,因此藉由適當的波導寬度與間隙寬度設計使得有效折射率相同達到相位匹配條件時,模態便能透過增強消散波耦合(Enhanced Evanescent-wave Coupling, EEC)於波導之間進行轉換,分立或增加所需的模態實現分模態多工以及解多工器的效果,此模態轉換區間稱為非對稱式定向耦合器(Asymmetric Directional Coupler, ADC),是由負責傳輸基礎模態(Fundamental Mode)的接取波導(Access Waveguide)以及負責傳輸高階模態的共用波導(Bus Waveguide)構成。

圖1 (a)、(b)分模態(解)多工器之示意圖。(c)藉由適當的波導寬度設計使得有效折射率相同達到相位匹配條件時,實現分模態多工以及解多工轉換。

圖1 (a)、(b)分模態(解)多工器之示意圖。(c)藉由適當的波導寬度設計使得有效折射率相同達到相位匹配條件時,實現分模態多工以及解多工轉換。

考量實際元件面積占比以及模態間串擾的優化,實驗室主要以四通道分模態多工器之結構進行設計分析,並適用橫向電場(Transverse-electric, TE)模態,由模擬分析可知四通道分模態多工器在波長範圍為1,530~1,555nm的各通道模態轉換效率皆大於90%,此外團隊亦針對波導寬度的偏差容忍度進行探討,模擬顯示一般製程誤差並不會對耦合效率有顯著之影響,說明此設計元件具有涵蓋常用通訊波段的良好寬頻表現。

基於以上分析結果,團隊以四通道分模態多工器結合分波多工技術,搭載48個波長通道,以此傳輸平均數據傳輸量約為50Gbit/s的OFDM訊號,最終在符合前向錯誤校正(Forward Error Correction, FEC)所制定的條件之下,達到9.4Tbit/s的數據總傳輸量[IEEE Access, vol. 7, pp. 129104 (2019)]。

除此之外,團隊更進一步將接取波導的寬度由450nm縮窄為350nm,這使得模態轉換之間的耦合長度(Coupling Length)相較前項設計能夠巨幅縮短80%,大幅降低整體元件所占之長度而無顯著效能降低的現象,以此在相同的波長通道數以及訊號調變格式之下,最終平均數據傳輸量達到約60Gbit/s,總數據傳輸量也突破至11.7Tbit/s[IEEE Access, vol. 8, pp. 219881(2020)]。

少模光纖實現矽晶片間之訊號傳輸

矽光子技術的實現讓數公分的市售光電元件,得以在數毫米的矽光子晶片上以微米等級的姿態登場,隨著製程技術之進展以及結構設計之改良,其效能相較研發初期已然有顯著的提升,不但單一光電元件能有優秀的表現,數個光電元件組成的光路系統亦能有所發揮。然而,資料中心的傳輸速度不光只是追求單一矽晶片的內部運算速度,更有賴整體架構之間的高效率資訊傳遞,以此為發想團隊嘗試使用少模光纖(Few Mode Fiber, FMF)實現矽光子晶片之間的訊號傳輸,並搭配多模分工器提升資料傳輸量。

晶片間之數據傳輸困難在高階模態於波導與光纖之中是以不同的震盪形式在傳播,直接以現有的一維或二維光纖光柵耦合器(Two-dimension Fiber Grating Coupler, 2D-FGC),對於高階模態勢必會減低模態轉換之間的效率,而需要提升功率造成耗能增加,為此必須特別設計適用於高階模態的二維光纖光柵耦合器,再者,由於高階模態在傳遞時容易產生模態串擾或轉換成其他階數的模態,使得轉換效率以及傳輸量降低,因此團隊採用FMF作為晶片間傳遞的光纖,以此來減少高階模態產生的可能性。

實驗成果的部分,團隊以兩個向量之分模態多工器傳遞兩組模態,經由2D-FGC將波導模態轉換至光纖模態後由FMF傳遞另一組相同設計之晶片元件進行對稱式解調,如圖2所示,搭配分波多工最多單一模態通道可傳輸34個波長通道,最終總數據傳輸量達到4.36Tbit/s[OFC 2021, paper M3D.6]。

圖2 經由2D-FGC將波導模態轉換至光纖模態後由少模光纖(FMF)傳遞另一組相同設計之晶片元件進行測量示意圖和實驗照片[OFC 2021, paper M3D.6]。

圖2 經由2D-FGC將波導模態轉換至光纖模態後由少模光纖(FMF)傳遞另一組相同設計之晶片元件進行測量示意圖和實驗照片[OFC 2021, paper M3D.6]。

神經網路修正訊號品質並提高傳輸量

縱使矽光子元件在效能上相較過往已有明顯提升,仍然難以追上頻寬和傳輸速率龐大的需求市場,無論是對於材料的選擇、製程極限的突破、元件結構的改良等,都須仰賴大量的時間以及精力成本,為此團隊提出以遞迴神經網路(Recurrent Neural Network, RNN)系統中的長短期記憶神經網路(Long Short Term Memory Neural Network, LSTMNN)去修復失真訊號以降低訊號錯誤率。

實驗中使用面積占比極小的矽微環調變器(Silicon Micro-ring Modulator, Si-MRM),用以調變PAM-4訊號實現強度調變直接偵測(Intensity-modulation Direct-detection, IM/DD)的系統架構,此架構的優點在於訊號在調變以及解調變都較為簡單,毋須過於複雜的架構設計即可完成。然而,以向量網路分析儀(Vector Network Analyzer, VNA) 對於Si-MRM進行量測,結果顯示在為施加外部偏壓時其3dB頻寬僅有47GHz,但仍無法滿足傳輸速度的需求。

因此團隊提出以LSTMNN長短期記憶神經網路的方法對於訊號進行補償,其原理為透過神經網路的方式對於偵測到的訊號進行預測與判讀,讓訊號在系統中能夠自行匹配出較低誤碼率(Bit Error Rate, BER)的結果,此方法的優勢在於相較過往使用的數位訊號處理(Digital Signal Processing, DSP)而言,神經網路毋須預先知曉一定程度的原始訊號資訊,即可針對接收訊號進行優化,實驗結果顯示在通過FEC標準之下,BER能夠有效降低且傳輸速度達到每個波長通道160Gbit/s,彌補硬體在物理方面的傳輸極限[OFC 2021, paper Tu5D.3]。圖3展示以長短期記憶神經網路去修復矽微環調變器訊號,及編碼解碼訊號處理流程圖。

圖3 (a)以長短期記憶神經網路(LSTMNN)去修復矽微環調變器訊號,達到每個波長通道160Gbit/s,彌補硬體在物理方面的傳輸極限的示意圖、及(b)編碼(c)解碼訊號處理流程圖[OFC 2021, paper Tu5D.3]。

圖3 (a)以長短期記憶神經網路(LSTMNN)去修復矽微環調變器訊號,達到每個波長通道160Gbit/s,彌補硬體在物理方面的傳輸極限的示意圖、及(b)編碼(c)解碼訊號處理流程圖[OFC 2021, paper Tu5D.3]。

矽光子在台灣展望

近年來,不論從上游的研發設計到矽光子晶片的製程,而至應用矽光子技術實現的收發器(Transceiver)商品,以及各種與矽光子整合技術相關的模擬軟體,皆可以看到許多國際知名企業與學校投入其中,而台積電以及鴻海等企業,更是不落人後於矽光子的技術發展。基於通訊需求的持續擴展,科技部亦針對矽光子科技開展了一項為期四年的旗艦計畫,其中本團隊便參與了「通訊應用矽晶光電同調收發模組之研究」,並共同主持此研究計畫,期盼共同開發出高速的矽晶光電同調收發模組。

分模態多工器與解多工器的研發,良好地體現了被動元件無須額外電壓施加的優勢,透過結合分波多工的技術以及高階調變訊號格式的應用,便能達到高速訊號傳輸的系統架構。少模光纖的應用更讓傳輸維度跳脫單一矽晶片內部的光路架構,而能實現矽光子晶片與矽光子晶片之間的訊號傳遞,完善資料中心的系統。神經網路的使用更是從另一個層面彌補硬體設備的限制,使得矽光子晶片的訊號傳輸品質得以大幅提升。

(本文作者為國立陽明交通大學光電系教授,文字由陳冠宏整理)