拜更強大的基頻(Baseband)與應用處理器所賜,手機的功能不斷進步,運作頻率也持續提升,業界也朝向採用層疊封裝(PoP)堆疊技術。這些手機功能與處理器容量的提升,要歸功於半導體製程技術的進步。舉例來說,基頻與應用處理器需要越來越多的內連線,迫使業界轉而採用面陣列式覆晶封裝。此外,從引線搭接轉向覆晶技術,對於PoP的設計與組裝而言,也衍生出許多挑戰與機會。

帶動PoP堆疊的力量,主要是手機與其他掌上型電子裝置須要縮小封裝的底面積。除了得減少在主機板上占用的空間,其面積不得超過記憶體,且須將邏輯元件封裝並排外,PoP堆疊因為可減少零件之間的連線長度,故帶來更好的電氣效能。PoP封裝符合固態技術協會(JEDEC)的相關標準,讓製造商能向不同供應商購買邏輯與記憶體元件。邏輯堆疊上典型的PoP記憶體頂部與底部之間的球柵陣列封裝(BGA)內連線間距僅有0.65毫米(mm),底部封裝與主機板的BGA間距則為0.55毫米。現今採用PoP製程的雙記憶體晶粒,頂部封裝的最大高度為1.3~1.4毫米。但這種元件的高度,通常超過許多上層封裝內有超過兩個記憶體晶粒堆疊的PoP封裝(表1)。

智慧型手機的市場持續成長,預計在2013年出貨量將超過五億支。消費者期盼多合一的功能,包括行動上網、影音、衛星定位、相機及遊戲等功能。對於更高效能的需求,帶動了處理器晶片尺寸的成長,以及需要更多的內連線。此外,各種封裝規格將維持不變甚至縮小,以便能夠裝入越做越小與越薄的裝置內。

覆晶底部封裝帶來充裕彈性

在底部封裝運用覆晶內連線技術,為PoP堆疊提供更多彈性。以覆晶來取代晶粒層級的內連線,會增加X/Y軸向的可用空間,如此會增加頂部與底部連結點的數量,或是做出更大的處理器晶片。

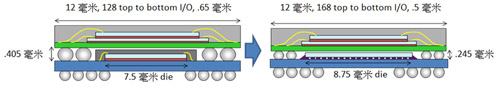

由於覆晶晶粒採用充填底膠,因此毋須從頂部向下澆灌封膠,也不須要引線搭接,從而減少所需的X/Y軸向空間。而省去向下澆灌封膠,亦可縮減頂部與底部封裝之間的間距高度,故允許在更細的內連線間距中採用較小的錫球(圖1)。

|

| 圖1 左為晶粒層級的內連線,右為覆晶底部封裝。 |

另一種增加功能的途徑,是採用封裝高度較低的覆晶晶粒,並把第二個晶粒疊到覆晶的頂部。第二個晶粒需要引線搭接的內連線,以及進行頂部向下澆灌封膠,以此法製作出的PoP內連線會增加高度,因此需要較大的錫球與較大的間距。疊在底部的第二個晶片,與頂部封裝之間也可能需要更多連接點。整個封裝必須加高與加寬來容納這些元素,或採用高長寬比的細間距解決方案,作為頂部與底部封裝的內連線(圖2)。

|

| 圖2 採用封裝高度較低覆晶圖示 |

堆疊晶粒需創新的PoP內連線

隨著處理器的功能日趨強悍與多元化,即使置於底側封裝的單晶粒仍需要更多內連線來連結頂側封裝,需要的數量超過最低標準間距0.5毫米,例如12毫米封裝的一百六十八個輸入/輸出(I/O)端子。增加封裝的底面積來容納更多頂側封裝與底側封裝的內連線,或是在現有規格中加入更多列的端子並縮減晶粒的尺寸的作法,在大多數情況下都不可行,因此須要採用細間距的解決方案。

|

| 圖3 μPILR PoP封裝圖示 |

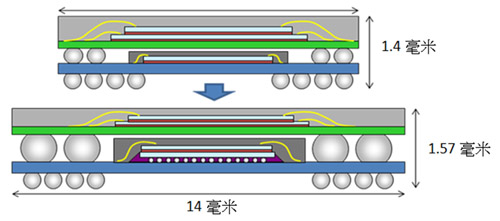

其中一種解決方案是提高封裝密度,並維持或縮減封裝的底面積,也就是Tessera的μPILR PoP封裝(圖3)。

較小長寬比的銅柱,抬高溼式處理的表面,讓焊料的內連線高於基板的表面,讓元件可採用越來越小的錫球,進而置於更細的間距。經過溼式處理準備進行μPILR製程時,焊料就會吸附到錫柱上,並維持足夠的間距,避免垂直內連線間出現焊料的搭橋短路現象。這使得PoP能在更細的間距上進行堆疊,直立高度提高的幅度,就是μPILR的高度。額外多出的高度餘裕度,能為底部封裝堆疊晶粒帶來緩衝彈性,毋須增加元件的整體底面積,進而節省封裝成本和主機板空間。

此外,高度平面化銅柱所抬高的溼式處理表面,會產生更高的堆疊良率,提供更多緩衝空間,消除因基板的板彎造成接點開路與短路的缺陷。針對一般板彎變形的基板進行並置堆疊測試時,利用μPILR技術所做出的內連線,不僅沒有開路或短路的現象,錫鉛凸塊很牢固地接合各個零件。

μPILR PoP解決方案克服了傳統BGA技術的種種限制,讓製造商能推出低高型、微間距、且效能更高的元件。μPILR能達到0.3毫米的間距,並讓直立高度維持在0.2毫米,讓封裝的整體高度不到1.0毫米。這項技術還帶來高可靠性優點,因為μPILR內連線在靜態與動態負載下,都維持相當高的耐撓曲性。最後,由於μPILR PoP採用標準材料與組裝製程,因此毋須再投資增加基礎設備。

新覆晶組裝方式挑戰不小

|

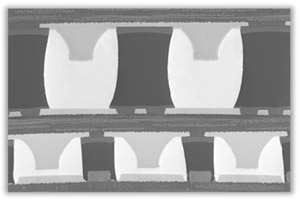

| 圖4 μPILR覆晶貼合為細間距的凸塊溼潤及底部填膠的實際直立空隙提供較多容許幅度。 |

除了PoP外,μPILR還可用在底部覆晶封裝,透過基板上的銅柱將覆晶晶粒接合在封裝上,而不是透過晶粒上的銅柱(圖4)。

μPILR提供一種高共面性的凸塊互連層,為凸塊接合提供更高的溼製程容許幅度(Wetting Margin)。在組裝大體積薄型元件時,這種特性非常重要,尤其是內含大量凸塊且容易繞曲的超薄封裝基板。支援覆晶的μPILR內連線,亦能建構出更高的I/O元件,能夠把間距縮小至100微米(μm)以下。這讓業者可預估直立高度,即使採用可塌扁的無鉛焊錫凸塊,底膠仍能維持高良率,並降低電遷移造成損毀的風險,因為縮減間距,不一定要縮減晶粒銲墊尺寸,也不一定會產生電流聚集效應(表2)。

消費者不斷要求更薄且更強大、多功能、多合一的掌上型電子產品。為滿足這些需求,PoP元件必須持續微型化,並提高內連線密度來達到更高處理效能。在底部封裝晶粒運用覆晶技術,雖然有助縮小封裝尺寸,但由於用到傳統焊球,因此發展受到限制。μPILR內連線解決方案,支援PoP與覆晶內連線,能進一步整合各項功能,並讓電子元件持續微型化。

(本文作者為Tessera台灣區總經理暨東亞區總監)