目前全球石英(Quartz)元件每年總產值超過45億美元,而伴隨著終端市場不斷推陳出新,整體產業也將在穩定中持續成長。由於石英晶體、濾波器、振盪器等石英元件關係到系統運作的穩定性,其提供準確時脈訊號(參考頻率)供系統運作於控制電波頻率及穩定訊號,並具有控制時脈、產生頻率和過濾雜訊功能,應用範圍包括通訊、工業、軍事、醫療等領域。

根據NDK估算,全球石英元件約有35%應用在通訊產品,30%在個人電腦(PC)及消費性電子中使用,基地台及衛星等相關產品應用比重約占10%,而由於汽車電子興起,目前比重已達18%,故不論高、中、低階電子產品,石英元件皆不可或缺。

壓境石英市場 MEMS振盪器崛起

目前時序元件市場中的主流技術為石英振盪技術,在全球石英晶體產業中,以日本為主要生產地,產值占全球60%以上,包括愛普生東洋(Epson Toyocom)、NDK、京瓷(Kyocera)、KDS和住友(Sumitomo)等。然而,面對市場對元件性能與成本的持續要求,石英元件已面臨極大的挑戰,例如陶瓷封裝材料來源受限。多層夾合的陶瓷基材為目前全球石英振盪器元件業界之封裝基材採用主流。由於該石英振盪器元件之陶瓷封裝基材在製程與材料方面,有其技術困難點與專利障礙,相關陶瓷材料業者在切入該製程開發後,面臨技術成熟度與規格無法與目前全球主要供應商京瓷相抗衡,再加上該公司壓低陶瓷基材的價格,使得其他業者無法在此材料元件上與其相抗衡。

另外,隨著消費性可攜式裝置與行動網路的蓬勃發展,這些隨身電子裝置也被要求必須兼具更輕薄、更長使用時間與更高效能的性能特點,而其內部所使用的石英振盪元件,在此趨勢要求下,同樣也必須朝小型化、低耗電、高精確度、高可靠性的方向不斷進步,其中最無可避免的挑戰是滿足對體積要求的持續小型化。

|

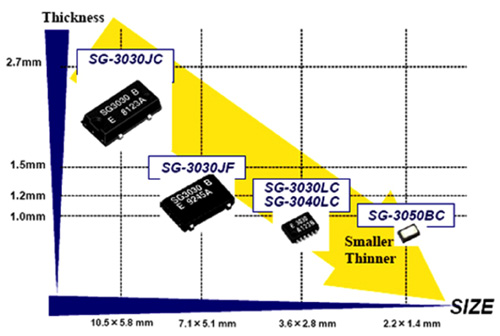

| 圖1 石英振盪元件的尺寸演化趨勢圖 |

以音叉型(Tuning Fork)石英晶體單元為例,在過去10年中,其體積從約150立方毫米(mm3)縮小到只有1.5立方毫米,縮小幅度高達一百倍以上。目前此小型化的趨勢仍不斷演進(圖1),因此在電子產品輕薄化的同時,也為石英振盪元件的開發帶來新的挑戰與衝擊。

當石英晶體要具備愈來愈小的體積時,機械式的傳統研磨切割製程已然面臨技術瓶頸,在可見的未來,石英振盪元件的小型化技術勢必將面臨越來越難以突破的挑戰,而極有機會取而代之的將是新一代微機電系統振盪器(MEMS Oscillator)技術。

目前MEMS振盪器的市場應用已經開始起飛,並已逐漸滲透與侵蝕傳統石英振盪器市場。在國際上,在此領域的領先廠商包括美商SiTime、Discera等,其策略上均以鎖定特定應用來開始取代傳統石英晶體振盪器。

與傳統石英振盪元件相較,MEMS振盪器具有以下幾項優勢:超微型化的振盪結構,可滿足振盪器元件體積越來越小的市場趨勢要求;可數位補償的全溫頻率穩定性,可使MEMS振盪器具有極低的全溫頻率漂移(<±5ppm);可程式校正架構為系統設計和縮短多樣性新產品開發週期,提供必要的靈活性與競爭力;完善的半導體生產鏈可讓MEMS振盪器供貨期全面縮短,並提升需求應急的能力;全自動生產的加工製作方式,使微機電振盪器在品質和可靠性方面具有極高的一致性和重現性。

以上這些特點也使得MEMS振盪器比傳統石英晶體振盪器更能符合電子產品對未來市場的需求,也因此微機電振盪器在未來,可望隨著半導體製程技術的提升,而逐漸加速替代既有的石英晶體振盪器解決方案。

MEMS振盪子特性各異

|

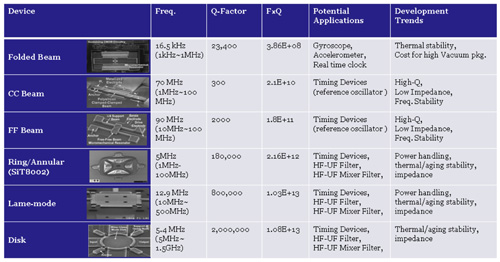

| 表1 不同形式震盪子之特性與應用 |

MEMS振盪子(Resonator)根據其機械特性、結構形狀,以及其使用的材料與振動模態,一般可以分為自由樑(Free Beam)振盪器、固定樑(Clamp Beam)振盪器、拉梅模態(Lame Mode)振盪器、環形(Annular)振盪器以及碟狀(Disk)振盪器等。不同設計形式的振盪子具有不同的振盪特性(表1)。一般而言,振盪子的振盪形式主要受到頻率及品質因子(Quality Factor)影響,因此振盪器產品的應用範圍不同,振盪子振盪形式與主頻率亦不同。

剖析MEMS振盪子關鍵性能

對MEMS振盪子而言,衡量其性能的重要特性指標,除了有振盪頻率(Resonant Frequency)與品質因子外,其他如動態阻抗(Motional Resistance)、溫度穩定性(Temperature Stability)以及功率消耗等將決定振盪器的輸出性能。而在這些性能指標上,將會受到結構設計、製程、電路以及封裝等因素的影響。

對振盪子而言,其品質因子越高越好,因為品質因子代表著振盪子的能量損耗的程度,一般而言品質因子可表示如公式1:

...公式1

|

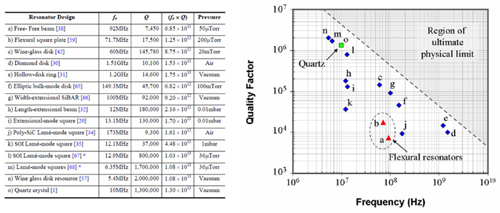

| 圖2 振盪子品質因子與頻率乘積特性 |

其中Qair為空氣阻尼的影響,Qanchor為振盪子與基材(Substrate)連接之固定島塊(Anchor)影響,Qsurface為振盪子表面晶格缺陷造成之影響,QTED則為熱彈性(Thermal Elastic)阻尼的影響。因此對振盪子而言一般會採用真空封裝使其空氣阻尼效應降低,或者在設計上會將振盪子的固定島塊設計在振盪波的節點(Node)上以降低振盪波傳遞的能量損失。所以,無論透過製程或是設計的手段,都是希望能夠提升振盪子的品質因子,但品質因子的提升有一定的極限,所以無法無限量地提高。由文獻上可知,振盪子品質因子與操作頻率乘積(f-Q)具有物理極限如圖2所示。

|

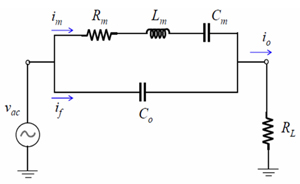

| 圖3 振盪子等校RLC電路 |

而MEMS振盪子另一個關鍵性能就是其動態阻抗Rm。振盪子的機械結構特性可以用等效RLC電路表示(圖3)。圖中Vac為驅動訊號,i0為輸出電流,C0為穿隧電容(Feedthrough Capaciatnce)。

而振盪子的動態阻抗可表示如公式2~3:

................................公式2

....................................公式3

其中η為機電耦合係數(Electromechanical Coupling Factor),與驅動/感測電極的面積(Ae)、介電常數(ε)及振盪子的體電壓(Vp)成正比,而與電極和振盪子的間隙(g)成平方反比。因此,為了降低振盪子的動態阻抗,一般除了將品質因子提高外(Qtotal),亦可將機電耦合係數(η)提高。

但圖2所示,一般而言,當振盪子頻率中心與振盪子形式確定後,其品質因子的極限值即可確定。因此一般為降低動態阻抗可由提高機電耦合係數(η)達成,常見的方法有提高體電壓,增加電極面積以及縮小間隙等,可是電極面積往往會決定振盪子的尺寸,因此在尺寸的考量下,電極面積增加的幅度也有限。

另一方面,提高體電壓往往也必須犧牲電路的複雜度,且有可能會導致振盪子產生不穩定現象。而縮小電極間隙是最有效率的方法(因Rm與振盪子的間隙(g)成四次方反比),但縮小間隙往往受限於黃光製程的能力。

為了有效縮小間隙,無論國外大廠或是研究機構等提出了許多不同的次微米間隙(Submicron Gap)的製作方式,以提高機電耦合係數。以下將針對目前不同的振盪子與次微米間隙的製作方法做一說明。

|

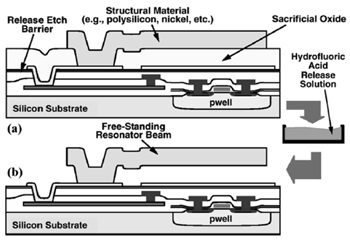

| 圖4 多晶矽面型微加工製程之基本流程圖。(a)去除犧牲氧化層前的結構示意圖;(b)去除犧牲氧化層後的結構示意圖。 |

MEMS振盪子製程說明

除了MEMS振盪器的結構設計有所區別外,在微機電振盪器的製作加工上,目前國外研究機構的發展重點在於高真空度的晶圓級真空封裝,以及縮小動件與電極間的間隙。以下將針對國外各重點研究機構以及公司所發展之製作方法做一簡單的介紹。

首先,圖4為一可整合積體電路與MEMS元件在同一晶圓上的多晶矽面型微加工基本流程圖,為一種將多晶矽直接沈積於互補式金屬氧化物半導體(CMOS)積體電路上並形成多晶矽為材料的MEMS微結構。其做法為在CMOS積體電路製作完成後,於其上沈積犧牲氧化層,並在犧牲氧化層上沈積多晶矽材料,如圖4(a),然後利用氫氟酸(HF)溶液將犧牲氧化層去除,如此即可形成可動的MEMS元件,如圖4(b)所示。

|

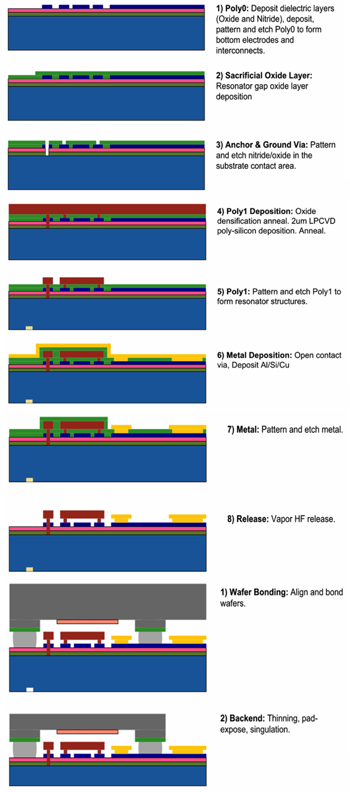

| 圖5 Discera MEMS振盪子製程示意圖 |

值得注意的是,為了使CMOS的金屬連線能夠承受沈積多晶矽材料時625℃的高溫製程,此一振盪器的CMOS製程係選擇鎢為連線材料;為了使目前常用的金屬連線材料,如銅與鋁,能夠與MEMS結構之製程相結合,目前亦有多晶矽鍺(Polycrystalline-SiGe)低溫沈積技術的研發,用以克服製程溫度的問題。

這種做法的優勢在於可與CMOS電路整合,然而目前低溫多晶矽鍺製程尚未臻成熟,目前還未有商業化的振盪器元件使用此種製程。

而Discera使用的製作方法與上述方法相當類似(圖5),其不同之處在於,為了得到品質穩定的多晶矽,其沈積溫度仍須高於CMOS電路可忍受的450℃,因此基板須置換為可忍受高溫製程的矽基板,在晶圓級真空封裝上,則是以傳統的玻璃介質(Glass Frit)做為接合材料,但在封裝上蓋置入一個Getter,用以吸收真空空間中的離子。

|

| 圖6 MEMS First製程置側面示意圖 |

另一國際大廠SiTime亦提出一名為MEMS First的專利製程(圖6),該製程利用EpiSeal技術將共振器於高真空環境下包覆於矽晶層之中,如此可提高振盪器的可靠度與準確度。圖6為該製程的側面示意圖,其做法為:在一Device Layer為10~20微米的絕緣層上覆矽(SOI)晶片上以深離子蝕刻技術形成寬度為0.4微米(μm)的深溝,並以此深溝形成振盪器共振腔的形狀,接著再以氧化矽(SiO2)材料填入深溝中,並將晶片置入多次磊晶爐(Epitaxial Reactor)中以沈積多晶矽(Poly-Si)薄膜。為了清除留在深溝的氧化矽,在共振腔結構上方蝕刻多個小孔,並由這些小孔將共振腔內的氧化矽去除,接著再將晶片置入多次磊晶爐中以1,000℃的高溫將晶片上的污染物去除,並在此時以磊晶的方式將小孔密封,以及成長共振腔上的密封多晶矽上蓋,最後則在以深離子蝕刻技術蝕刻多晶矽上蓋形成深溝,用以形成電性絕緣的鑽孔(Via),最後以化學機械研磨(CMP)法將上蓋表面磨平。

|

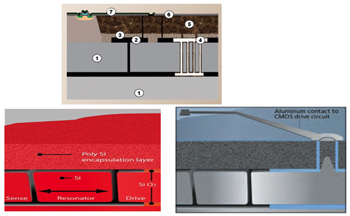

| 圖7 SiTime共振腔結構後之SEM照片 |

圖7為完成共振腔結構後之SEM照片,其共振腔因為是在高度潔淨和高度真空的環境下密封完成,因此可確保其產品的準確度及可靠度。另外,在封裝的製程上也可使用一般封裝製程,因此能夠節省封裝製程的成本。

MEMS振盪子之補償

一般MEMS振盪子因採用矽(Silicon)做為振盪結構,因此其在頻率對溫度的穩定性上一般表現較差(約為-30ppm/℃)。振盪子的共振頻率會隨著溫度變化上升或下降,主要是受結構材料本身的楊氏係數對溫度的變化率、熱膨脹係數以及品質因子等因素影響。為了改善此問題,一般可藉由溫度補償的方式來改善。在溫度補償中又可分為主動式(Active)與被動式(Passive)溫度補償。

| ‧ |

|

| |

一般被動式溫度補償主要是採用複合材料做為MEMS振盪子的振盪結構,由於矽材料是一種熱膨脹係數為「負」的材料,會導致共振頻率因升溫而減少,因此一般會採用熱膨脹係數為「正」的材料,如氧化矽,與矽振盪子做為複合材料的振盪結構,則可因為二氧化矽是一種膨脹係數為正的材料,將會使振盪子的共振頻率因升溫而增加,如此利用兩種正、負熱膨脹材料的組合和其所具有的不同楊氏係數對溫度的變化率所形成的複合材料,將有機會在適當的材料設計比例上,得出此複合材料結構振盪子的適當操作溫度,而在此適當操作溫度時,複合材料結構振盪子之共振頻率隨溫度變化的大小是零。 |

| ‧ |

|

| |

MEMS振盪器的主動式補償通常需要溫度感測器(Temperature Sensor),以及致動器(Actuator)達到主動式閉迴路控制的功能。過去常見的方式是在振盪器的電路端製作溫度感測器,並透過調整振盪器體電壓的方式來改變振盪子的輸出頻率,如圖8所示,此為羅伯特博世(Robert Bosch)於2006所提出之專利US7068125。另一種方法是史丹佛大學Kenny教授研究團隊所提出的主動式溫度補償方法,如圖9所示。主要是利用兩振盪子,其中一個做為溫度計,另一做為振盪源輸出,並設計了加熱器做為致動器,持續對振盪子加熱,讓振盪子能夠維持恆溫而不受到外界溫度變化影響,因此可保持振盪子之輸出頻率穩定。 |

MEMS振盪子未來發展無限

輕薄短小迄今仍是3C電子產品以及穿戴式智能產品的主流趨勢。因此,微型化與低耗能的MEMS振盪器將是時序元件業者未來在競爭激烈的市場中突圍的利器。從MEMS振盪器產品技術發展來看,目前國外廠商占有絕對的領先優勢,包括SiTime、Discera、恩智浦(NXP)、博世、Ecliptek、意法半導體(ST)等皆積極投入研發;國內廠商亦已逐步切入該技術領域。

由於MEMS振盪器須具備與石英振盪器相同的外部性能規格及較低的成本,才能在市場上藉由其微型化與可程式化調整的優勢取代石英振盪器。因此MEMS振盪器的設計必須能具備低電壓操作、高頻率穩定性和可量產化等必要條件。工研院南分院長期投入MEMS振盪器的開發,無論從設計到製作與產品的封裝測試已有完整的技術能量與專利布局,特別是在高頻率穩定性的複合材料MEMS振盪器,以及具備高品質因子的聲子晶體結構MEMS振盪器的技術開發上,已達到國際大廠的性能水平,在某些性能上甚至已經超越國際大廠的規格(如頻率穩定性)。

未來MEMS振盪器的發展,首先在設計上必須能事先辨識潛在性問題,如製程的不完美性(Fabrication Imperfection),一直到封裝層級的影響,須藉由設計將可能的問題解決,以提升開發效率。雖然目前MEMS振盪器在頻率穩定性(PPM)等性能尚無法與大多數石英振盪器競爭,但其可微小化、批次量產及較低封測成本等特色,已引起市場高度重視。長期看來,由於半導體及微機電製程日益成熟,而台灣則是產業重鎮,因此相當有優勢投入發展。

(本文作者為工研院南分院微系統中心微元件技術部研發副理)