合成器可採用單迴路或多迴路鎖相迴路(Phase-locked Loop, PLL)的方式設計,但不可避免地都必須謹慎處理雜訊及寄生的問題。單迴路設計有其先天上的限制,所以多迴路PLL是目前主要的發展方向。

PLL可用於各種用途,包括頻率合成在內。成功的合成器設計主要取決於工程師的選擇,例如究竟要採用單迴路或多迴路方法,以及一些重要的設計考量,例如雜訊和寄生。

PLL為線性控制系統

為充分了解會對PLL產生影響的選擇和設計考量,首先必須認識PLL的基本概念。PLL在穩態下為一線性控制系統,必須考慮的變數為相位。Laplace的s域分析,可用來預測迴路的穩定度及相位雜訊效能。

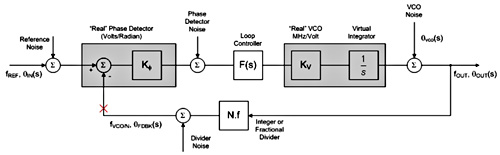

圖1為PLL的基本方塊圖。PLL的「輸入」為參考頻率,輸出頻率為fout=N.f‧fIN。使用整數除法器時,輸出頻率的步進單位會與參考頻率相同。若使用分數除法器,輸出頻率的步進單位會遠比參考頻率小。然而,分數除法器會產生嚴重的雜波問題,而且在相位雜訊效能上通常比不上整數除法器。

|

| 圖1 基本的PLL方塊圖,其中包含各種雜訊源。 |

開迴路轉移函數(Open Loop Transfer Function)即為迴路增益GH(s)。分析GH(s)可以得到以相位邊限(Phase Margin)來表示的迴路穩定度資訊。參考頻率、相位偵測器與N除法器的雜訊會執行低通轉移函數,亦即迴路會斥拒超出迴路頻寬(BW)以外的雜訊。

電壓控制振盪器(VCO)雜訊會執行高通轉移函數,在迴路頻寬內的VCO雜訊將會被斥拒。迴路控制器F(s)通常為一個帶0的積分器,但也有可能使用較複雜的網路。

為建立與各種PLL元件有關的雜訊之模型,可以使用下列方程式:

其中,L(f)是在偏離載波的某個頻率下的單旁波帶(SSB)相位雜訊,Sφ(f)為雙旁波帶相位雜訊或功率頻譜密度。各個係數(k0, k1, k2, k3)代表每十倍頻為10dB、20dB和30dB的雜訊底線範圍。Lesson的模型預測射頻和微波振盪器擁有平坦的1/f2和1/f3範圍,而高Q值振盪器(石英和表面聲波振盪器)則擁有平坦的1/f和1/f3範圍。

另外,除法器和相位偵測器會擁有平坦的1/f或閃爍範圍。以一個微波VCO為例,假設已知雜訊底線,1/f2範圍中的一個點(dBf2_VCO, f2_VCO),以及1/f3範圍中的一個點(dBf3_VCO, f3_VCO),那麼就可以得出下列雜訊方程式。

將輸入雜訊源乘以N,可以得到一般所稱的遠端(Pedestal)相位雜訊。最理想的迴路頻寬,乃是遠端相位雜訊越過VCO相位雜訊的位置。總雜訊為迴路修正遠端雜訊(經低通濾波器處理)和VCO雜訊(經高通濾波器處理)的總和。對輸出雜訊取以10為底的對數(小於3dB),可以得到最終的SSB雜訊。

單迴路優點多但有限制

單迴路鎖相迴路是一個經濟又有效率的合成器解決方案,融合適中的效能、小巧的體積和低操作功率。使用商用元件如分數N型特殊應用積體電路(ASIC),並經過細心的模型建立程序,可讓迴路達到最佳狀態,以提供具有合理的相位雜訊和寄生效能及精細頻率解析度的訊號。

多迴路有改進性能提升

單迴路方法雖經過最佳化處理,但仍有其限制。高效能合成器會使用多個PLL,因為它們比簡單的單迴路分數N型(FN)合成器提供更佳的相位雜訊和雜波效能。

多迴路合成器有許多種配置。偏移或步進迴路會產生粗略的頻率步進,而精細迴路(或DDS)則會產生一個低頻的倍頻程寬(Octave-wide)訊號,具有介於粗略步進之間的精細解析度。總和迴路會將這兩個訊號加在一起。

一般而言,偏移迴路和主參考頻率雜訊為近端雜訊效能,而總和迴路的VCO為遠端雜訊效能。精細迴路應該為二階因素。由於總和迴路中包含混頻器,所以必須小心處理頻率計畫,以避免在迴路頻寬中出現任何雜波。

某些廠商的產品如安捷倫(Agilent)的N5181B/N5182B訊號產生器採用此種三迴路方法。其中的分數N型迴路,會產生62.5M~125MHz的頻率。偏移迴路所輸出的3G~6GHz頻率(以125MHz為步進單位)與總和迴路的VCO輸出頻率混頻後,會產生一個中頻(IF),其與FN迴路所產生的參考頻率相同。上旁波帶與下旁波帶經過混頻後,即可獲得完整的頻率範圍。

參考頻率方塊會產生一個100MHz的超低雜訊,其會被鎖定到高品質的10MHz參考頻率。從這個100MHz雜訊,可以產生FN迴路的50MHz參考頻率。在偏移迴路會以500MHz為步進單位,產生從3G6GHz不等的一連串頻率。在偏移迴路還會多產生62.5MHz和187.5MHz兩個參考頻率。

偏移迴路是另一個選擇

偏移迴路中的頻率,全都與n*500MHz有關。因此,即使迴路中包含混頻器,也不會出現交叉雜波,且距離載波最近的雜波為62.5MHz。為使迴路鎖定在適合的旁波帶,所以有必要執行VCO控制(VCO Steering)。

偏移迴路的近端相位雜訊,是n*500MHz雜訊與62.5MHz或187.5MHz參考雜訊,以及相位頻率偵測器雜訊的總和。利用完美的乘法,將100MHz的VCXO訊號變成500MHz,然後再形成各種諧波。為了將額外的雜訊源考慮進來,所以加入一個誤差係數(Fudge Factor)。

3G6GHz的VCO具有很差的相位雜訊。因此,偏移迴路需要一個寬迴路頻寬來斥拒或排除VCO雜訊。偏移迴路控制器包含一個差動式低通濾波器、一個低雜訊的差動轉單端式儀器放大器和以變動的KV來控制迴路增益的步進衰減器。以上每一個方塊,包括VCO調諧埠在內,都會在迴路中增加相位位移,這會嚴重影響到相位邊限,從而降低迴路的穩定度。

差動式低通濾波器會從相位偵測器斥拒62.5MHz的雜訊,所以不會在偏移迴路的載波產生旁波帶。這些旁波帶會在總和迴路中互相作用,因而在最終輸出產生一個近端雜波。設計此種濾波器的代價是,必須在62.5MHz的頻率進行最大衰減,同時在增益交越點(Gain Crossover)維持較低的相位位移。在濾波器的通帶中,相位位移估計約為一個固定時間延遲。

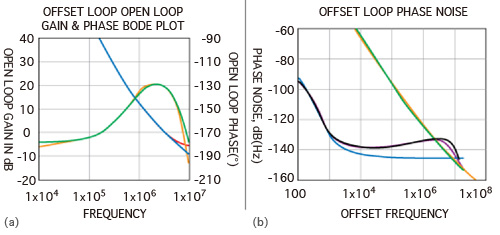

運算放大器(Op Amp)和VCO方塊,是以簡單的時間延遲來建立模型。為擁有平坦的頻率衰減,特別設計領先落後(Lead Lag)總和網路。圖2(左圖)顯示增益交越點和開迴路轉移函數使用24奈秒(ns)的延遲。

|

| 圖2 波德圖(Bode Plot)和雜訊圖顯示模型與量測結果相當一致。相位邊限約為48度。 |

使用低通和高通迴路轉移函數及各種雜訊源方程式,可以計算出偏移迴路雜訊:

迴路中的相位偵測器、參考頻率和其他雜訊源,總共會使相乘的參考雜訊變差約5dB。迴路頻寬設在約3.2MHz的範圍,這會導致很大的相位雜訊峰值,而被總和迴路所衰減。圖2(右圖)顯示了偏移迴路雜訊。

改用分數N型迴路/總和迴路

FN迴路會產生一個1G2GHz的輸出頻率,將其除以16可以產生輸入到總和迴路的62.5M125MHz參考頻率。FN迴路採用安捷倫專屬的晶片組,參考頻率為50MHz,其在雜訊和寄生效能上表現出色。

因為使用除法的關係,在輸入總和迴路前,FN迴路中的雜訊和雜波就降低24dB。同樣的方法可用來分析這個迴路。在輸入總和迴路之前,將1G2GHz的輸出頻率除以16,以產生62.5M125MHz的頻率。相除過的分數雜波會小於-90dBc。

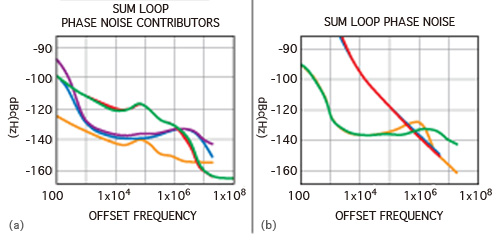

總和迴路使用一個低雜訊的0.75G1.5GHz VCO,經過相乘後頻率可達3G6GHz。輸入總和迴路的參考頻率,即為除過的分數N型迴路頻率。在回饋路徑中使用混頻器,還可將偏移迴路加進來。由於總和迴路的IF頻率(混頻器輸出)遠低於偏移迴路(混頻器輸入),所以混頻器的交叉雜波會處於高值位(High Order),並因此落在很低的位準。圖3顯示以下列方程式所算出的總和迴路雜訊。

|

| 圖3 總和迴路的雜訊因素和最終輸出的雜訊 |

使用數學運算軟體來執行what if假設情境分析,可以輕易地調整不同的迴路參數,例如增益交越點、極點和零點的位置及迴路中的各種雜訊源,以便達到最佳的效能。接下來還可以計算元件值並使用電路模擬器來驗證每個迴路的效能。

多迴路PLL將是發展標的

不論單迴路PLL經過何種程度的最佳化處理,仍然會有一些限制。多迴路解決方案可以大幅改善近端和寬廣偏移雜訊及寄生效應。只要使用適合的設計與模型建立方法,多迴路PLL便能有效率地達到嚴苛應用所需的效能。

(本文作者任職於安捷倫)