可攜式裝置設計不斷努力在整合各種高耗電量的功能和更長電池壽命這兩項矛盾的目標中取得平衡。為了將系統中不必要的功率浪費降到最低,各種新型電源管理技術紛紛出籠。然而,電池中儲存的寶貴能量仍可能在不知不覺中流失,例如ICCT電流便是造成浪費的隱形原因之一。本文將探討在混合電壓供電的可攜式設計中,如何透過邏輯元件改善此一現象。

對行動運算裝置與智慧型手機設計團隊而言,延長電池壽命是無止境追求的設計目標。然而與此矛盾的是,市場一方面希望可攜式裝置的電池壽命能持續延長,另一方面又必須透過整合新功能來替終端產品找賣點,因此設計人員除了必須採用先進的電源管理架構外,更必須仔細檢視系統設計中任何可能浪費電源的每一個細節。I

CCT電流便是一種常被設計人員忽略的隱形功耗來源,透過先進的邏輯技術,可以將此一浪費降至最低,從而延長系統的電池壽命。

ICCT電流為隱形功耗

目前大多數可攜式設備系統中都採用多個供電軌,以滿足輸入/輸出(I/O)、核心處理器、射頻(RF)等不同性質的元件需求。但當輸入高電平(VIH)不等於電源電壓(VCC)時,便可能由於ICCT電流出現而造成隱藏性的功耗。

|

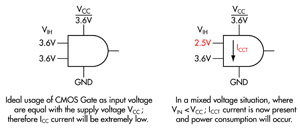

| 圖1 邏輯和輸入電壓條件 |

當輸入電壓等於供電軌電平(VIL=GND或VIH=VCC)時,互補式金屬氧化物半導體(CMOS)元件通常具有極低的靜態電流(ICC)和洩漏電流,對行動應用所使用的邏輯元件而言,這是最理想的技術。不過,若VIH小於VCC的話,則會發生輸入級的P型金屬氧化物半導體(PMOS)和N型金屬氧化物半導體(NMOS)電晶體在不同級導通的現象,從而傳導電流。在這個狀態期間,靜態電流ICC增加,造成一條從VCC到接地(GND)的路徑。這個增加的電流被稱為ICCT電流(圖1),亦是輸入電壓逼近閾值時的電源電流。

輸入電壓等於電源電壓VCC時,為使用CMOS電路的理想狀態,這時ICC電流極低。但在混合電壓的情況下,若VINCC,ICCT電流便會出現,功耗也隨之產生。由於當輸入電壓為0伏特或等於VCC時,CMOS元件的耗電量極低,因此產品資料手冊通常也會註明該條件下的ICC。不過,若設計人員以為ICC是一個定值的話,那可就大錯特錯了。以VIH值小於VCC的情況為例,這時元件的ICC電流一定比資料手冊所註明的ICC來得大。

一般在CMOS電路的設計中,輸入電壓閾值或輸入切換點為VCC/2;不過,目前市場上已經有晶片供應商為解決ICCT的問題開發出低ICCT閘電路。這類元件通常採用專有的輸入電壓設計,可降低輸入閾值電壓,增大輸入電壓範圍,同時不影響有效邏輯低電平(VIL)。

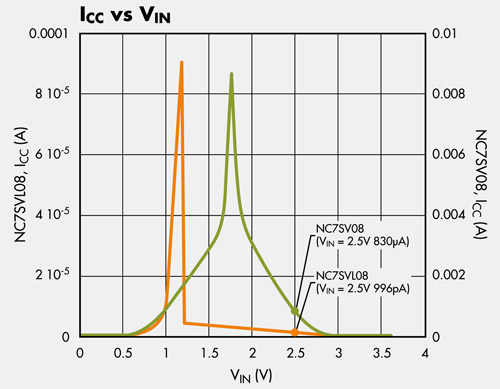

圖2中標準CMOS輸入元件(實線)和低ICCT輸入元件(虛線)的比較可以看出重新設計的輸入結構所具備的優點。靜態功率由基本DC功率公式決定:P=ICC×VCC。在本例中,輸入(VIH)為2.5伏特,標準CMOS閘電路輸入的功耗為3.0毫瓦,而低ICCT邏輯閘電路的功耗只有0.003毫瓦,亦即利用低ICCT元件,靜態功耗可降低近100%。

|

| 圖2 ICC-VIN輸入曲線(VCC=3.6V,VIN=2.5V) |

由於ICC電流不是定值,其幅度隨VCC與VIN間的差距而改變,因此這類低ICCT邏輯節省功耗的效果須視情況而定。表1為快捷(Fairchild)所提供的NC7SVL低ICCT邏輯在不同VIH條件下的表現。

電池壽命得來不易 邏輯元件選擇不容輕忽

對於功率預算十分緊張的可攜式應用產品來說,任何不必要的耗電都是不能接受的,若設計人員想將電池使用時間延到最長,其要訣為降低各級的功率。隨著可攜式設備整合更多的功能,功耗問題漸漸成為一個隱憂。低ICCT邏輯元件可為設計人員提供一個具成本效益的解決方案,以解決這些難題。

(本文作者任職於快捷半導體)