最近推出的跨電感電壓調節器(TLVR)在多相DC-DC應用中頗受歡迎,這些應用為CPU、GPU和ASIC等低壓大電流負載供電。此一趨勢主要基於該技術的瞬態性能。TLVR並支援彈性的設計和布局,但其同時也存在幾個缺點。本文闡述了TLVR設計選擇如何影響性能參數,並根據優缺點討論相關權衡方式。

TLVR降壓器電流漣波與瞬態

對於許多高電流應用而言,多相降壓轉換器的任何改善都有意義。瞬態性能改善尤其值得關注,因為許多CPU、GPU和ASIC現在都有非常嚴格的瞬態規格,而高效率對於節能和熱性能也非常重要。

電感中的電流漣波是影響設計選擇的重要參數:其影響效率和輸出電壓漣波,並間接關係到瞬態性能、解決方案尺寸和其他性能指標。另一個關鍵特性是瞬態條件下的電流擺率,這是瞬態性能的基本限制因素。通常,電流漣波(以及效率)和瞬態性能(直接影響輸出電容大小等因素)導致設計決策需要權衡。

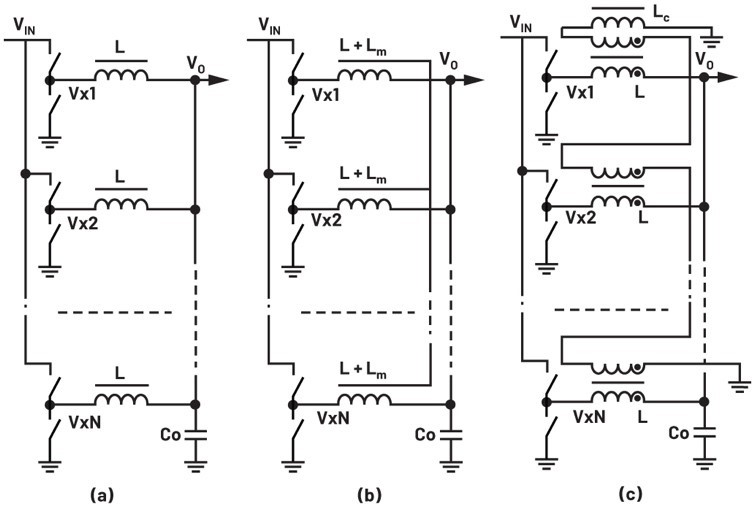

採用分立式電感(DL)的傳統多相降壓轉換器如圖1a所示。為了實現較理想的波形交錯,假定所有相位之間都具有適當的相移。一種替代方案是用耦合電感(CL)取代DL,如圖1b所示。另一種替代方案則如圖1c所示,稱為TLVR,其中調諧電感Lc會影響電流漣波和瞬態性能。TLVR方法的原理是向分立電感增加次級繞組,並透過次級繞組的電氣連接來連結相位。此種設計思路類似於耦合電感,主要是對所有連結相位之間的交流波形進行平均,以在特定瞬態擺率下獲得更好的電流漣波,但TLVR的有效耦合電感是有限的,因為必須考慮全部相電流。TLVR的缺點是TLVR變壓器不能傳送電流的直流部分,因此直流電不會像在磁耦合電感中那樣在相位之間抵消掉。本文將重點介紹TLVR的更多細節和特定權衡。

圖1 多相降壓轉換器,分別採用(a)分立電感(DL)、(b)耦合電感(CL)和(c)TLVR

圖1 多相降壓轉換器,分別採用(a)分立電感(DL)、(b)耦合電感(CL)和(c)TLVR

TLVR中漣波和電流擺率的第一個數學模型及公式可能已出現在相關文獻中。雖然這是一個非常有用的數學模型,適用於任何電路條件(任何工作週期D=Vo/VIN或多個相位Nph等),但其有一些局限性。例如,低Lc值(圖1c中的調諧電感)會導致誤差增加,當Lc=0時,誤差變得無窮大等等。低Lc值的極端情況比Lc=開路的極端情況更重要,因為使用TLVR的主要原因是改善瞬態性能,表示Lc值相當低。

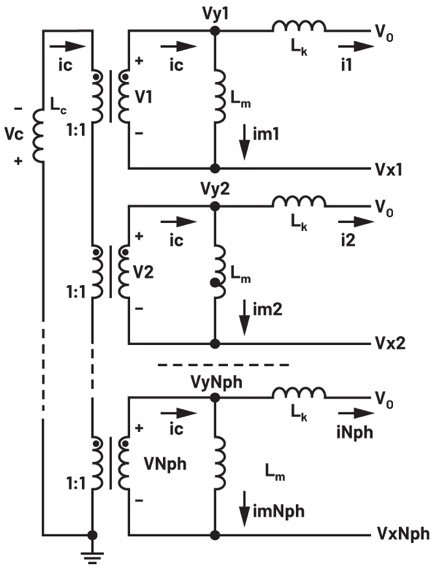

此外並提供了更精準的TLVR推導,透過指定適當的Vx狀態,推導出的公式可以得出穩態(對於電流漣波)或瞬態下的電流擺率。該推導是針對更精準的等效TLVR原理圖(圖2)進行的。此模型與任何極端情況下的模擬都具有極佳的相關性,但穩態下的電流擺率僅對1/Nph範圍有效。後者是可以接受的,因為經由實際的證明顯示,恰好在1/Nph區域TLVR具有相對於DL基線的最大電流漣波增量,並且當Nph夠高時,其將會接近DL漣波。

圖2 多TLVR模型

圖2 多TLVR模型

TLVR值在產品手冊中的顯示方式通常與分立電感DL相同,並且從中可推導出TLVR。圖2中的模型假設TLVR總值或自感被分成兩部分:一個是通常較小的Lk,其餘部分實際上成為TLVR變壓器的互感Lm=TLVR-Lk(公式1)。

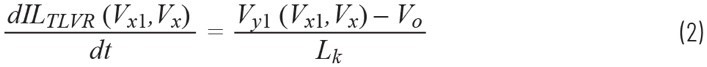

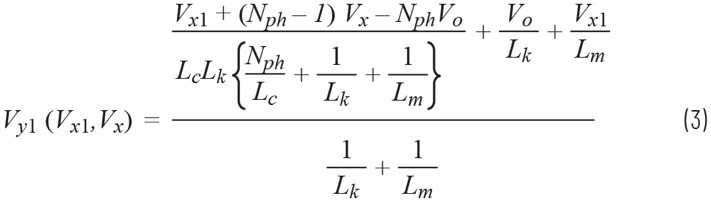

基於圖2中的模型,TLVR中的電流擺率可用公式2表示,其中Lk是主繞組和輔助繞組之間的TLVR漏感。Vx1電壓分配給目標相位而所有其他Vx節點均假定具有相同電壓(VIN或0)。相應的節點電壓Vy1如公式3所示。強制Vx1=Vx,並將這些電壓指定為VIN(斜坡上升)或0(斜坡下降),便可使用公式2直接計算TLVR中的最大瞬態擺率。此外,公式2中的電流擺率可用於公式4中的穩態漣波計算,其中Vx1=VIN,所有其他開關節點均為Vx=0。不過,公式4僅對1/Nph有效,因為其假設全部導通時間D/Fs內具有單一且相同的擺率。

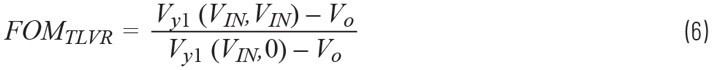

如文獻所述,品質因數(FOM)是反映系統性能的一個良好指標,最大化FOM通常是實現理想權衡的正確方向。但請注意,高FOM本身並不能確保特定應用規格中的每個參數都得到滿足,高FOM僅是良好設計的一個指標。FOM的定義如公式5所示,這對於1/Nph範圍是合適的,可以用公式6來表示TLVR FOM。

為了進行比較,使用CL方程式(此處未顯示),但重點關注TLVR性能和權衡。並使用陷波耦合電感(NCL)結構作為基準,與尺寸和大小相容的特定TLVR=150nH解決方案進行比較。

多相設計/決策/權衡 TLVR性能提升有撇步(1)

多相設計/決策/權衡 TLVR性能提升有撇步(2)