商用現場可編程閘陣列硬體模擬器(FPGA-based Emulator)與定製矽硬體模擬器(Custom Silicon Emulator)之間的根本區別在於映射被測設計(DUT)的核心單元。顧名思義,定製矽硬體模擬器是基於定製元件而造,不可用於商業用途。

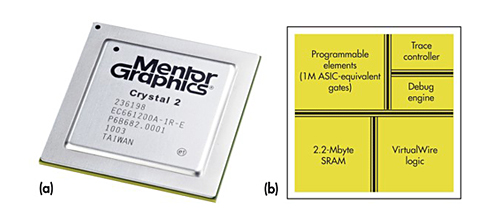

在商用FPGA硬體模擬器中,核心單元是專為硬體模擬應用而設計的定製FPGA,但通用FPGA是個糟糕的選擇,因此有廠商提供一種稱為Crystal2的系統單晶片(SoC),並稱之為定製片上硬體模擬器(Custom Emulator-on-chip),如圖1。

|

| 圖1 Crystal2定製片上硬體模擬器外觀與內部架構 |

定製FPGA硬體模擬器三大新創架構

在定製矽硬體模擬器中,核心單元包括大量簡單的布林處理器,此類處理器在巨大的記憶體中執行設計資料結構存儲,供應商稱之為「基於處理器的硬體模擬器(Processor-based Emulator)」。很顯然,定製FPGA硬體模擬器與商用FPGA硬體模擬器具有一些相似之處,但仍各自具備獨特的功能。

事實上,定製FPGA硬體模擬器係由法國初創公司MetaSystems最先開發並商業化,採用不同於賽靈思(Xilinx)和Altera所提供的獨特FPGA。

該硬體模擬器是基於定製矽上模擬器架構,專為涵蓋整個硬體模擬器(包括可配置單元、局部互連矩陣、嵌入式多埠記憶體、I/O通道、帶探測電路的除錯(Debug)引擎和時脈產生器)的模擬應用而設計。

另外,該設計使用三個創新特點,每個創新點都可提供獨特的優勢,分別為可程式設計單元的內部互連網路;定製FPGA的外部互連網路和I/O結構;DUT除錯引擎(DUT Debug Engine)。

可程式設計單元內部互連網路

可程式設計單元的互連網路包括兩個不同分級層,位於查閱資料表(LUT)及其集群(Cluster)級別的低層,以及更大塊的LUT集群,即所謂的疊塊的高層。

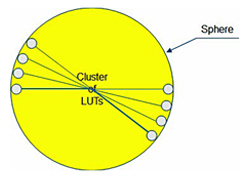

空間類推法可用來描述低層。假設所有的LUT都位於球體表面上,任何兩個LUT互連都必須穿過球體中心,則無論兩個LUT位於何處,互連導線的長度始終相同(圖2)。

|

| 圖2 低層級空間類推法 |

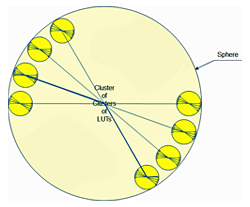

上述類推法延伸到更高層級,LUT集群可以分布在更大球體的表面上,並採用相同的方式互連,如圖3。這基本上是一個重複相同模式的分形圖,從外到內或從內到外移動,高層(Clusters of LUTs)透過專利結構彼此互相連結溝通,提供類似於低層(LUTs Inside Cluster)固有的優勢。

高層通過微小的交互開關矩陣(有些類似於片上網路(NoC)架構)互連疊塊,使該結構有別於傳統網格互連網路,確保布線可預測、快速和無壅塞。

|

| 圖3 高層級空間類推法 |

此外,要注意的是,不可預測的時序和保持時間違規行為會破壞商用FPGA的可用性,而時鐘樹(Clock Tree)透過導線連接到獨立於資料路徑的專用路徑,因此可以預測和重複時序,並通過構造防止時序違規行為,因為資料路徑比時鐘路徑更長。

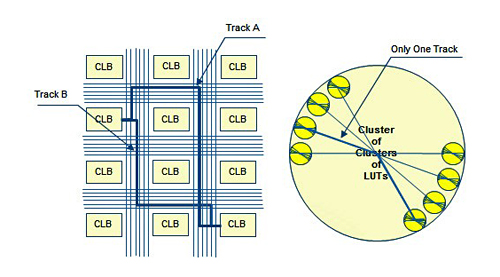

與商用FPGA的結構相比,定製方法可以確保時序的確定性和可重複性,並消除了布局約束,確保實現簡單的布線和快速的編譯(圖4)。

多層互連網路技術與高FPGA容量之間為彼此權衡,並可支持快速和無壅塞(Congestion)的FPGA布局和布線(P&R),約在5分鐘內可對一個定製FPGA進行布局布線。相對於將商用FPGA的填充率降低至50%或以下,布局和布線仍可能需要幾個小時。

|

| 圖4 商用FPGA(右)與定製方案(左)的對比 |

毫無疑問地,與使用目前市場上最大的商用FPGA晶片如Virtex-7 XC7V2000T相比,映射十億特定應用積體電路(ASIC)等效邏輯閘設計將需要更多的定製FPGA晶片。但兩者實際差異可能會小於通過比較內部資源(例如LUT)估算的結果,因為定製FPGA的利用率接近100%,而商用FPGA則為50%左右。

以下因素有助於減輕容量差距,包含內置的VirtualWire邏輯(用於I/O數最大化而不是消耗LUT);內置的除錯引擎(將寶貴的可配置邏輯陣列留給DUT映射而不須因為除錯耗用LUT數目);以及一個有效的布線器。

其實這兩種技術都受益於在多個PC上分配布局和布線,但定製方法仍然具有優勢。在一系列定製FPGA上對十億ASIC等效邏輯閘設計進行布局和布線(在大型PC Farm上進行P&R)需要30分鐘;在一系列較小的Virtex-7上對相同的設計進行布局和布線將需要幾個小時。

藉由該技術,定製FPGA硬體模擬器供應商可以獨立營運開發,優化和定製布局和布線軟體,而這是商用FPGA硬體模擬器供應商無法做到的,因為後者受FPGA廠商支配。

片上硬體模擬器的外部互連網路和I/O架構

片上硬體模擬器的外部互連網路是基於所謂的VirtualWire技術,FPGA晶片之間會自動在編譯過程中視為一個巨大的FPGA(Single Giant FPGA),此大FPGA不會受到透過傳統方式互連的一系列等效FPGA的潛在時序問題的影響。該技術在開發時僅可用於採商用FPGA的硬體模擬器,現在,相同的技術已嵌入到片上硬體模擬器。

事實上,VirtualWire是基於多個再合成(Re-synthesis)流程(包含時序(Timing)、記憶體(Memory)、互連(Interconnect),此類流程係將DUT轉換為映射到一系列定製片上硬體模擬器元件的功能等效的設計。

時序再合成使用可保證功能正確優先原則,來轉換重新定時用戶的設計,藉由引入單個高速時鐘來保護其免受不準確的FPGA延遲。此外,還消除了傳統硬體模擬系統的保持時間(Hold-time)問題。

記憶體再合成因毋須構建定製存儲卡或使用FPGA記憶體,從而實現低成本實施各類記憶體(包括多埠RAM)。據了解,多工和記憶體共用的設計支持快速且便宜的常見SRAM晶片進行記憶體硬體模擬。

互連再合成透過在元件(Device)固定和有限數量的I/O接腳上,增加傳輸中的I/O訊號數,來擴展元件間的通訊頻寬,並以最大速度進行連接,最終結果是,元件利用率大幅提高到約100%,避免壅塞並維護DUT完整性。在每個I/O接腳增加I/O訊號類似於在FPGA原型板上實施I/O數最大化的方法。若以VirtualWire技術實現則更為複雜;該技術透過保證局部時序正確性,實現全域時序正確性和系統可擴展性;同時提供為所有觸發器(Flip-flops)計時的虛擬時鐘(Virtual Clock),分配單個同步低偏移時鐘;另外,訊號布線和調度受編譯器控制,因為訊號必須通過已知數量的FPGA。

VirtualWire還擴展了頻寬,從而提高FPGA和導線的利用率;多工技術可以擴展各級封裝的互連頻寬,從FPGA間和板卡之間到主機殼間,使得分區更容易。

值得注意的是,VirtualWire還提供相同的多工技術來訪問記憶體,透過對資料匯流排進行多工,可以使用常見的SRAM晶片構建寬記憶體;實施多埠記憶體;並在布線和調度步驟中整合記憶體調度。

整合設計除錯功能

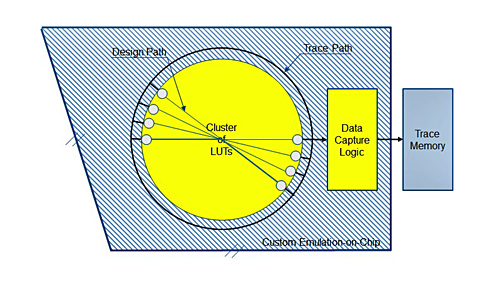

第三個創新涉及定製方法的整合設計除錯功能,是基於在晶片內部實施的即時智慧資料捕獲和安裝在模擬板上每個晶片旁邊的跟蹤記憶體(Trace Memory),可以確保監控DUT的所有單元,是透過構造而非編譯內部探頭(Probe)實現的,還能避免硬體模擬速度下降。

利用所有LUT和嵌入式記憶體輸出連接到晶片上訊號探測電路實現全面監控,可省去在編譯時的布線工作,接著,探測電路會依次將探測資料定向到快速記憶體晶片庫,該庫耦合到安裝在模擬板上的定製片上硬體模擬器元件,如此一來就可預留布線資源來構建電路設計映射,提高可重新配置硬體的效率(圖5)。

|

| 圖5 預留布線資源來構建設計圖片,提高可重新配置硬體的效率。 |

整合觸發機制和圖形化電路實體路徑瀏覽器的內置邏輯分析儀能夠增強設計除錯功能,以加快識別難以發現的缺陷。預設情況下,片上硬體模擬器啟用觸發(Triggering)、暫存器(Register)、強制與解除(Force/Release)、記憶體/暫存器讀寫,以及中斷點保存與恢復。

遺憾的是,與最大的商用FPGA相比,定製方法也有缺點。因為定製晶片的容量密度較低,要映射任何給定的電路設計,硬體模擬器將需要更多的FPGA,從而導致物理尺寸更大、重量更重。

粗略估計,與具有相同設計容量的商用FPGA硬體模擬器相比,定製晶片的尺寸大一個數量級;重量約重五倍;功耗約高四倍以上。

況且,商用FPGA硬體模擬器的原始時鐘速度更快,據公開資料顯示,似乎比片上硬體模擬器快兩倍,這同樣起因於兩種晶片的容量差異。事實上,具有更大容量的現成FPGA可以容納電路設計的更大部分,並只需更少的元件以映射整個設計。最終結果是,互連導線更短,傳播延遲更快。

但是,若要利用這種功能,則需要耗時的手動分區;如果沒有優化分區和消除跳距--即組合導線跨越多個FPGA,那麼在商用FPGA硬體模擬器中,模擬速度可能會下降。

(本文作者為明導國際特約技術專家)