I2C匯流排的發展始於1980年代初期。而在1990年代前期,英特爾(Intel)創造了I2C的進階版本,稱之為系統管理匯流排(System Management Bus, SMBus),此一進階版本係針對伺服器以及PC內部的電源和散熱管理系統的需求而制訂。

到了2000年代初期,SMBus被選擇作為電源管理匯流排(Power Management Bus, PMBus)的實體介面,PMBus為模組化電源系統的開放規格,這也為I

2C/SMBus產品開闢了另一市場。時至今日,由於其低成本和低耗電、加上強大的產業支持與其極具效率的通訊協定,I

2C匯流排仍不斷地成長及普及,因此現今許多新推出的終端應用皆已採納I

2C。

在許多此類的應用中,基於安全或消除接地迴路的需求,I2C/SMBus介面須進行電化隔離。例如乙太網路供電(Power over Ethernet, PoE)應用,一般須在PoE供電設備(Power Sourcing Equipment, PSE)和接地系統控制器之間使用I2C介面,以進行溝通。無論出於標準規定或實際的考量,來避免乙太連網設備間產生接地迴路(Ground Loop),其電化隔離(Galvanic Isolation)是必要的。

此實體介面包括串列數據(SDA)和串列時脈(SCL)兩條線路。這兩條線路連接至開集極型驅動器(Open Collector Driver),作為輸入和輸出。乍看之下,似乎只要簡單地在平行和相反方向放入兩個單向隔離器,便能隔離SDA和SCL。然而,當主端或從屬端出現低邏輯電位(Logic Low)時,則此方法將產生會栓鎖住低電位匯流排線路的回饋。藉由加入防栓鎖電路(Anti-latch Circuits)可以解決此問題,然而這卻是一個體積龐大且昂貴許多的解決方案。

矽晶RF隔離技術的最新突破,例如芯科實驗室(Silicon Laboratorie)Si8400和Si8405的I2C雙向隔離器,則能將隔離和防栓鎖功能整合在單一封裝體中。針對須要隔離I2C/SMBus的應用所面臨的問題,這些產品提供單晶片的防鎖解決方案,且除了I2C/SMBus提升電阻(Pull-up Rresistor)外,此種解決方案毋需其他外部元件。此外,此元件提供最高達2.5KVACRMS的隔離值,支援時脈伸展(Clock Stretching),且操作最大匯流排速度為2Mbit/s。

有鑑於此,此篇文章將說明整合型I2C隔離器的運作,以及使用這些元件的設計限制和考量。

I2C隔離器旁加入防栓鎖

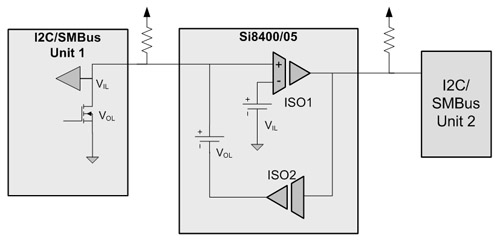

若無防栓鎖防護(Anti-latch Protection),則當隔離器輸出低邏輯電位透過相鄰隔離器通道傳回時,將會在兩側產生穩定低栓鎖電位的情況,如此便會導致雙向I2C隔離器被栓鎖住。一般是在隔離器的一側加入防栓鎖防護,以避免此情況(如Si8400/05的「A」側),如圖1。

|

| 圖1 使用Si8400/05的I2C範例 |

「A側」低輸出(VOL)和低輸入(VIL)電位的設計,是要讓隔離器VOL大於隔離器VIL,以防止栓鎖的情況。

I2C留意隔離器種種設計限制

除了前述的各種注意事項外,I2C設計時還須考量種種的設計限制,如表1所示。

| 表1 I2C設計限制和影響 |

| 設計限制 |

技術規格數值 |

匯流排提升強度和溫度的影響 |

為避免栓鎖情況的發生,隔離器輸出低電位必須大於隔離器輸入高電位。

|

典型的隔離器VOL 0.8V

典型的隔離器VIL 0.6V

輸入/輸出邏輯低電位的差異

ΔVSDA1, ΔVSCL1 =

50mV 最小值 |

這通常由隔離器的技術規格所保證。然而,若提升強度太弱,則輸出低電壓將下降,且可能會太接近於輸入低電位邏輯電位。這些會對溫度造成影響

|

匯流排輸出低電位必須小於隔離器輸入邏輯低電位 |

匯流排VOL = 0.4V 最大值

隔離器VIL = 0.545V 最大值 |

若提升強度太大,則匯流排上的這些元件可能無法將電壓拉低在輸入低電位範圍內。這些將產生相對的溫度係數。高溫是最糟的情況 |

| 隔離器輸出低電位必須大於匯流排輸入低電位。 |

匯流排VIL 0.3*VDD

= 1.0V 最小值VDD=3.3V

隔離器VOL = 0.9V最大值 |

若此提升強度太大,則隔離器可能無法將電壓拉低至低於匯流排輸入低電壓。

Si8400/05 Vol: -1.8mV/C

CMOS緩衝器: -0.6mV/C

這會影響溫度,而低溫為最糟的情況。 |

I2C匯流排須正確 連接隔離器A側

使用I2C隔離器的第一步便是選擇要讓匯流排的哪一側連接至隔離器A側。在理想情況下,選擇的那一側應該是:

|

|

| |

例如,Si8400/05隔離器一般是採用0.5毫安培至3毫安培的提升範圍。 |

|

|

| |

某些元件可能標示輸入低電位為0.8伏特,而其他元件可能需要0.3×Vdd的輸入低電位。假定一個最小3.3伏特的電源供應,則具有0.3×Vdd輸入低電位的那一側就是比較好的選擇,因為該側的輸入低電位為1.0伏特。 |

|

|

| |

例如,Si840x的輸入電位為0.545伏特。大部分的互補式金屬氧化物半導體(CMOS)元件電壓可拉低至0.4伏特的接地範圍內,因此這通常不是問題。 |

雖然隔離器一般具有0.9伏特的輸出低電位,但是仍可能將隔離器A側連接至具有標準電晶體-電晶體邏輯(Transistor-Transistor Logic, TTL)邏輯低電位0.8伏特的匯流排。

在此情況中,須使用建議最低值的匯流排提升強度。例如,Si8400/05輸入低電平將從0.9伏特最大值被降低為0.83最大值。很重要的一點是,須考量輸入電位負溫度係數,以確保具有適當的雜訊容限度。例如,當匯流排元件的規格是在 85℃的最大輸入低電位為0.8伏特時,則典型-0.6mV/C溫度係數則意謂在-40℃時,輸入電平將是0.875最小值,這會導致雜訊容限度為45毫伏特。

其他系統層級設計納入考量

其他兩項重要的系統層級設計考量為時脈伸展(Clock Stretching),以及如何納入一般須隔離的其他系統狀態和控制訊號。

很明顯地,數據線路(SDA)必須是雙向的,因為此線路包含註冊位址和數據,可從主端傳輸至從屬端,或是自從屬端到主端。而對從屬端裝置而言,在「承認(ACK)」期間,亦即在為主端元件進行資料檢索時,讓時脈線路(SCL)保持低電位狀態也是很平常的。

為讓「時脈伸展」在特定的I2C設計中運作,則必須使用一個I2C隔離器,它在SCL線路上也是雙向通道。

若未針對SCL訊號進行雙向隔離,則設計人員必須確定所有I2C從屬端元件能以相同於主端的的匯流排時脈速度和時序特性運作。這便對系統開發人員造成額外的設計和驗證負擔。Si8400針對SCL和SDA皆是雙向。

除了SCL和SDA訊號隔離外,許多設計還須要針對其他的系統狀態和控制訊號進行隔離,例如重設和中斷線路。使用具有額外單向通道的單一I2C隔離器能讓系統設計師得以簡化設計中的時序挑戰。

被迫以多重隔離器(Multiple Isolator)或光耦合封裝(Opto-coupler Package)隔離其他狀態和控制通道,如此將造成明顯的元件至元件的時序變數,若取代此一作法,具有額外雙向通道的的單晶片I2C隔離器則展現出在整個過程中皆能緊密追蹤電壓和溫度變數的時序特性。Si8405具有兩個額外的單向通道,適用於隔離重設和中斷訊號。

I2C設計並不複雜。只要考量每一種設計技術並選出符合需求的隔離器,設計師將能在他們的產品中輕鬆地運用I2C。

(本文作者任職於芯科實驗室)

| 參考資料 |

●NXP UM102104, I2C -bus specification and user manual, Rev. 03 — 19 June 2007

●SMBus.org, “System Management Bus (SMBus) Specification”, Version 2.0, August 3, 2000

●Silicon Laboratories, Inc., Si8400/05 data sheet |