毫無疑問地,資訊時代的特徵,是收集、處理和分發越來越大的資料模組需求呈現爆炸式的成長。在通訊網路領域中,這表示網路上連接的基礎設施和元件需要更多頻寬。

在醫療產業中,則反映在掃描儀器、X光機等設備產出的資訊更為詳細。相對地,針對頻寬的這種快速成長進行測試與分析,彰顯了對於速度更快、容量更大的電子測試設備之需要。

這種對資料的無止境需求,促使JEDEC發表了針對資料轉換器與邏輯元件之間高速串列鏈路的JESD204標準。該標準的修訂版B於2011年發布,此版本將串列鏈路數據速率提高到了12.5Gbps,以滿足現今世界使用轉換器應用更高頻寬的要求。這些應用中的很大一部分,均要求資料以兩次電源週期之間已知且一致的延遲遍歷整個系統。這一概念稱為「確定性延遲(Deterministic Latency, DL)」,JESD204B標準對此要求同樣有相關規定。此版本發表前,需要實現確定性延遲的系統設計師得藉由外部應用層電路來滿足要求。在JESD204B標準中導入了三個子類。子類0向後相容JESD204A標準,並且沒有關於執行確定性延遲的相關規定。子類1導入了一個外部參考訊號(稱為SYSREF),該參考訊號為採樣時序提供了一個系統級的基準。子類2定義SYNC~訊號如何用於採樣時序的系統級基準。採樣時序基準在各種情況下均可用來實現確定性延遲。本文旨在釐清JESD204B三個子類在操作上的區別,並為讀者提供實現其各自確定性延遲功能的相關實用知識。

確定性延遲概述

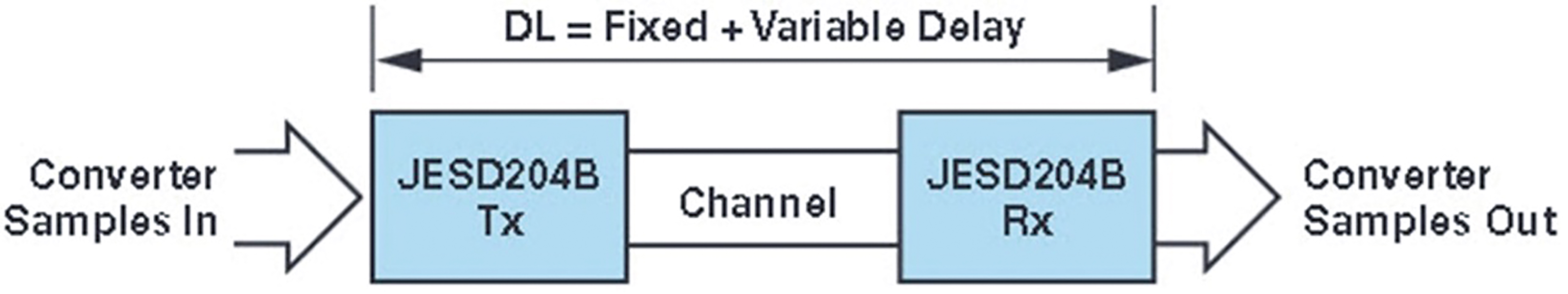

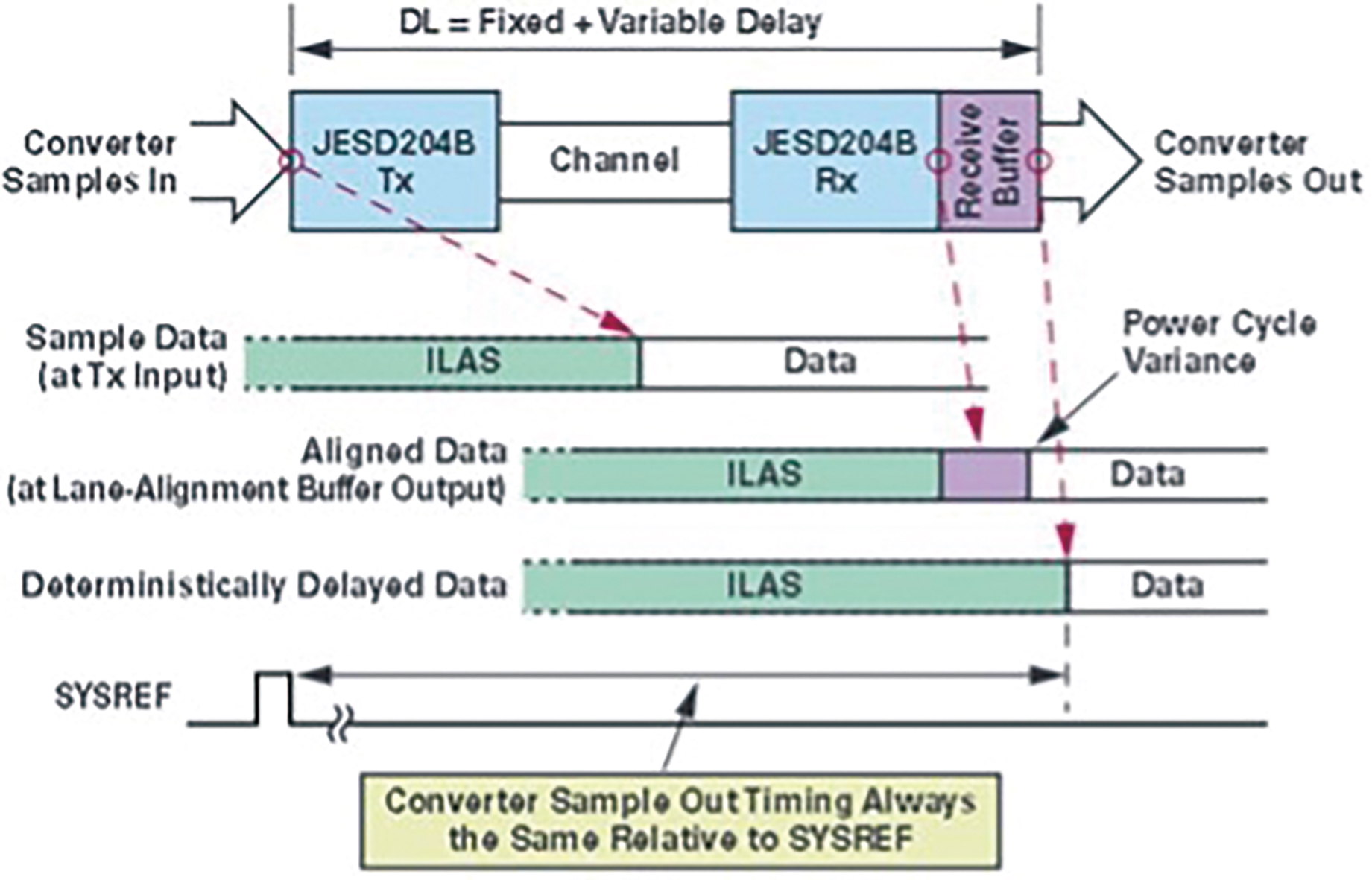

JESD204B標準將確定性延遲(DL)定義為基於幀的樣本到達串列發送器的時間與基於幀的樣本從串列接收器輸出的時間之差。延遲在幀時脈域中測量,且至少在低至幀時脈的週期內必須是增量可編程的。延遲必須在兩次上電週期之間,以及任意再同步事件之間可以重複。此定義見圖1。

圖1 確定性延遲圖示

圖1 確定性延遲圖示

JESD204系統中的確定性延遲由固定延遲和可變延遲組成。可變延遲是由數位處理模組中時脈域之間逐電源週期的任意相位關係所導致。在JESD204A和JESD204B子類0系統中未考慮到可變延遲。因此鏈路上的電源週期變化存在延遲。

子類0

子類0主要由JESD204B標準所提供,以保證向後相容JESD204A元件。如果系統設計人員有一個具有傳統JESD204A介面的自訂ASIC,並希望將其連接至帶有最新特性的JESD204B轉換器,那麼很可能需要這種向後相容性。

JESD204B標準提供子類0工作模式的要求和建議;這些要求可能與其他子類不同,最明顯為SYNC~訊號要求是子類1獨有。 SYNC~要求(同樣適用於子類2):

1.JESD204B接收器SYNC~輸出須與接收器幀時脈同步。另外也要求發送器幀時脈與SYNC~同步;這可以透過允許發送器SYNC~輸入重定幀時脈計數器來實現;必須指定SYNC~輸入到幀時脈邊界的延遲。

2.建議使用與元件時脈相同的邏輯(比如LVDS)。

3.一定不能交流耦合。

4.須指定接收器接腳端元件時脈到SYNC~的延遲(tDS_R);在幀時脈比元件時脈更快的系統中使用幀時脈啟動並捕捉SYNC~;無論如何依然需指定tDS_R。

5.必須指定發送器SYNC~到元件時脈的建立時間和保持時間。

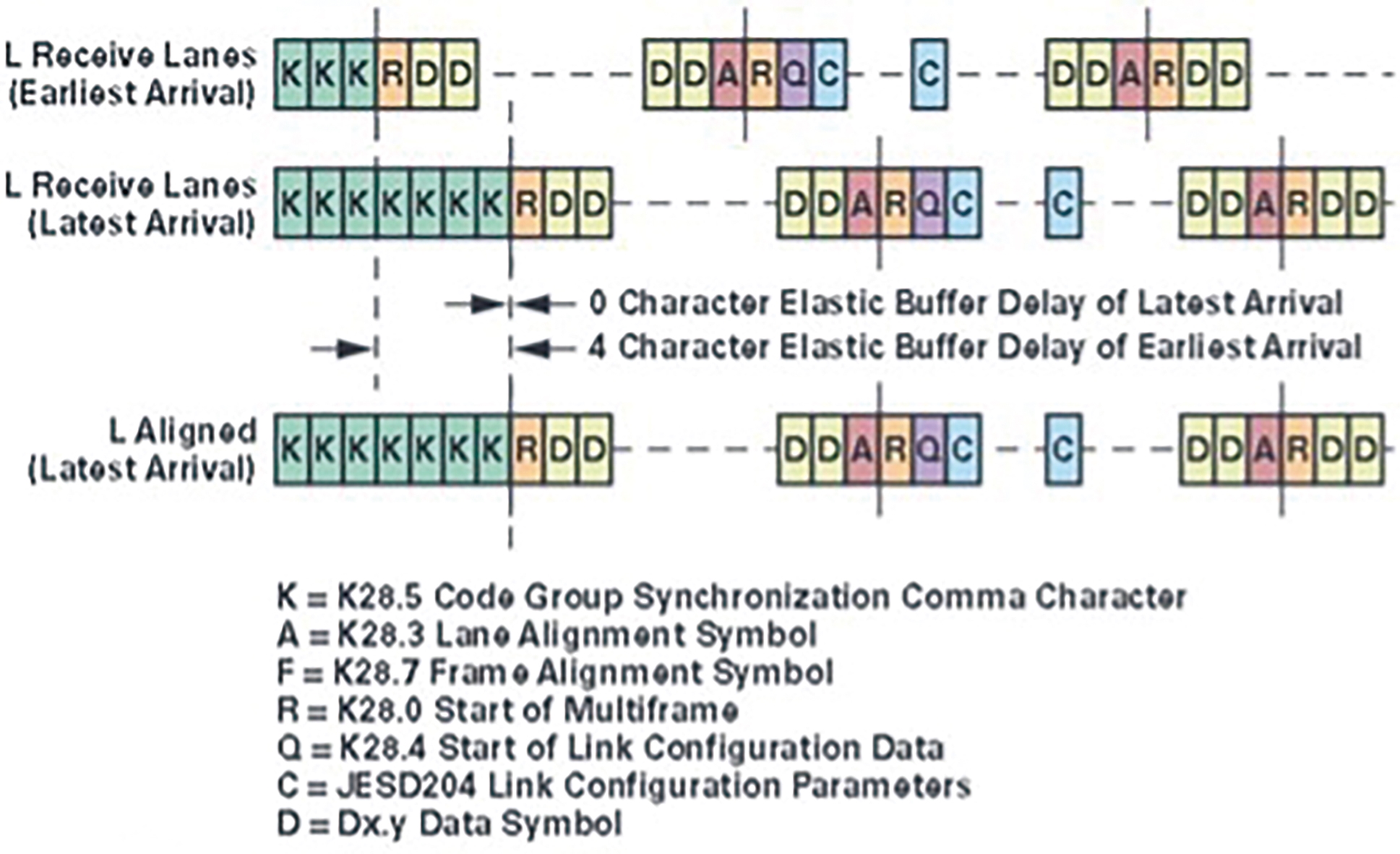

透過在每一條JESD204通道上使用一個彈性緩衝器,便可在JESD204接收器內自動處理JESD204單條鏈路上的通道對齊。初始通道對齊序列(ILAS)期間,對所有通道進行監控,並且在最終到達通道的「多幀啟動」對齊控制字元到達後,同時釋放所有緩衝器,如圖2所示。

圖2 單鏈路上的通道對齊

圖2 單鏈路上的通道對齊

雖然建議接收器和發送器的幀時脈均與SYNC~訊號同步,但沒有在整個系統中同步本地多幀時脈(LMFC)的機制。因此,使用確定性延遲無法實現多個轉換器的鏈路對齊。相反的,若單個元件內的多個轉換器配置為JESD204B單鏈路的一部分,則這些轉換器毋需借助外部電路即可對齊。LMFC對齊誤差只會對鏈路總延遲產生最多一個LMFC的可變延遲。

部署確定性延遲的一個優勢,就是它可以提供多晶片同步的途徑。然而,實現多晶片同步並不必然要部署確定性延遲。

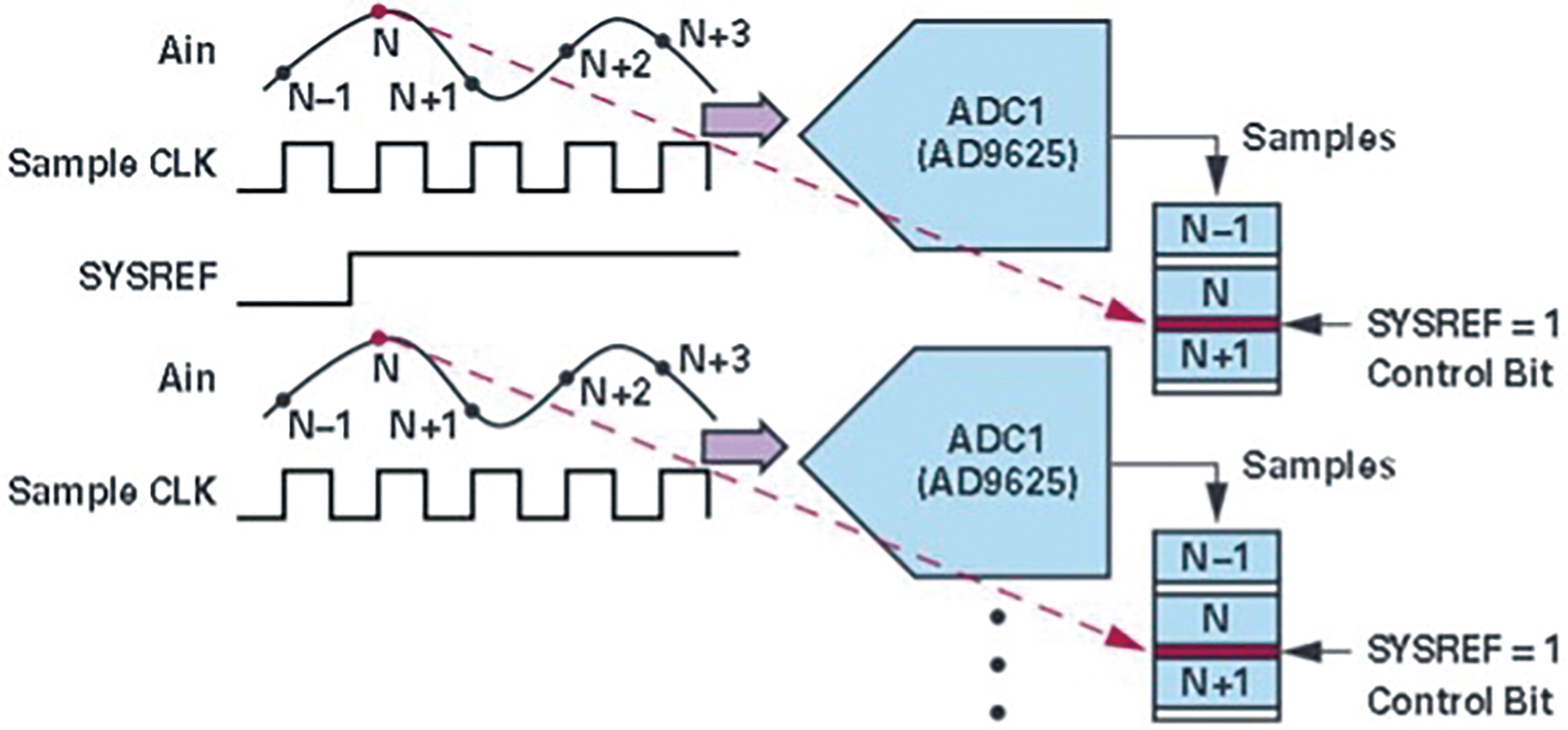

JESD204標準允許在採樣資料中加入「控制位元」,以便將樣本資訊從發送器傳輸到接收器。在ADC應用中,可將控制位元用於「時間戳記」,標記恰好與外部基準訊號一同出現的樣本。如果在子類0工作模式下使用子類1元件,那麼可以透過SYSREF輸入實現該操作。另外,也可在連接單個邏輯元件的多ADC應用中使用SYNC~訊號。多晶片同步的基本要求是為ADC提供外部基準訊號,並支援JESD204發送器中的控制位元。

有業者推出元件如AD9625和AD9680支援多晶片對齊的時間戳記功能。圖3說明如何使用SYSREF輸入來為恰好與外部基準訊號一同出現的樣本標記時間戳記。如圖所示,當元件時脈採樣SYSREF訊號時,將在該樣本中設置指定的控制位元。可針對JESD204B系統中的全部元件執行此操作。SYSREF輸入不用於確定性延遲。

圖3 在多個ADC中加入時間戳記控制位元

圖3 在多個ADC中加入時間戳記控制位元

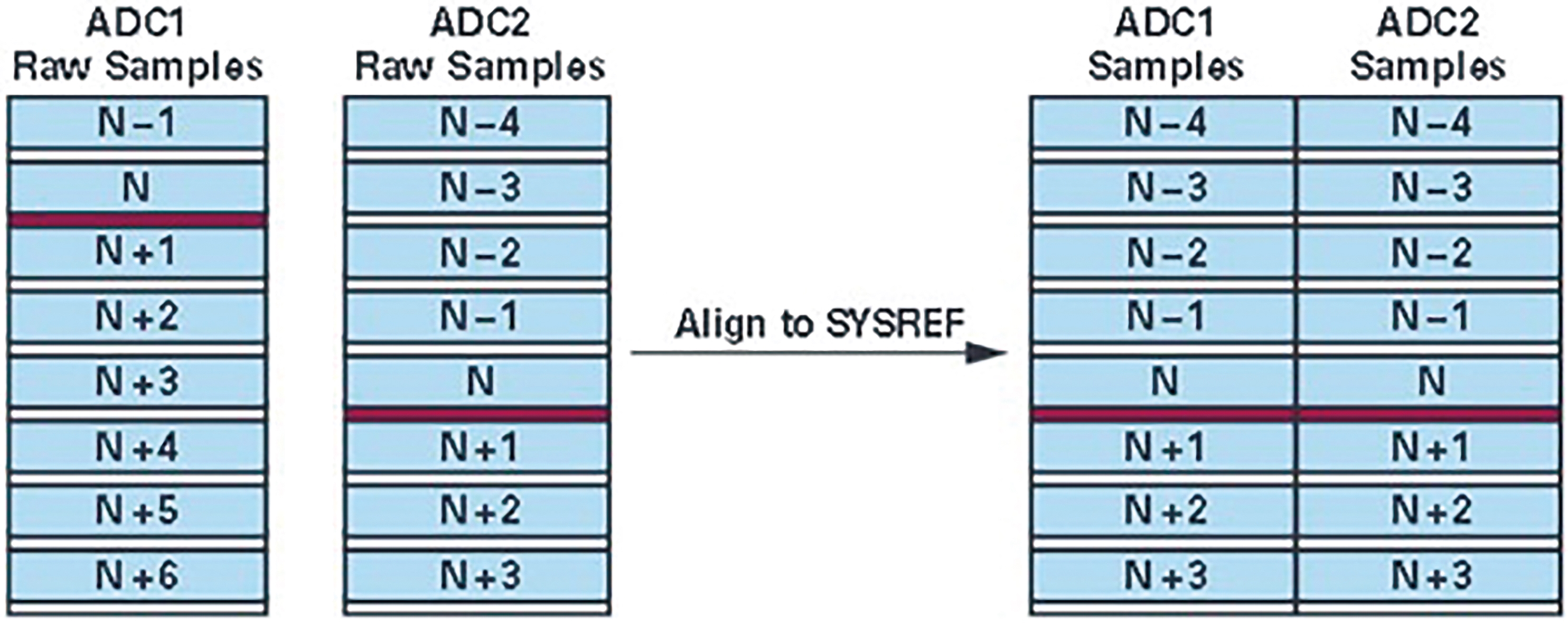

當為所有ADC元件的樣本打上時間戳記後,下游邏輯元件便可如圖4所示進行樣本對齊。

圖4 對齊打上時間戳記的樣本

圖4 對齊打上時間戳記的樣本

子類1

如上所述,鏈路上的通道對齊和多晶片對齊可在子類0工作模式下實現。但是,很多應用不僅依靠多元件的樣本同步,還要求轉換器和邏輯元件之間資料傳輸具有已知的確定性延遲。如某些ADC應用使用回饋迴路校準前端類比增益。通常可透過向接收器輸入測試訊號來實現。然後使用數位化資料來確定一切必要調整。關鍵是需瞭解類比輸入到邏輯元件的延遲決定是否調節。若每次電源週期之後,無論是否發生同步事件,資料的到達時間都必須一致,這類應用就需要部署確定性延遲。

在子類0系統中,樣本資料到達最終通道後便從JESD204B接收器釋放。然而,每次電源週期的釋放時間都可能不同。在子類1系統中,定義了「接收緩衝器」,它的釋放時間以外部SYSREF訊號為基準。因此,它不會受到 JESD204B系統中電源週期變化的影響(圖5)。

圖5 子類1系統中使用SYSREF的資料釋放時序

圖5 子類1系統中使用SYSREF的資料釋放時序

緩衝器與LMFC有關,它的釋放時間以SYSREF訊號為基準。SYSREF用來在系統中全部的JESD204B元件之間進行 LMFC相位對齊。緩衝器釋放時間以該SYSREF對齊的LMFC為基準。

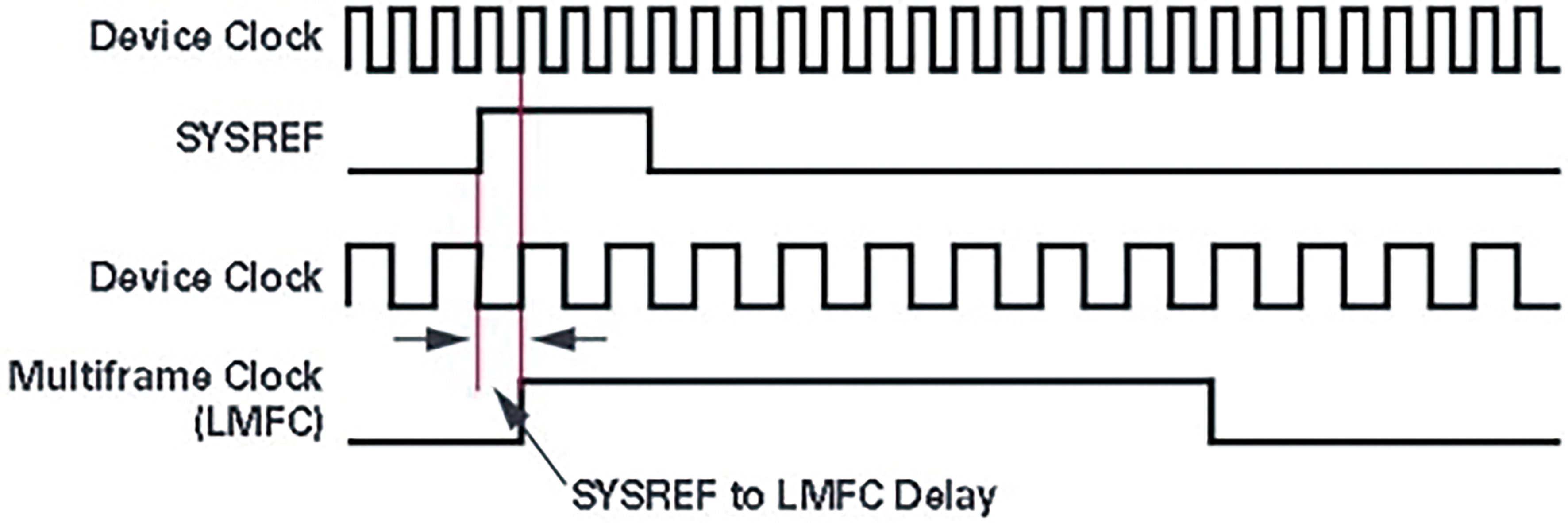

JESD204B系統中確定性延遲的精度和可靠性取決於元件時脈與SYSREF之間的關係。元件時脈是系統基準時脈,它提供採樣時脈(一般而言)、JESD204B時脈和串列器時脈。它用來捕捉SYSREF,並完成幀和多幀時脈的前沿相位對齊,如圖6所示。JESD204B標準提供了針對SYSREF和元件時脈的要求與建議。標準還提供了PCB布局布線與系統時序的指導。然而,這些要求如何部署在JESD204B系統中則取決於應用的系統級需求,比如確定性延遲不確定性(DLU)。部署特定應用的DLU以及其他詳情將於下篇文章介紹。

圖6 使用SYSREF進行幀時脈相位對齊

圖6 使用SYSREF進行幀時脈相位對齊

子類1操作的其他關鍵要求和建議如下:

1.在JESD204B系統中,必須指定所有元件的SYSREF前沿到幀和多幀邊界的延遲。在ADI轉換器產品中,這稱為 「SYSREF到LMFC延遲」。

2.接收緩衝器用來緩衝資料,並使用經過SYSREF對齊的LMFC作為確定性參考,以釋放資料。JESD204B標準定義了「接收緩衝器延遲(RBD)」。RBD決定緩衝器深度,額定值範圍為1至K幀週期(TF)。RBD用來補償系統中的可變延遲。 隨著多幀中幀數的增加,容許的可變延遲也隨之增加。ADI DAC元件支援16或32的K值。在大部分應用中,建議將其設為32。

3.由於確定性延遲的實際實現可能因製造商而異,甚至來自同一製造商的不同元件也可能存在差異,因此,當系統需要多晶片同步時,必須使用相同的轉換器。

4.同樣重要的是,元件間通道偏斜應最小化。例如對於ADI的DAC應用,元件間偏斜之和加上最大可變延遲,結果得到的值應小於本地多幀時脈(LMFC)。

5.元件時脈和SYSREF應從相同元件產生,以確保兩個訊號相位對齊。同時,SYSREF和元件時脈的元件間偏斜都應最小化。

6.在討論子類0工作模式和多晶片同步時,本文提出了SYNC~組合的概念,但對於子類1系統,這是不必要的。

SYSREF訊號可以是一個單脈衝、一個週期方波或者一個帶隙週期方波。SYSREF的週期必須為LMFC的整數倍。ADI元件支援全部三類SYSREF訊號。

SYSREF訊號的時序必須基於元件時脈進行精確控制,以使元件時脈採樣邊沿固定,並且為用戶所知。如前所述,SYSREF訊號必須與元件時脈保持源同步。因此,建議用提供整個系統元件時脈的同一元件來產生SYSREF訊號。例如ADI的AD9525就適合用來執行這種任務。

JESD204B標準中的時脈分布偏斜以及其他偏斜要求與其說是規則,不如說是指導。導入這些指導的目的是以例子說明去偏斜能力,作為解串器的推薦值。可在JESD204B標準第4.12部分找到這些描述。

子類2

子類2系統使用SYNC~訊號提供確定性延遲和多晶片同步,而非使用外部訊號提供時序基準。這種部署方案的主要優勢是,它能減少JESD204B系統的接腳和網路數量。如前所述,子類1 SYSREF背後的構想是利用它在系統中的所有元件之間實現內部幀和多幀時脈(LMFC)的同步。由於SYNC~根據接收器的LMFC產生,它搭載的LMFC時序資訊可用於實現相同的接收器與發送器之間的同步,就像使用了外部基準一般。SYNC~相較子類1 SYNC~需要額外的功能與精度。這些要求和系統同步時序要求降低了元件時脈所能達到的頻率。

使用SYNC~作為時序基準時,滿足時序要求的難度與使用SYSREF相當。系統時序精度受限於SYNC~的分布偏斜和 PCB上的元件時脈,以及它們的傳播延遲。精度解析度取決於元件時脈週期。與子類1一樣,系統的DLU要求決定了分布偏斜的限制。 在子類1系統中,元件時脈/SYSREF源是主機基準訊號,其同步請求來自邏輯元件。在子類2系統中,邏輯元件用於主機時序控制器,負責校正鏈路兩側的LMFC相位。其實現方式取決於系統是基於DAC的系統,還是基於ADC的系統。

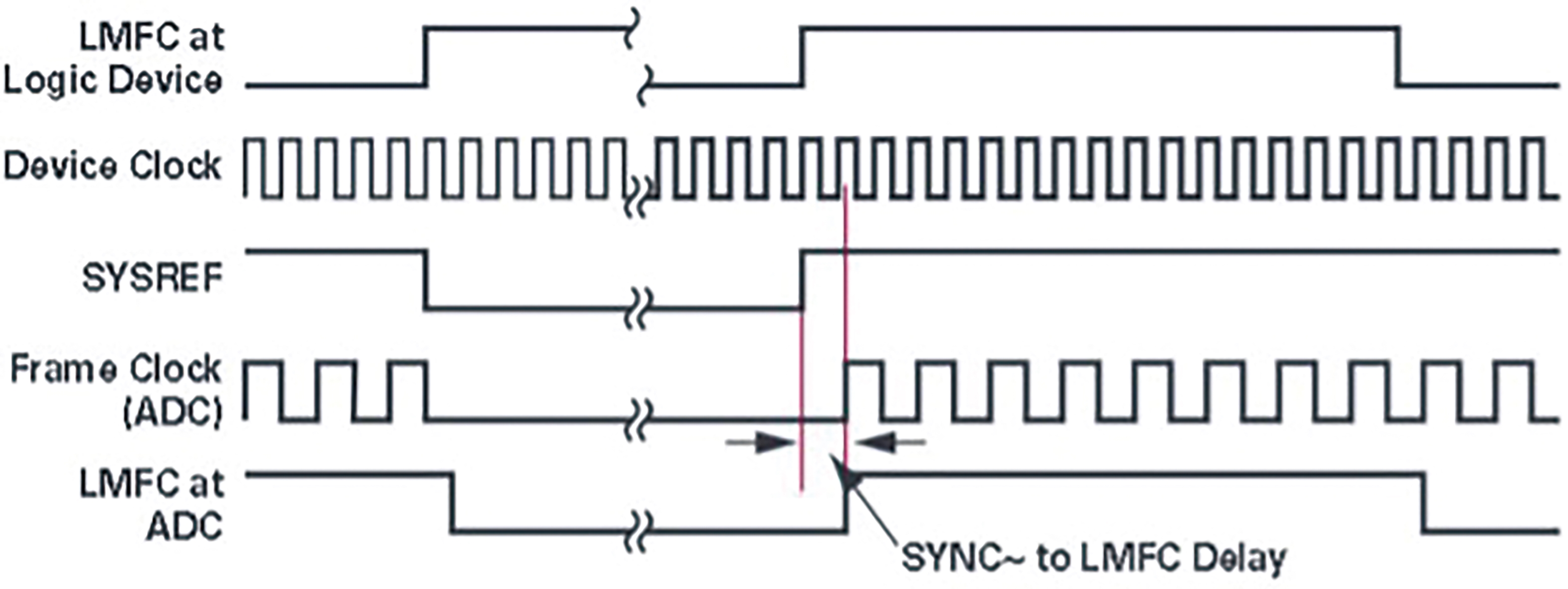

在子類2 ADC應用中,SYNC~解除置位元訊號由檢測時脈捕捉(通常是元件時脈),並用來重定其LMFC的相位。檢測並捕捉SYNC~訊號之後,除了重定其本地LMFC,JESD204B發送器還將開始發送K28.5字元,並會連續執行該操作,直到建立系統時脈。時脈建立後,同步過程的ILAS部分將在LMFC邊界處開始。在ADC系統中,ADC的LMFC對齊操作並不是一個反覆運算過程,且透過SYNC~單次置位完成,如圖7所示。另外還可使用週期性SYNC~監控發送器LMFC的相位對齊。更多詳情,請參考JESD204B標準第6.4部分。

圖7 使用SYNC~進行幀時脈相位對齊

圖7 使用SYNC~進行幀時脈相位對齊

在子類2操作中,邏輯元件的LMFC是主LMFC基準,轉換器LMFC必須與它相位對齊。在子類2 DAC應用中,邏輯元件還使用檢測時脈(通常是元件時脈)來捕捉一個或多個DAC的SYNC~訊號。邏輯元件將檢測自身LMFC與DAC LMFC之間的相位差,並在ILAS部分同步期間向DAC發出調節命令。ILAS長度為4個多幀,而鏈路參數(包括LMFC相位調節資訊)在第二個LMFC週期期間發送至接收器。在JESD204B系統中,邏輯元件向DAC發出的LMFC相位調節命令如下所示:

.相位調節(PHADJ):此命令指示是否需要調節相位。

.調節計數(ADJCNT):此命令指示所需的調節步驟數。

.調節方向(ADJDIR):此命令指示LMFC相位應提前還是延後。

根據調節時脈的解析度和它與LMFC週期的關係,調節DAC的LMFC可能花費超過一個ILAS週期。DAC上完成任意相位調節後,SYNC~置位低位準,以發出錯誤報告。邏輯元件上的發送器將使用此再置位再次檢測LMFC相位差。如果毋需進一步調節,則ILAS期間PHADJ位復位,接收器不發出錯誤報告。此時,LMFC處於對齊狀態,可開始傳輸使用者資料。如需執行另一次調節,則邏輯元件發送器將發起另一次反覆運算過程。更多詳情,請參考JESD204B標準第6.4部分。

當JESD204B系統中所有元件的LMFC都完成相位對齊後,便能透過子類1中的同樣辦法來實現確定性延遲。也就是說,接收緩衝器的釋放時間以相位對齊後的LMFC為基準,而不是以最後到達的通道資料的非確定性到達時間為基準,如圖5所示。它們的差異僅僅在於如何實現LMFC相位對齊。

JESD204B系統中確定性延遲的精度和可靠性取決於元件時脈與JESD204B系統中每一個SYNC~訊號之間的關係。與子類1相同,元件時脈是系統基準時脈,提供採樣時脈、JESD204B時脈和串列器時脈。它用來捕捉SYNC~訊號;後者在整個系統中為邏輯元件提供LMFC相位關係資訊。JESD204B標準提供的子類2要求與建議總結如下:

.針對ADC:

1.ADC必須調節其與檢測來自邏輯元件的SYNC~訊號有關的內部幀時脈和LMFC(可能還有採樣時脈)。

2.LFMC調節解析度應由元件製造商定義,並且會限制系統同步精度。

3.SYNC~檢測解析度應由元件製造商定義,並且會限制系統同步精度。

4.如圖7所示,必須指定SYNC~解除置位到ADC LMFC邊界的延遲。

.針對DAC:

1.DAC必須要能根據邏輯元件的指令調節其內部幀時脈和LMFC(參見上文「DAC子類2部署概述」部分)。

2.必須指定DAC LMFC調節解析度(DAC元件時脈週期中)。

3.無論何時,只要完成相位調節,DAC就必須發出錯誤報告。

針對DAC應用中的邏輯元件:

1.必須要能在檢測時脈(通常是元件時脈)遞增的情況下檢測SYNC相位與其自身LMFC的關係。

2.必須要能根據DAC調節解析度計算ADJCNT。

3.必須要能在ILAS期間發送校正資訊。

總結

資料轉換/通訊追求高處理能力為滿足目前與未來應用中更高的資料處理能力要求,JESD204B定義了數GB級介面,作為資料轉換器與邏輯元件之間實現通訊所需的通道。確定應用需要哪個子類是系統設計的重要步驟。對於不要求確定性延遲的系統,可以採用三種子類中的任意一種;其中,子類0的部署最為方便。而如果需要確定性延遲,則對於子類1或子類2設計而言,需考慮其他系統級因素。在下篇文章中,將更為詳細地探討這些問題,協助系統設計人員正確選擇JESD204B子類。

(本文作者為ADI應用工程師)