前一期介紹了幾種設計10Gbit/s高速串列差動式電氣通道訊號的方法,並且討論了微帶線(Microstripe)或帶狀線(Stripline)的特性。以下則將針對微帶線與帶狀線進行模擬,並分析其優缺點,也同時討論串列解串列(SerDes)晶片能帶來的協助。

微帶線走線長度影響抖動甚鉅

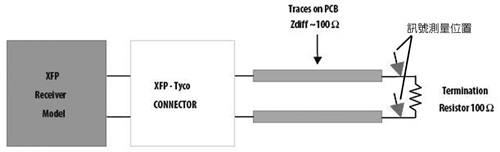

模擬一將檢視走線尺寸與介電質耗損對微帶線上10Gbit/s訊號傳遞所造成的影響,模擬時採用圖1的組態安排,電氣訊號由XFP光接收器提供,扮演電氣傳輸器的角色,並經過XFP連接器以及主控電路板上的電路互連結構到達提供100Ω差動終端的電阻,訊號的測量在圖1中箭頭所標示終端電阻的兩端進行。

|

| 圖1 XFI資料連結模擬的架構安排,其中右方箭頭標示了訊號測量的位置 |

這個模擬安排基本上有些理想化,忽略了實際SerDes或開眼晶片(Eyer Opener IC)封裝的頻率相關特性,以及雖然相對較小,但依然存在的晶片輸入緩衝電容影響。不過這樣做可以用較清楚的方式分析走線路徑參數對電氣資料通道XFI的影響,稍後則會以更真實的電氣接收器模型來取代終端電阻。

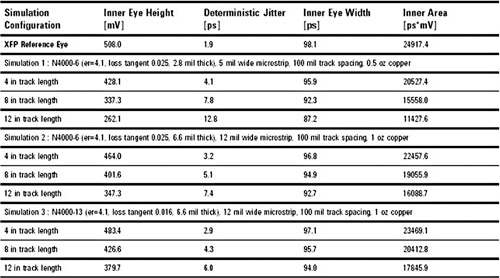

對於電路板階層的相連,則使用了差動阻抗為100Ω的寬鬆耦合微帶線,並在模擬二使用了4、8及12吋走線長度的三種不同走線寬度與介電質組合。組態的詳細資料以及眼圖分析的結果可以參考表1。請注意,兩個環氧樹脂層板都使用了相同的介電常數,以便使用完全相同的走線尺寸。因為介電常數會隨著頻率下降,同時兩個層板間也有些微差異,因此此處使用較標示值為高的範圍。

|

| 表1 微帶線互連的模擬參數與結果 |

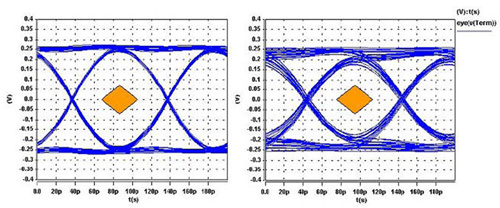

由圖2可以看到,隨著走線長度的增加,目標眼圖關閉以及更高的資料相關性,例如決定性抖動相當明顯。此圖將0與1的變化都分離成為多重走線,同時中間區域大幅縮小,圖2中的中央眼罩以符合XFI ASIC/SerDes接收器輸入遮罩為基礎,僅做為相對比較之用。值得注意的是,XFP多重訊號源協定中的最長走線長度建議值為12吋。

|

| 圖2 模擬二中4吋(左方)與12吋(右方)走線長度的眼圖比較 |

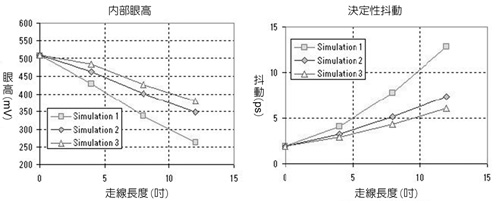

表1中所列出的結果以圖3描述,顯示了增加的決定性抖動以及下滑的開眼幅度為所選擇微帶線尺寸大小與介電物質的函數,非常明顯地,模擬一會產生最大的耗損,這可以解釋為相對較窄的表面阻抗,大約只有5密耳(mil)寬。將走線寬度加到12密耳可以大幅度降低表面效應所造成的耗損,此可由模擬二的資料看出。對於這兩個模擬,使用的耗損因數為0.025,較寬鬆並且較便宜的層板,要進一步提高眼圖的餘裕空間,則可使用更低耗損的層板如模擬三。不過,除非是超過6吋的超長互連長度,否則改善相當有限,對於短於6吋標準的走線長度,較高耗損的層板就足以符合XFI通道的要求。

|

| 圖3 微帶線互連XFI連線組態的部分眼圖參數 |

貫孔/PCB牽動帶狀線走線效能

帶狀線走線位於兩個參考平面之間,可以電源或接地面方式加以模擬,不同傳導層間通常以大約6密耳厚的介電層分隔,這代表了帶狀線寬必須相當窄,大約為5密耳,以便符合100Ω的差動阻抗設計目標。因此可以假設,表面效應耗損將扮演相當重要的角色。雖然帶狀線的整個表面可以傳導電流,和大部分電流會在相對參考平面的表面上流動的微帶線不同,用來降低表面效應的較寬走線會在高頻產生感應電阻,因此需要較厚的介電質層;不過由於整體厚度可能會超過實際限制,因此並不可行,較厚的電路板同時也需要較厚的貫孔,這會影響到繞線密度並造成重大的阻抗不連續性。

帶狀線的另一個缺點是必須透過貫孔將它們相連,採用貫孔設計會對訊號完整性以及整體XFI通道的效能造成大幅的影響,XFI MSA標準提供有貫孔設計、單端式與差動式貫孔區別,以及分析開路挖除長度對貫孔回返耗損影響等相關指南。

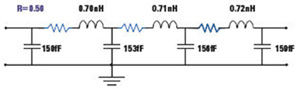

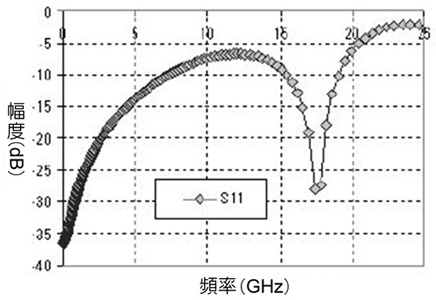

貫孔的高頻特性,由S11與S21參數描述,會依貫孔的尺寸參數,如鑽孔直徑、貫孔長度、電氣間隙大小以及堆疊方式與接地和電源面的確切位置有關。此外,也可以使用反鑽(Back Drilling)的方式來縮減貫孔的挖除長度,帶來更好的高頻效能表現,不過要對XFI資料通道上這些參數的影響進行全盤的探討基本上並不可能,也不在本篇文章的討論範圍。因此設計了可以產生XFP MSA 1.0版中類似響應的單端式貫孔等效電路,以便進行因貫孔所造成阻抗不連續性的適當模擬,所採用貫孔模型的等效電路可以參考圖4,模型中使用了些微變化的電容與電感值將生產時可能發生的變動性導入到模型中,圖5為貫孔回返耗損的結果,與XFP MSA 1.0版中的貫孔模擬類似,這個模型會在大約17GHz處產生主要的諧振尖峰。

|

| 圖4 貫孔的等效電路 |

|

| 圖5 貫孔等效電路的S11回返耗損 |

接著將貫孔模型插入到主控電路板帶狀線互連的任一端XFI資料通道上,這可以讓訊號由XFP連接器流經帶狀線並由帶狀線回到SMT終端電阻。

接著進行兩套模擬,其中一套使用標準的層板,另一套則使用耗損因數分別為0.025與0.016的較低耗損介電質,在兩套模擬中,帶狀線為5密耳寬同時被夾在12.2密耳距離分開的參考面之間,走線則以50密耳分隔進行微弱邊緣耦合。

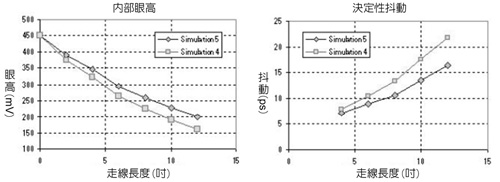

表2為模擬參數與結果的整理,並將兩個參數圖透過圖6描述。和預期一樣,由於相對較窄的線寬,表面效應所造成的耗損對開眼的大小帶來大幅的影響,主要來自於大幅縮小的內部眼高。事實上,對標準的FR-4,XFP MSA只建議最長6吋的帶狀線長度,不過使用較低耗損的介電質可以帶來開眼大小的明顯改善,主要原因是,在帶狀線組態中電場會被完全包含在介電質內,因此帶狀線的介電質耗損會比微帶線相對較大,所以較低耗損的介電物質可以用在超出標準建議6吋的帶狀線長度上。

表2 帶狀線互連的模擬參數與結果

由於出現兩個貫孔,因此可以注意到,內部開眼,也就是圖6中的眼高會降低,甚至在走線長度為零時。在此特殊情況下,考慮兩個貫孔帶來開眼幅度下滑大約10%,適當的貫孔設計或者使用差動式貫孔可以將這個耗損降到最低。

|

| 圖6 帶狀線互連XFI連接組態的部分眼圖參數 |

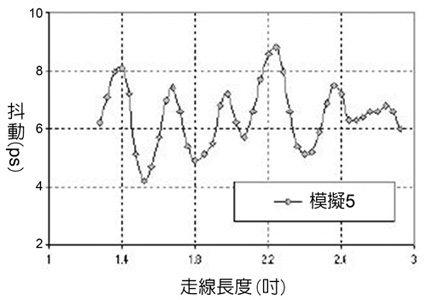

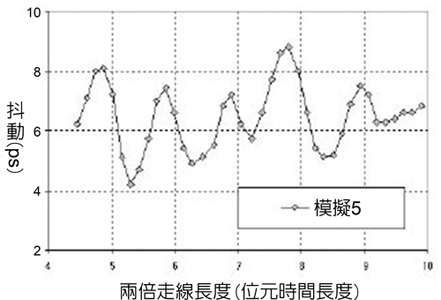

另一個使用貫孔的影響是提高了資料相關抖動(Data Dependent Jitter, DDJ)的幅度,對於走線長度較短,因此決定性抖動會隨走線長度振盪,如圖7中的較低耗損介電質,這個振盪行為主要來自於帶狀線兩端兩個貫孔形成阻抗不連續造成反射所帶來的振盪效應,就算是使用偽亂數位元序列,這個效應還是非常大。

為了進一步研究這個現象,先取得模擬組態5的帶狀線傳遞延遲(174.17ps/in),這可以將圖7以訊號來回時間,也就是兩倍走線長度的函數繪製圖7。以位元時間為單位(100ps),得到的結果可以參考圖8。由圖8中可以明顯看出,最大值與最小值都會隨著位元時間長度週期性出現,符合抖動幅度振盪為諧振效應的原始解釋。

|

| 圖7 資料相關抖動為帶狀線走線長度的函數 |

|

| 圖8 資料相關抖動以訊號來回時間的函數方式繪制,單位為位元時間長度 |

這個效應會對造成較短互連長度系統效能的變動,不同時間所生產環氧樹脂層板的介電常數會有些微的變動,造成帶狀線傳遞延遲的變化,而這也會造成相同標準長度互連路徑訊號來回時間的差異,對系統效能的整體影響造成接收器必須能夠容忍整體抖動的變化。以系統效能穩定的目標來說,最好是使用較低階的層板,以便帶來足以將反射衰減的較大介電質耗損。

SerDes左右訊號品質

到目前為止,接收電路都是以理想的100Ω終端電阻來代表,但是在實際應用的XFI通道中,這個部分絕大多數會以終端電阻在矽晶片上實現,隸屬差動輸入緩衝器一部分的開眼或者是SerDes串列解串列晶片取代。由於對XFI通道而言,並不需要額外的表面黏著元件,因此將可以大幅簡化系統的設計。不過,這也代表了晶片封裝的頻率相關特性位於主控電路板傳輸線尾端與終端電路之間,因此會對接收訊號的品質造成影響。

為了評估這個效應,因而建立了晶片封裝的模型,XFI通道元件的理想封裝應該是一個只會造成訊號延遲而不會發生反射的50Ω阻抗(z0, zdiff=10Ω)傳輸線,較新的球閘陣列(BGA)晶片封裝雖然相當接近這個傳輸線限制,不過這個晶片封裝的內部結構,例如封裝貫孔與打線,卻會造成阻抗的不連續性。

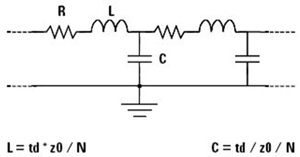

為了模擬的進行,在此使用了延遲時間為90ps的50Ω傳輸線,這相當於大約10毫米的晶片封裝互連長度,依封裝材料的折射率而定。但在此不用傳輸線的方式來描述互連,而是將封裝互連分割成數個獨立的全等RLC電路,在電路圖中這可以視為一系列電阻與電感透過電容接地的階梯狀電路,其中每個RLC元素都是如圖9中所顯示的一個階梯步階,階梯電路的步階數越多,對傳輸線的模擬就更精確;相對的,如果步階數較少,那麼將帶來較大的耗損,並且會在晶片封裝互連模型的S11與S21參數產生諧振。

|

| 圖9 RLC階梯電路包裝模型的構成元素。 |

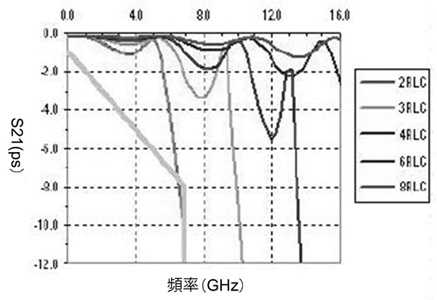

這個封裝模型的諧振以及截止頻率會隨著RLC電路元素數目的減少而移向更低的頻率(圖10),對於所選用的90ps延遲以及50Ω的漸近線阻抗,整體的電感值為4.50nH,而整體電容值為1.80pF,這些數值將平均分散在階梯電路的每個步階上。

|

| 圖10 SerDes串列解串列/開眼晶片封裝模型的傳輸線特性(S21),封裝被分割為多個完全相等的RLC電路元素。 |

圖10最左邊中的粗灰線為XFP MSA所規定XFI連線的最高可允許通道耗損,只由兩個RLC電路元素組成的封裝模型明顯地並不符合XFI連線的效能要求。 此外,本文也進行了微帶線傳輸線連線模型上實際封裝模型對XFI連線的影響,選用模擬組態二並搭配8吋的微帶線長度。

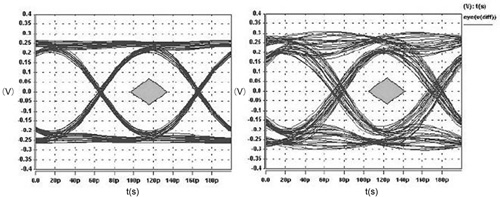

訊號由晶片的接腳測量,模擬結果產生的兩個眼圖可以參考圖11,其中左方的眼圖做為參考,顯示沒有加上晶片封裝模型時於微帶線尾端取得的訊號,右方則是加入內含三個RLC電路元素晶片封裝模型後的相同訊號。在此可以看出,抖動的幅度增加同時最大內部開眼縮小。

|

| 圖11 左方沒有加入晶片封裝模型以及右方搭配上由三個RLC電路元素組成晶片封裝模型的模擬結果,訊號由XFI通道參考模型的point 5(XFP MSA圖1的pointD)測量。 |

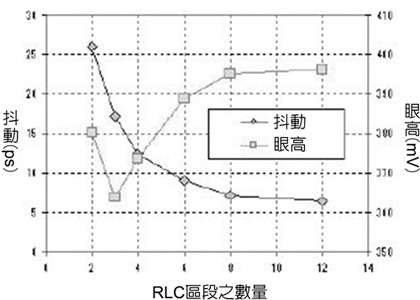

抖動以及內部眼高是由將選用封裝模型的整體電感與電容值分別分割為二、三、四、六、八以及十二個相同RLC電路元素進行模擬的品質因數,所得到的結果以圖12中的圖形表示。

|

| 圖12 抖動與內部眼高為晶片封裝特性的函數 |

要解釋圖12則必須記住,封裝模型中較少的RLC電路元素數量代表了截止頻率較低的較差封裝,而較多的電路元素則代表這個封裝模型相對接近50Ω的傳輸線,因此由圖12可以看出,較低頻寬,也就是較少RLC電路元素的封裝會帶來較高的抖動以及較小的開眼。因此,要對整體XFI通道容量空間進行評估,非常重要的是必須對開眼或SerDes串列解串列晶片的封裝頻率特性特別注意。

相同的觀念當然也可以應用在其他做法上:例如SerDes串列解串列晶片做為電氣訊號的傳輸器而XFP收發模組做為接收器時,為了要讓抖動保持在最小,XFP收發器的頻寬必須以相同方式進行最佳化以便將可能的寄生效應降到最低。

圖12中一個違反直覺的觀察是,當RLC電路元素數目下降到二時,開眼會再次變大;不過必須記住,這樣的封裝模型並不符合XFP MSA的耗損規格要求。事實上,內部眼高之所以增加是因為10Gbit/s資料串流因封裝寄生而造成高頻部分的反射,因此,由矽晶片的角度來看,晶片封裝扮演了低通濾波器的角色,而所反射的訊號高頻部分會在晶片座上消失,降低了最相關的輸入緩衝器邊緣速率以及內部的開眼大小。

為XFI通道設計挑選適合走線方式

本篇文章的模擬範例與結果顯示XFI通道的設計如何影響連線的訊號完整性,並特別對XFP模組中量化器/開眼電路及主控電路板上開眼/SerDes串列解串列晶片間互連結構訊號品質的影響進行探討。

自此可以看出,設計的決定來自幾種取捨:首先,對於收發器與SerDes串列解串列晶片相互間相當靠近的XFI通道,由電路路徑所發出的電磁干擾(EMI)對整體系統的EMI影響相當小,因此可以使用標準相對較高耗損的FR-4微帶線走線,但必須特別注意因阻抗不連續性反射所造成的諧振效應,而標準FR-4相對較窄線寬的表面效應電阻以及介電質耗損應該要對這些反射提供足夠的衰減以增加抵抗能力。

其次,對於須要讓XFP收發器與SerDes串列解串列或開眼晶片分隔較遠的XFI通道設計,帶狀線互連是能夠提供目標抗EMI能力的最可行組態,不過為了良好的訊號完整性,必須使用低耗損的FR-4,同時也建議在貫孔上採用高速設計的法則,例如更大的電氣間隙以及後鑽式作法來縮小貫孔挖除長度。另外,如果XFI通道設計介於這些限制之間,則建議透過模擬來取得最佳的組態。

要達成XFI資料通道的成功設計需要對每個組成連線的元素進行仔細的分析,XFI連線設計的完成建立在每個元素都能夠符合XFP MSA中所列出的頻率相關耗損規格上,此外,所有的耗損也必須小於整體的連線限制,不同連線元素間的相互動作還是可能造成XFI通道發生無法預期的行為而無法通過相容性測試,因此必須藉由訊號完整性的模擬來加以驗證,不過只要遵守這樣的方法,系統設計將可以很快朝向符合要求的解決方案邁進。

(本文作者任職於安華高科技光纖產品事業部)

| 參考資料 |

[Hall 2000] Stephen H. Hall, Garrett W. Hall, James A. Call合著:“高速數位系統設計(High Speed Digital System Design)”,John Wiley & Sons, Inc., ISBN 0-471-36090-2.

[Johnson 2002] Howard Johnson:“表面效應與介電質耗損混合討論

(Mixtures of skin-effect and dielectric loss)”, EDM Magazine, September 19, 2002.

[Ritchey 1999] Lee W. Ritchey:“印刷電路板材料介紹

(A tutorial on PCB Materials)”, www.speedingedge.com |