自2015年蘋果(Apple)開啟智慧穿戴裝置世代以來,理想的智慧穿戴結合人工智慧(AI)、物聯網(IoT)、邊緣/雲端運算、聯網能力(如Wi-Fi、Bluetooth與5G通訊),於穿戴裝置建構智慧終端,因體積小且延續傳統手表的使用習慣,已成為多數人使用手機產品的功能延伸,進一步改變生活習慣,成為貼身數位助理。

穿戴產品發展演進趨勢及挑戰

例如讀取訊息,行動支付等,便利性讓穿戴裝置容易被大眾接受,加上智慧化後增加的體徵判斷功能,讓穿戴裝置有了運動及健康的取向吸引用戶黏著度,根據市場調研機構Counterpoint發布的全球智慧手表出貨量報告顯示,2020年上半年全球智慧手表出貨量已接近4,200萬,相比2019年同期實現了20%的成長。市場研究分析機構Yole預測,至2025年整體穿戴裝置市場可達979億美金,年複合成長率達11.2%。

隨著眾多品牌智慧穿戴裝置推陳出新,結合多樣感應器已是基本功能:長續航時間,走路、跑步或睡眠記錄,已是基本的必備功能。此外,為了滿足特定使用族群配戴產品的需求,提供一些新功能如孩童安全、寵物追蹤、長者跌倒監測等特定用途的穿戴裝置。

常見的健身項目如仰臥起坐、深蹲、開合跳等健身動作自動計數功能,讓使用者可以更輕鬆進行健身活動,同時監控偵測心跳、血氧、睡眠、壓力等生理狀況數據。隨著健身鍛鍊的生活風潮盛行,運動/健身取向的裝置也越來越受歡迎;另外因2020年疫情所致,消費者不方便上健身房且檢測身體狀況需求明顯增加,以致智慧穿戴裝置銷售成長超過預期。

新推出的穿戴產品中,已見採用人工智慧來分析數據,運動/健身取向的設計中就會內建多種進階運動模式偵測大幅度運動,如:網球、籃球與足球等,綜合分析運動姿勢、速度、力量強度的人工智慧演算法,成為智慧教練幫助使用者記錄運動的軌跡;增加防水設計就可以追蹤使用者的游泳姿勢、距離、速度、心跳,導入體徵演算法來判斷身體狀況,給予運動訓練的建議,或是健康診斷的警示。有些高價多功能的產品中甚至加入氣壓計、衛星定位系統(GPS、GLONASS、Galileo與北斗)、羅盤、深度感測器,讓活動領域擴展到空中、水底,滿足更多探索極限冒險的使用者進階需求。在可預見的未來,穿戴式裝置會融入越來越多的感測器,並專注於演算法的優化,以強化應用切身的輔助,實踐人工智慧並改善人類生活。

三項低功耗SoC運用於穿戴產品晶片設計重點

從晶片設計的角度來看,在穿戴裝置在設計上有三種挑戰:體積、省電、智慧。

有限體積對穿戴裝置的設計挑戰

穿戴裝置對於小體積要求極高,畢竟電池、顯示模組已占用了大部分的體積,因此主晶片以及內嵌的多種感測器,在乎面積極小化的程度比起其他電子產品更來得高。根據功能、所需的電晶體元件數量,一般的穿戴裝置會選擇55nm以下製程,產業中推出高階多功能的產品可能選擇到40nm/28nm甚至FinFET製程。有幾項原因推升製程進步,一個裝置內會使用多種感測器,如測量物體三軸姿態角或角速率以及加速度的裝置(IMU)、心率監測儀(HRM)、大氣壓力感測器(BARO Sensor)等。而感測器在開機狀態下持續收集數據,AI/ML加入後,模式已經從傳送到主控端(如手機)運算,進階到在裝置內運算,一方面降低聯網必要性及頻寬需求,提升裝置的即時反應;另一方面,終端資料量及運算量的增加也讓裝置內記憶體的需求容量更高,進一步傾向使用先進製程。再者,穿戴裝置的輕薄短小特性也會限制PCBA設計,若使用高度整合SoC晶片可以減去外部元件的數量,在電路設計與元件的簡化、厚度及防水、防摔、可靠度等這些考量上都可以更有設計彈性。

如何最大化使用有限電量是關鍵

如上所述,穿戴裝置使用電池供應並提供常時使用,功耗的設計是非常重要的,要滿足使用者對其期待隨侍在側的產品性質,又要避免太頻繁地充電,設計上必須盡可能延長待機時間,以至於穿戴裝置對於耗電需求格外高標,除了感測器及螢幕外,高效處理晶片是其關鍵核心,為了降低整體功耗,可選用超低功耗(ULP)製程,運作於低操作電壓下保持工作頻率,並從元件設計階段就將省電機制考慮進去,才能根本地提升整體效能效率,如晶片設計商智原科技便以Fundamental Library設計能力,在聯電的製程工藝55/40/28/22nm上打造PowerSlash IP,能在0.81V至1.32V廣域電壓下運作;而其加速模式(Turbo Mode)可在額定頻率下減少MCU核心約40%的動態功耗。

客製化記憶體最高可壓低耗電至百分之一

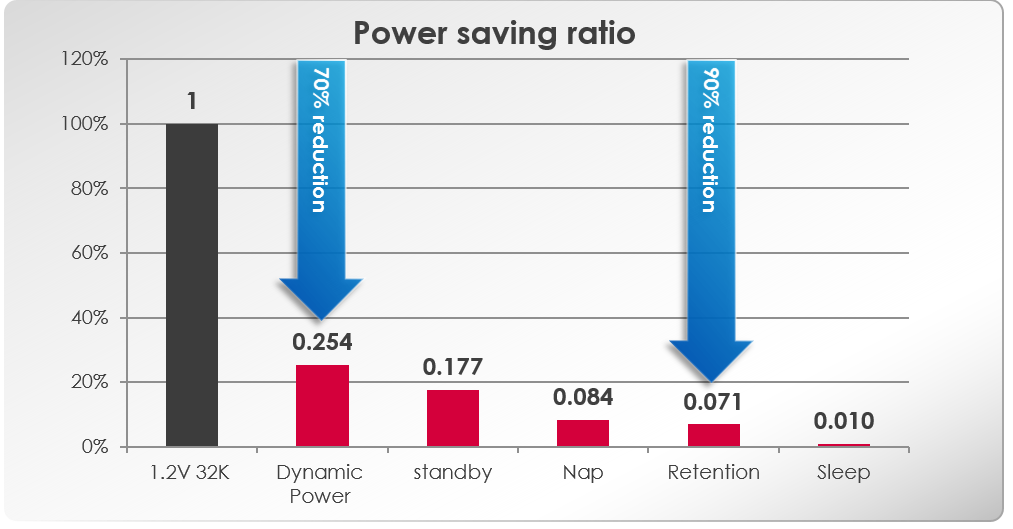

此外,內建的記憶體容量需求越高所耗的電也越多,因此衍生出更多客製化設計SRAM單元的需求(圖1),業者若具備客製低電壓SRAM Bitcell的設計能力,可依照晶片功能需求的範圍內,大幅降低臨界電壓(Threshold Voltage);這種設計可以大幅降低整體耗電,優化記憶體在SoC中耗電的比例,讓SRAM在保持在工作電壓,搭配不同操作模式,記憶體漏電流可以顯著地降低,跟正常模式相比,可只消耗約百分之一的耗電量,不用再因為需求SRAM的容量而犧牲了晶片功耗。

圖1 客製化SRAM記憶體設計在不同模式下的耗電表現

圖1 客製化SRAM記憶體設計在不同模式下的耗電表現

另外,裝置中現在配備眾多的感測器,為了有效率地使用這些感測器,統計穿戴裝置使用週期內,感測器會消耗掉大部分的電力。因此,發展出專屬的感測中樞(Sensor Hub)集中控制所有感測器,對此在設計中透過客製化的指令集(Instruction Set),可以調控Always-on的效能分配,包括感測器的校正及資料融合,讓感測器的處理程序單獨在Sensor Hub上運行,主SoC效能可以集中處理傳輸、內容判讀或將資料進一步加工使用,例如人工智慧的部分。

動態切換操作頻率使晶片耗電更精省

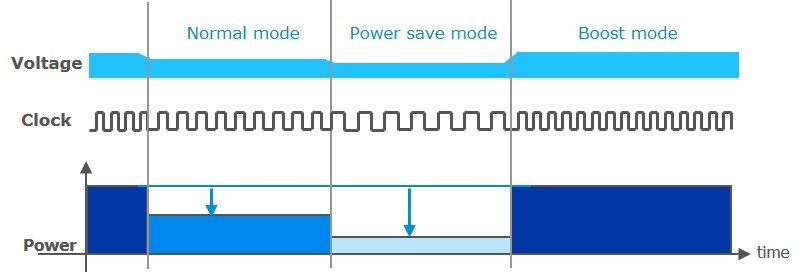

SoC中的核心CPU,掌管所有感測器收集到的數據運算。為了讓CPU的效率更好,根據裝置的使用情境,裝置必須隨時處於Always-on,以較低功耗達成全天候健康監測功能;為了讓整體功耗獲得較佳控制,晶片設計上可採取DVFS動態電壓頻率管理模式(圖2),此動態電壓頻率管理功能,依照裝置執行任務模式調整操作頻率。穿戴裝置的使用情境大部分時間是在待機狀況下,動態切換操作頻率使CPU在長待機時間時以較低速運行,而被喚醒後快速切換至全速工作頻率下執行運算,或者搭配加速模式可進一步加強核心在相同的操作電壓下達到兩倍的效能,系統整體效能和功耗都被考慮到,讓用戶在體驗上察覺不到切換的頓點,也達成裝置長時間續航力的目標。

圖2 DVFS動態電壓頻率管理模式示意圖

圖2 DVFS動態電壓頻率管理模式示意圖

筆者在協助客戶做系統架構評估到SoC系統整合的經驗中,看到低功耗設計的需求性,在晶片設計與驗證中,即可滿足客戶在低功耗產品為目標。因此,業者如智原發展出一套完整的低功率設計流程,從元件庫設計到DFT到P&R,在每個設計環節都將低功耗納入考量,並且此流程符合IEEE 1801-2009 UPF 2.0及IEEE P1801 CPF等業界低功耗規範,提供客戶完整優化的運算功率及性能。 完善架構評估及開發平台周全智慧晶片設計

產品快速迭代的週期下,應用上推陳出新,千篇一律的功能已經不能打動消費者。各家廠商針對監控與改善個人健康功能逐漸提升,伴隨現今社會對健康重視的風氣促使廠商著重在塑造健康生態圈,可以編輯專屬客製化的運動菜單,利用裝置收集到的多種體徵數據,量化生理狀況,訓練人工智慧對於健康體徵的訊號判斷,一旦出現異狀可以及時提醒使用者留意自己的身體變化,例如心律不整警告,因主晶片加入AI/ML的運算引擎,所以智慧判斷可完全在裝置上運作,毋須上傳資料到終端或雲端,同時滿足預防醫學的功能及保護使用者隱私洩漏的問題。隨著智慧演算法的進化,未來可期延伸到更細化的護理或預防性功能,無創血糖檢測,血壓、肌肉運動、食物攝取量記錄等。更細化的數據,可以讓智慧穿戴裝置進階智慧化,獲得更多症狀追蹤的能力。

由於注意到客戶在系統應用上智慧程度升級的趨勢,在協助客戶將AI演算法落實到晶片的過程中,特別是整合AI/ML功能的SoC,在制定架構上需要仔細地評估系統架構,在初期階段先對晶片效能的設定,建立一個虛擬探索平台,先行在SoC整體包含神經網路的工作量、處理速度、效率上,分析評估所需的匯流排及記憶體流量,這種設計方式讓架構調整、選擇、及優化的過程有明確的數據參考,可提前找出資料流量及功耗及效能在設計上的平衡點,以確保整體晶片表現符合預期目標。

此外,為協助開發商提前驗證智慧演算法到應用程式的完整度、可靠度,幫助縮短產品上市時間,諸如55uLP/40uLP等IoT開發平台(Uranus&Ariel),將智慧穿戴/物聯網裝置常使用的傳輸介面及電源模式、通訊模組、記憶體、安全加解密機制,整合在開發平台上供客戶做裝置前期驗證,如此一來讓軟硬體開發可以同時進行,縮短迭代及驗證的時間,甚至提前做多裝置聯網系統評估,協助產品開發團隊有效掌握開發時程。

穿戴裝置從剛問世時被視為過渡產品,功能上曾出現諸多抱怨,時至今日各家消費電子品牌大廠爭相推出專屬穿戴裝置,2020年已經推升到銷售歷史新高,可期待未來的高普及率之下,智慧穿戴可成為僅次於手機的物聯網隨身入口,結合智慧化、輕便、長時間待機、快速反應這些發展重點,讓穿戴裝置越來越智慧,使用方式越來越直覺。譬如智原便於設計服務上提供55/40/28/22nm多種製程平台選擇、低功耗設計流程加上CPU及SRAM優化的設計服務,滿足穿戴裝置小體積及省電的挑戰;而物聯網/智慧穿戴裝置專屬平台的推出,可推進智慧軟體系統開發與晶片設計與驗證週期,即可縮短產品上市時程,與客戶一起成就產品,提供較佳的用戶體驗。

(本文作者為智原科技市場行銷企劃經理)