藉由控制器區域網路彈性資料率(CAN FD)通訊協定,CAN技術在多分支(Multi-drop)網路中的資料率可提升至2Mbit/s,而在點對點的通訊系統中則可達到5Mbit/s。CAN FD是完善的CAN通訊協定改良版,也可說是強化版,主要可提高CAN網路中的平均位元率。

目前在汽車應用中的CAN,125kbit/s、250kbit/s和500kbit/s位元率均已通過驗證。

未來透過CAN FD通訊協定,CAN資料傳輸率可從資料階段加以提高。目前汽車業分成兩部分討論,一是2Mbit/s的多分支網路,另外則是最高到5Mbit/s和8Mbit/s的多點通訊。

迴路延遲局限CAN FD位元率提升

要廣義涵蓋CAN FD通訊協定,並不須要對現有CAN收發器加以任何改良,但由於在資料階段就要提高位元率,因此實體層(PHY)需要新的參數;而在開發所謂CAN高速接收器時,開發人員有必要參考ISO11898-2/-5/-6標準,這些標準指定許多靜態參數,像是隱性和顯性的電壓位準。

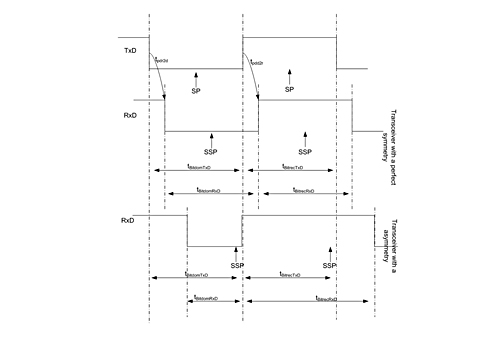

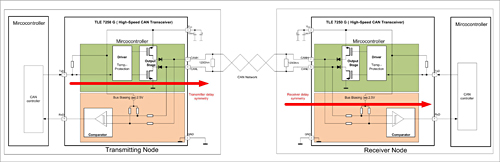

事實上,位元率越高,動態參數就越顯重要,實體層唯一的動態參數為TxD-to-RxD傳播延遲(迴路延遲)(圖1),參數最大值在現行ISO 11898-2標準下為280奈秒(ns);在ISO 11898-5標準下為255奈秒;而ISO 11898-6則是以ISO 11898-5為基準,傳播延遲規格相同。

|

| 圖1 TxD-to-RxD收發器傳播延遲規格 |

傳播延遲係針對有定義負載的收發器指定,但在實際應用中還必須考慮其他延遲,像是微控制器(MCU)和收發器之間的延遲;靜電放電(ESD)和電磁相容性(EMC)耐用性強化元件的延遲;尤其是從顯性末端到隱性邊緣的振鈴。

TxD-to-RxD迴路延遲適用於隱性到顯性的轉移,也適用於顯性到隱性的轉移,參數係針對60歐姆(Ω)和100pF的總線負載指定。此種規格的缺點是,允許極度非對稱的轉移傳播延遲,如此將縮短或延長隱性或顯性位元的位元長度,限制CAN FD電報資料階段可能的位元率上限。

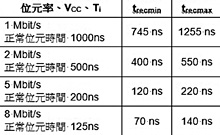

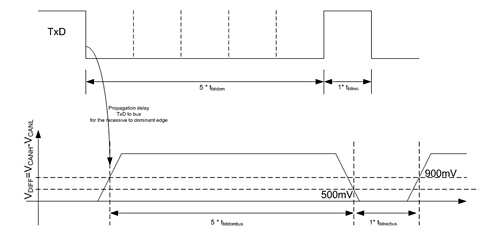

圖2顯示極度對稱和非對稱TxD-to-RxD傳播延遲效能的差異。假如收發器具有極度對稱行為,顯性位元的RxD位元時間將與TxD位元的位元時間相同;假如收發器具有極度非對稱的行為,RxD的顯性位元將大幅縮短,隱性位元則會延長,

|

| 圖2 TxD-to-RxD傳播延遲完美對稱的收發器 |

如此的極度非對稱,將對可能的最短位元時間和可能的最長位元時間造成限制。導致非對稱延遲的因素很多,其中包含顯性、隱性位元的時間長度、收發器本身的溫度及微控制器和收發器的介面等。

顯/隱性位元時間長度

為了將CAN FD應用的收發器效能最佳化,因此須指定傳播延遲對稱(圖3)。從分析市場上多款CAN收發器便能發現,連續顯性位元數量會對收發器行為造成影響,為了將此發現涵蓋在規格中,指定連續五個顯性位元之後的隱性位元的位元時間遂有其必要。

|

| 圖3 CAN FD收發器的傳播延遲規格 |

正常來說,較低的位元率不會影響此效能,此規格也能用在較低的位元率。目前討論兩種不同的資料階段位元率:用於複雜網路通訊的2Mbit/s及點對點通訊的5Mbit/s。位元率越高,需要的準確度也越高,這就是2Mbit/s和5Mbit/s可以適用不同限值的原因。為了用同一種收發器涵蓋此規格,須要調整溫度範圍和5伏特(V)供電(VCC)的範圍,如表1。

|

| 表1 TxD-to-RxD傳播延遲對稱的新規格 |

此參數中的資訊顯示,所有較低位元率的隱性位元將縮短至不超過100奈秒,而且也能延長至不超過50奈秒,接著可以將這些數值用在網路設計和仲裁階段的取樣點計算。

CAN匯流排網路

另一個發生非對稱延遲的原因,則是匯流排網路本身的實際行為。CAN收發器具有開漏輸出階段(圖1),且不具如FlexRay收發器的推挽式功率級,這類的開漏概念允許控制隱性到顯性的轉換速率,以將排放最佳化,並允許只從匯流排控制顯性位準。

|

| 圖4 不同電容負載對顯性位元時間的影響 |

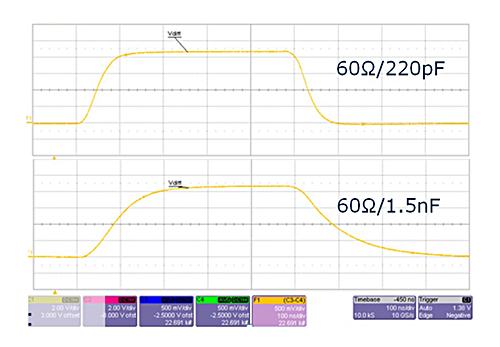

至於顯性到隱性的轉移,最大轉換速率則由輸出階段控制,但最小轉移速率則由匯流排控制。在由大量節點和/或額外的外部ESD或EMC元件導致高電容負載的情況下,可提高顯性到隱性轉移時間,以縮短隱性位元的位元時間,如圖4顯示兩種不同電容負載的影響,上方顯示電容負載220pF的匯流排差動電壓行為,下方則顯示電容負載1.5nF的相同曲線,兩邊都有較低的轉換速率,但顯性位元經過延長。顯性位元時間的長度取決於接收器的臨界值位準,如圖5所示。

|

| 圖5 標示出最大和最小接收器閾值位準 |

具有高臨界值(900毫伏特)的接收器跟具有最小可能臨界值的接收器一樣,可偵測較小的顯性位元時間。

溫度

傳播延遲非對稱的另一項原因為溫度。視技術和驅動器概念而定,溫度係數可能為正值或負值。

顯性差動電壓位準

非對稱變動的原因還有顯性差動電壓(VCAN_H-VCAN_L)的位準,如果顯性電壓位準較高,例如接近最高位準的3伏特,關閉時間就會延長,直到差動電壓位準低於最小接收器臨界值位準的500毫伏特。

顯性差動電壓位準取決於三項因素。

假如位元率較高,VCC範圍和溫度範圍就會縮小,讓較高的位元率也能達到穩定的通訊。

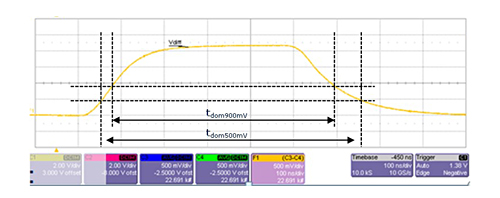

表1的資料顯示,實體層隱性到顯性與顯性到隱性的迴路延遲不同,例如2Mbit/s時的差異可能介於+50∼-100奈秒,若要從接收節點計算預期的位元時間,則需要有收發器和接收器的資訊,針對這項需求,更新後的ISO 11898-2提供了發送器延遲對稱的資訊(圖6)。

|

| 圖6 發射器和接收器延遲對稱的說明 |

在收發器的TxD接腳傳送連續五個顯性位元,接著傳送開啟隱性位元。在CANH和CANL匯流排輸出接腳上,差動電壓的觸發位準(VCANH-VCANL)在顯性到隱性邊緣定義為500毫伏特,在隱性到顯性邊緣定義為900毫伏特(圖7)。接收器和發送器延遲對稱的總和,可用於計算最小的可能位元長度。

|

| 圖7 發射器傳播延遲對稱的定義 |

微控制器/收發器間的介面

微控制器和收發器之間的介面也可能是導致非對稱延遲的原因。微控制器TxD輸出驅動器的轉換速率對稱,及收發器RxD輸出驅動器的轉換速率對稱,也會影響對稱。

電路板上的電容負載,還有收發器TxD輸入或微控制器RxD輸入的電容輸入負載,皆可修改對稱。收發器TxD輸入緩衝區的輸入概念,如互補式金屬氧化物半導體(CMOS)位準輸入或電晶體邏輯(TTL)位準輸入臨界值,可能導致額外的對稱,如果輸出驅動器的轉換速率完全相符,CMOS位準輸入影響對稱的程度就較低。因為非對稱是由驅動器的對稱效能決定,如果收發器TxD輸入具有TTL輸入位準,這些臨界值會增加由臨界值建立的額外非對稱。

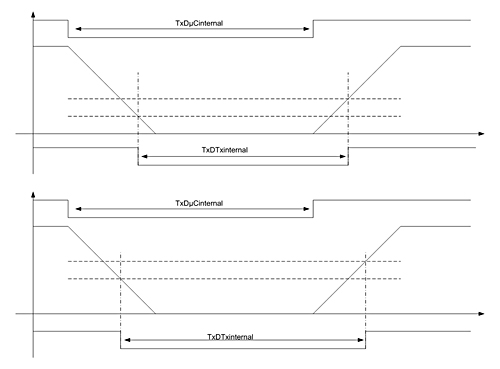

圖8顯示的範例具有非常低的輸入臨界值和非常小的磁滯。驅動器的轉換速率為極度對稱,但TTL輸入階段會將顯性位元時間縮短,這樣的非對稱會延長隱性位元,因而有所幫助,但匯流排通常會縮短隱性位元時間,在兩端皆有終端的點對點網路中,位元率也會受到限制。

|

| 圖8 TTL與CMOS收發器TxD輸入概念的比較 |

圖9顯示非對稱訊號對收發器TxD輸入的影響。尤其在高電容負載下,非對稱訊號也會修改隱性和顯性位元的位元時間,因此接收器和微控制器輸出驅動器在高電容負載下尤其必須對稱。

|

| 圖9 收發器內部位元時間的影響取決於轉換速率 |

在電氣隔離應用中,有光耦合器作為微控制器和收發器之間介面的情況下,必須將光耦合器

的傳播延遲納入考量。光耦合器具有開漏輸出階段,高至低邊緣(隱性到顯性)是由輸出電晶體驅動,顯性到隱性邊緣則取決於外部RC電路。

振鈴因素

另一個非對稱的原因,就是隱性到顯性轉移的振鈴。值得注意的是,這是不受控制的轉移,未終止的線路和星狀拓撲是此轉移發生振鈴的原因,而且振鈴還會額外縮短隱性位元,不過隱性到顯性轉移較不重要,因為收發器會以輸出階段控制轉移。如果發生振鈴,強力的輸出階段便會加以抑制。

實體層對稱的重要性在於實體層非對稱會減少取樣點的可能範圍,如果我們檢視最新可能的取樣點時間,則必須檢查兩種不同的狀況。第一種狀況為要再次同步的兩個隱性到顯性邊緣的最大可能距離,此時間為十個位元時間。若要計算最新的可能取樣點,必須考量:

第二種狀況為五個位元的情況,並連續傳送最多數量的顯性位元。在此情況下,必須考量上述要點及收發器對稱(2Mbit/s為50奈秒,5Mbit/s為20奈秒),要找出最早的可能取樣時間,五個顯性位元之後的隱性位元是最重要的。此時,除了其他要點,還必須考慮收發器非對稱(2Mbit/s的100奈秒或5Mbit/s的80奈秒)、網路振鈴和匯流排負載。

若要在高位元率(2Mbit/s以上)運作的CAN FD網路中成功且穩定通訊,應使用特殊的CAN FD收發器及短截線的線性網路拓撲,以及電容匯流排負載引擎控制零件(ECU),另外,工程師還需要對取樣點進行密集分析,收發器的新參數對典型CAN網路和CAN FD網路都有所幫助。

對於典型的CAN網路,這些參數有助於讓取樣點的計算變得更簡單或更可靠,而不須親自試用或預估任何數值,這些數值會在日後的資料表中提供。目前,ISO 11898-2標準仍持續更新中(亦即對稱檢閱),其中-2/-5和-6等部分將在ISO11898-2統合為一部分,並將加入新參數。

(本文作者任職於英飛凌)