在通訊系統設計上所會面臨的挑戰中,有一項就是以足夠的保真度成功的擷取訊號。為了要避免阻斷物(Blockers)、訊號失真和敏感度降級所造成的影響,蜂巢式基地台通訊系統必須符合蜂巢式標準的嚴格需求,例如分碼多重存取(CDMA)與寬頻分碼多重存取(WCDMA)等,並具有高動態範圍、高輸入線性度和低雜訊。

在以往,現實的問題讓完整差動訊號鏈性能的優點比不上單端選項,但是近來在整合型射頻(RF)電路技術上的進步及具有高性能的差動RF建構區塊之下,讓差動架構得以應用在高性能接收器的設計中。本文將討論3G與4G無線應用環境下的差動訊號鏈性能和優點。

剖析接收器訊號鏈運作

|

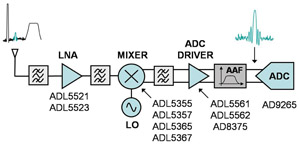

| 圖1 接收器正在朝向採用更多差動元件而演化,這股趨勢原本是從ADC開始,但已經逐漸地轉移至訊號鏈方面。在整合型RF電路技術方面的進步以及差動RF建構區塊的擴充,使得差動架構可以應用在高性能接收器的設計中。 |

圖1所示為傳統的超外差(Superheterodyne)接收器,此圖將有助於展現差動訊號鏈相對於單端訊號鏈的優點。不管其拓撲如何,其目的是將所需要的訊號成功地傳送至類比數位轉換器(ADC)中,以便進行數位化。訊號路徑是由天線、濾波器、低雜訊放大器(LNA)、混頻器、ADC驅動放大器和ADC等數個RF建構組件所構成。

位於天線之後的第一個區塊是LNA,會將熱雜訊上的訊號加以放大。位於此級的雜訊至為重要,因為它將會決定系統的敏感度和放大率,以便確保後續的混頻器與放大器不會加入顯著的雜訊。接著,帶通濾波器會抑制頻外訊號以及降低失真度與其他級所加入的雜訊。

緊接在LNA之後,混頻器頻率會將所需要的訊號加以轉譯,將高頻率RF訊號降轉換至較低且更易於管理的中頻(IF)。ADC驅動放大器和抗鋸齒濾波器(AAF)會將訊號準備進行數位化。此外,驅動器提供增益,而AAF會抑制落於第一耐奎斯特區域之外的訊號,其中也包括雜訊及會傳送至ADC的頻外寄生訊號。在類比訊號路徑的終點,ADC會將基頻資訊數位化。

理想狀態下,只有所需的訊號(圖1中左側以虛線顯示部分)會被傳送至數位領域。要處理這些所需的訊號(有可能很微弱)必須要有強固的系統,同時阻斷干擾訊號(有可能比較大)。若想設計出一組強固的系統,高敏感度、輸入線性度、選擇性及抗雜訊干擾性都是必要的。性能規格會依據應用領域和架構而有所改變,但在大部分的通訊系統中,共通的考量如失真度、雜訊層與動態範圍等,則是普遍存在的。輸入第三階截距(IP3)和1dB壓縮點(P1dB)必須要高。其他的考量還包括低成本、低電力與小尺寸等。

不易受雜訊干擾 差動優勢明顯

圖2將單端訊號與差動訊號之間的基礎以對照的方式顯現。使用的是通用的增益建構區塊,但是將相同的概念套用至混頻器和訊號鏈中的其他元件。

|

| 圖2 差動訊號所具有的消除優點提供了抗雜訊與抗干擾的能力,同時也提供偶次階諧波的消除效果。當單端與差動訊號兩者相互比較時,記得維持系統位準的性能指標以產生出良好的總體接收器設計是很重要的。 |

單端訊號--依據定義就是不平衡的,是藉由所需訊號和恆定參考點之間的差異而測得的。參考點(通常為接地)是作為訊號的回返路徑。假如錯誤的源極被導入訊號路徑中就會遇到一項難題。因為接地參考不會被注入的錯誤所影響,因此錯誤會透過訊號而繼續往前傳送。任何被導入單端組態設定的訊號變異,如果不使用極度複雜的消除技術都很難以移除。因此單端訊號會更易於受到雜訊和電磁耦合干擾的影響。

另一方面,差動訊號則是由一組取得平衡的訊號,以相等但是相反的振幅沿參考點移動所組成。正與負平衡訊號兩者之間的差異與合成的差動訊號相互對應。假如錯誤被導入差動系統路徑中,它將會被等量地加入至兩組平衡訊號內。由於回返路徑並不是對照參考點,因此錯誤將會在差動訊號中被消除掉。所以,差動訊號鏈比較不易受到雜訊與干擾的影響。這種先天具有的錯誤消除功能也提供了較佳的共模拒斥比(CMRR)和電源供應拒斥比(PSSR)。

差動訊號鏈相對於單端鏈還有另一項優點,就是在同樣的電源供應下,合成訊號擺幅可以達到單端擺幅的兩倍,這可以提高訊號對雜訊比值。或者,放大器的餘裕也能夠在同樣的電源供應下提高,進而降低失真度;或是能夠使用較低電源供應電壓提供相同的訊號擺幅,藉以減少電源的耗損。

圖2中也將差動系統中偶次級諧波先天具有的消除功能強調出來。非線性元件(在此案例中為一組單端與差動放大器)可以藉由給予正弦曲線輸入的冪級數(Power-series)擴充傳送函數來加以表示。在單端方案中,每個頻率(為輸出的倍數)會與一組常數相互關聯,偶次級與奇次級皆是。在差動組件中,偶次級非線性度會在合成輸出響應中被消除。真實的元件無法實現完美的消除功能,但是它們會因為較低的偶次級諧波而獲益良多。

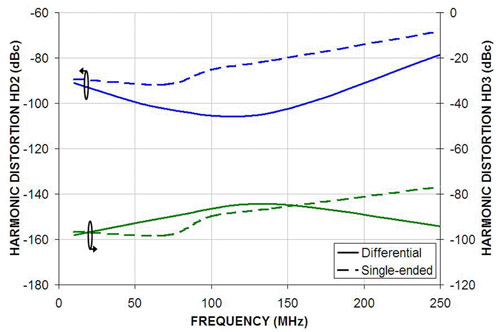

圖3所示為針對用以驅動高速的8~16位元ADC而最佳化超低失真低雜訊差動放大器的諧波失真。圖中顯示出當元件針對單端與差動拓撲設定組態時的第二與第三階諧波。雖然在單端模式下的失真度非常低(在100MHz下具有82dBc的HD2值),但是差動作業下的偶次級性能更佳(在相同頻率下具有少於100dBc的HD2值)。穿過了訊號鏈,對於在相同供應軌上的差動拓撲,於P1dB以及IP3應該可以獲得大約6分貝的改善。

|

| 圖3 雖然在單端模式下的失真度性能非常的低,但是在以差動作業下的偶次級性能上仍然有著很明顯的優勢。在輸出1分貝(dB)壓縮點與IP3上,對於具有相同供應軌的差動拓撲來說,可以預期大約會有6分貝的改善。 |

整合單端RF輸入/差動IF輸出

隨著接收器的演進,藉以提供較高性能位準差動元件的使用也日益增加。其演變是從ADC開始,並逐漸地轉回至訊號鏈。

以往,由於訊號應用領域方面的問題以及有限的差動RF建構區塊,因而形成單端或部分的差動訊號鏈。在部分訊號鏈的範例中,有一種是省略差動ADC驅動器,取而代之的是使用單端元件和變壓器來驅動ADC。雖然這種方法提供了一個簡單的解決方案,但是在性能的需求上卻反而倒退。單端驅動放大器除了會消耗更多電力外,也往往具有較差的偶次級失真、CMR及PSR。

如圖1中所示,常用於接收器的架構具有一組單端RF輸入和一組差動輸出。介於單端與差動作業之間的分隔線似乎已經被安排在混頻器上,以及被當作單端元件,譬如LNA之類的RF零件。大部分的SAW濾波器和混頻器核心原本屬於差動電路,但是為了應用上的目的而轉換為單端。

|

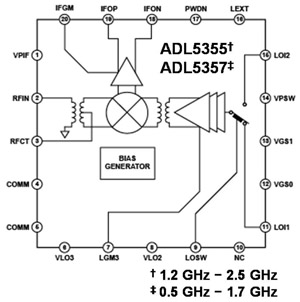

| 圖4 最近在整合式RF電路技術方面的進步,已經使具備單端RF輸入至差動IF輸出易於使用的混頻器得以實現。在以相對較容易的方式連結至外在真實環境時,差動的優點可以被運用到三組內部的混頻器埠上。 |

多年來,雙重平衡混頻器拓撲由於其具有高線性度,已經被使用於蜂巢式應用領域中。然而不幸的是,用來將訊號耦合至混合核心的傳統變壓器網路會占用大量的電路板空間,以及為設計增加顯著的成本。較新的RF元件如ADL 535x混頻器家族,將平衡/不平衡轉換器(Balun)及變壓器加以整合,提供了具備單端RF輸入與差動IF輸出之易於使用的RF建構組件。

圖4中顯示的三組混頻器埠都是內部完全差動。為了易於使用,RF和LO埠利用變壓器連結至外部環境,藉以實現單端介面。相對之下,包含了具有200歐姆(Ω)輸出阻抗之驅動放大器的IF輸出埠則是保持差動,使得與差動SAW濾波器的連結能夠更為容易。LO與RF平衡/不平衡轉換器的整合會限制混頻器的運作頻率,因而需要一整組能夠適用於橫跨蜂巢式基地台頻率範圍運作的元件。

(本文作者任職於ADI公司RF事業群)